# Ultra-low power electronics for energy harvesting node

by

Aleksandar Žujović

BSc. University of Belgrade - School of Electrical Engineering (2014)

Submitted to the Department of Micro- and Nanosystem Technology in partial fulfillment of the requirements for the degree of

Master of Science in Smart Systems Integration

at the

UNIVERSITY OF SOUTH-EAST NORWAY

July 2016

Certified by .....

Mehdi Azadmehr Associate Professor Thesis Supervisor

## Ultra-low power electronics for energy harvesting node

by

Aleksandar Žujović

Submitted to the Department of Micro- and Nanosystem Technology on July 01, 2016, in partial fulfillment of the requirements for the degree of Master of Science in Smart Systems Integration

## Abstract

Apart from providing detailed insight about the energy harvesting system as a whole, this work tackles the challenges of efficient control of the interface circuit of an electrostatic vibration energy harvester, with severely limited power consumption allowance for the controlling electronics. Used interface circuit consists of double charge-pump topology, comprising a storage element (pre-charged reservoir capacitance), dual antiphase variable capacitance and an intermediate storage element, with an inductive flyback return path. Since high voltages are expected in the long term operation, switch component of the interface circuit is realized as a high-voltage PMOS device from AMSH35 process by AMS.

Concerning the interface circuit, theoretical analysis was introduced, to demonstrate the requirement for precise synchronization of the switch with the circuit voltage levels, with the purpose of optimizing the harvested energy. Previous work was addressed, and this work was built upon it. For decreasing the power consumption of the critical component, a low power clock-signal generator was designed, with power consumption of approximately 0.35nW, and accompanying stable current reference with constant power consumption of 0.57nW, and 4.7%/V current deviation caused by variations in the supply voltage.

Additionally, issues accompanying the long term operation, and thus increase in the pre-charge voltage, were discussed in details, and subject of interest for further research and promising possible improvements were suggested.

Thesis Supervisor: Mehdi Azadmehr Title: Associate Professor

# Acknowledgments

I would like to express my most sincere gratefulness to Assoc. Prof. Mehdi Azadmehr for his relentless guidance and support during the work on this project, and constructive criticism during the thesis writing.

Additionally, I would like to acknowledge and express my thankfulness to the *SSI* Consortium, for creating this course programme and providing me with the opportunity to take part in it. It has been my honor and pleasure to participate in this programme for two years.

Finally I would like to express my deepest and eternal gratitude to my parents, who have effortlessly provided me with their never-ending love and enthusiastic support, and without whom I would not be the person that I am today.

# Contents

| A        | ckno                                                              | wledgn | nents                                                                         | $\mathbf{v}$ |  |  |  |

|----------|-------------------------------------------------------------------|--------|-------------------------------------------------------------------------------|--------------|--|--|--|

| 1        | Inti                                                              | oducti | ion                                                                           | 1            |  |  |  |

|          | 1.1                                                               | Motiv  | ation                                                                         | 1            |  |  |  |

|          | 1.2                                                               | Conce  | pt of energy harvesting                                                       | 2            |  |  |  |

|          | 1.3                                                               |        | ent energy sources and applications                                           | 2            |  |  |  |

|          | 1.4                                                               |        | ess Sensor Nodes                                                              | 4            |  |  |  |

|          | 1.5                                                               |        | tion energy harvesting                                                        | 5            |  |  |  |

|          |                                                                   | 1.5.1  | Generalized system                                                            | 5            |  |  |  |

|          |                                                                   | 1.5.2  | Mechanical structure working principle                                        | 6            |  |  |  |

|          |                                                                   | 1.5.3  | Electro-mechanical energy conversion                                          | 8            |  |  |  |

|          | 1.6                                                               | Circui | t for power management                                                        | 12           |  |  |  |

|          | 1.7                                                               | Thesis | s scope and limitations                                                       | 14           |  |  |  |

|          | 1.8                                                               | Thesis | s Outline                                                                     | 14           |  |  |  |

| <b>2</b> | Study of the Electrostatic Vibration Energy Harvesting System . 1 |        |                                                                               |              |  |  |  |

|          | 2.1                                                               | Electr | ostatic Transducer                                                            | 15           |  |  |  |

|          |                                                                   | 2.1.1  | Out of plane capacitor with gap closing                                       | 17           |  |  |  |

|          |                                                                   | 2.1.2  | In-plane capacitor with variable overlap surface                              | 17           |  |  |  |

|          |                                                                   | 2.1.3  | In-plane comb capacitor with variable overlap $\ldots \ldots \ldots$          | 18           |  |  |  |

|          |                                                                   | 2.1.4  | In-plane comb capacitor with gap closing                                      | 19           |  |  |  |

|          |                                                                   | 2.1.5  | In plane capacitor with variable patterned surface $\ldots$ $\ldots$ $\ldots$ | 20           |  |  |  |

|          |                                                                   | 2.1.6  | Summary                                                                       | 21           |  |  |  |

|          |                                                                   | 2.1.7  | Discussion                                                                    | 21           |  |  |  |

|          | 2.2                                                               | Power  | management circuit topologies                                                 | 22           |  |  |  |

|          |                                                                   | 2.2.1  | Primitive (continuous) topologies                                             | 22           |  |  |  |

|          |                                                                   | 2.2.2  | Charge Constrained Topology                                                   | 23           |  |  |  |

|          |                                                                   | 2.2.3  | Voltage Constrained Topology                                                  | 26           |  |  |  |

|          |                                                                   | 2.2.4  | Charge pump topologies                                                        | 27           |  |  |  |

|    | 2.3   | Summary and Discussion                                     | 2 |

|----|-------|------------------------------------------------------------|---|

| 3  | Inte  | rface circuit and flyback switch control circuit design 33 | 3 |

|    | 3.1   | Software tools                                             | 3 |

|    | 3.2   | Process technology                                         | 3 |

|    | 3.3   | Transducer model                                           | 4 |

|    | 3.4   | Interface circuit topology                                 | 7 |

|    | 3.5   | Previous Work                                              | 9 |

|    |       | 3.5.1 Return path circuit                                  | 9 |

|    |       | 3.5.2 Voltage level shifter                                | 0 |

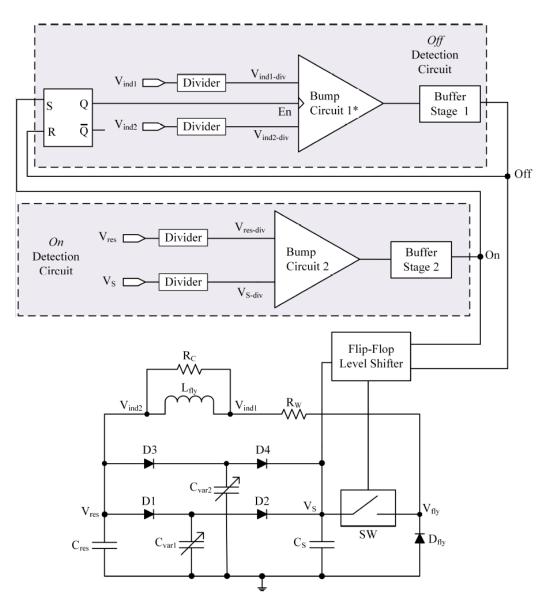

|    |       | 3.5.3 Synchronous switch control circuit                   | 1 |

|    | 3.6   | Self-sustaining topology considerations                    | 8 |

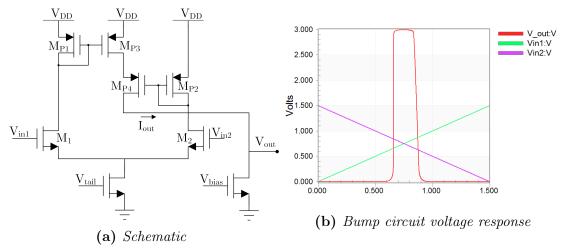

|    |       | 3.6.1 Bump-circuit clocking                                | 8 |

|    |       | 3.6.2 Low-power clock signal generator - literature review | 0 |

|    | 3.7   | CMOS Relaxation oscillator                                 | 1 |

|    | 3.8   | Current Reference                                          | 3 |

|    |       | 3.8.1 Design methodology                                   | 5 |

|    | 3.9   | Considerations for mid-term operation                      | 1 |

|    | 3.10  | Discussion                                                 | 2 |

|    |       | 3.10.1 Voltage regulator                                   | 5 |

|    |       | 3.10.2 Power consumption considerations                    | 7 |

| 4  | Con   | clusions, improvements and future work                     | 9 |

| -  | 4.1   | Chapter summaries                                          | - |

|    | 4.2   | Improvements and future work   7                           | - |

| Re | efere | nces $\ldots$ $\ldots$ $\ldots$ $.$ 78                     | 8 |

# Chapter 1

# Introduction

## 1.1 Motivation

Ambient energy is present in many forms in our surroundings, including solar (light) energy, thermal energy, wind energy, mechanical energy, electromagnetic or radiation energy, energy from chemical reactions and many others. Mankind has utilized this ambient, or environmental energy, throughout history to facilitate and improve their daily lives, which can be seen in the appearance of waterwheels and windmills that date back hundreds of years, or hydroelectric power plants, solar panels in the last century. Considering this, it is obvious that the concept of energy harvesting is anything but new.

In the more recent years, energy harvesting is placed in another context, meaning the utilization of harvested energy as a power supply for miniaturized electronic devices, such as wireless sensor nodes, wearable electronics or RFID tags and such. These devices are designed to be very power efficient, with maximum power consumption up to miliwatts, depending on the energy harvesting capability). However, they impose strong requirements for reliability w.r.t. power supply variation and size, depending on application. For microscale electronic devices which rely on energy harvesting for power supply, energy sources of practical interest are electromagnetic (such as those in RFID), mechanical vibrations and thermal gradients. Although these sources have certain efficiency limitations, they are practically unlimited if they are present at the device working location [1].

This chapter will briefly introduce the reader to the main idea, problems and challenges of microscale energy harvesting, outline different sources, applications of use and various conversion principles, i.e. types of transducers that are used in stateof-the-art energy harvesting systems.

# 1.2 Concept of energy harvesting

Energy harvesting (also known as energy scavenging or power harvesting) is essentially the process of collecting and converting the energy from an external environmental source, or sources, and utilizing that energy to supply power to a device or accumulating and storing them for later use [2]. An efficient energy harvesting system must properly convert, condition and manage harvested energy and make it available in appropriate form to its electrical load, i.e. the device itself, whether it is a sensor, a passive RFID tag or a battery that is being charged.

# **1.3** Ambient energy sources and applications

As mentioned before, there are many external energy sources available in the environment, which gives one method for classification of energy harvesting systems. A compact way of classifying the energy sources is with respect to their nature:

- Mechanical sources: such as mechanical vibrations and mechanical stressstrain,

- Thermal sources: waste energy from furnaces or machines, or friction sources,

- Radiation sources: includes sunlight or light-sources, ambient RF waves or infrared waves,

- Natural energy: from water flow, wind etc.,

- Biochemical sources: includes sources based on chemical reactions.

Energy from these sources is utilized for various applications ranging from megawatt to nano-watt scale, which can be summarized as:

- Mega-watt range: Power supply for domestic (household) and industrial use. Commonly used sources are hydraulic flow and potential energy [3], wind energy [4] and solar energy [5].

- Mili/micro-watt range: low power applications such as vibration powered wrist watches [6], solar powered calculators [7], micromachined thermopiles for harvesting on human bodies [8], shoe-mounted piezoelectric generator [9], electrostatic and electromagnetic generators [10] etc.

- Nano-watt range: electrostatic harvesters with limited variation range, piezoelectric nanowires, nanosensor noise harvesters [11], carbon nanotubes [12] etc.

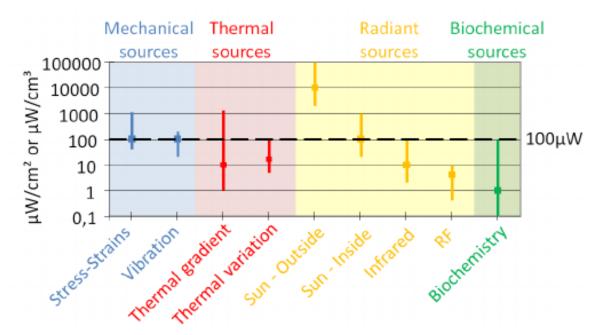

For electronic devices and wireless sensor nodes mili-nano watt range is of a particular interest. For this purpose we consider some sources to be more appropriate and pay more attention to them. Figure 1-1 illustrates power densities for different ambient energy sources.

Figure 1-1: Power densities available from different ambient energy sources [13]

As seen Figure 1-1, highest available power density is available from direct sunlight. Although solar energy harvesters are frequently used in a wide range of power levels and scale sizes, two major limitations prevent solar energy from being the most popular and attractive source of ambient energy. Namely, the cost of manufacturing for high power and large scale generators reduce its availability for commercial use, and on the other side low light availability for small scale devices reduces the efficiency of such harvesting systems [14, 15]. Some devices harvest thermal energy in form of thermal gradients [16], but normally a high temperature gradient, or temperature variation is required to achieve effective harvesting which limits the scope of application, especially in micro-scale devices, where it is hard to find temperature differences greater than approx. 10°C. Mechanical vibrations are present in various environments that require monitoring, i.e. sensors and sensor networks, such as factories, bridges, cars etc. This makes vibration energy harvesting more and more attractive for wireless sensors applications, such as ones presented in [17, 18].

# 1.4 Wireless Sensor Nodes

There is an increasing number of applications for which servicing and maintenance of devices, such as battery replacement or data collection, is difficult or inconvenient due to inaccessibility. Such applications include, but are not limited to, various sensors for monitoring temperature, humidity and/or pressure in rain forests, monitoring state of industrial machines such as motors, pumps and turbines, or perhaps implantable devices for vital functions monitoring and many others. Ideal devices would be accessible remotely, and self-sustaining, meaning that they would function properly only from harvested energy over a long period of time. Data collection can be done wireless, to eliminate the need for data wires or necessity of physical access for collection of data. Other challenge is for the system to be self-powered from the environment energy, which poses a big challenge, since environmental energy is unpredictable and might not be available at all times. This imposes the necessity of a power storage element, so the harvested energy can be stored for further use. Recent technology advancement, especially in microelectronic technology allows design and production of very low-power devices that would efficiently consume the limited harvested energy.

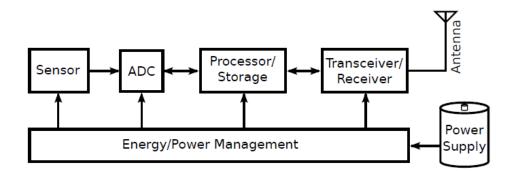

Typical topology of a WSN (*Wireless Sensor Node*) is shown in Figure 1-2 [19] in the form of a block diagram.

Figure 1-2: Typical WSN architecture [20]

Power consumption of such a system is typically dominated by communication and sensing operations, but these occur very infrequently due to the slow changing nature of environmental variables such as air pressure or temperature. Consequently, processing, sensing and communication units can be idle, and consume no to very little power, while the harvesting cycle replenishes the power supply.

# 1.5 Vibration energy harvesting

Energy harvesting from mechanical vibrations is a relatively new concept, compared to for instance harvesting of solar energy through photovoltaic cells, or electromagnetic energy for RFID circuits. It began to take off more rapidly in 2000's with the increased research of MEMS devices.

## 1.5.1 Generalized system

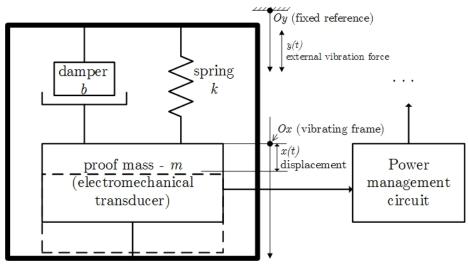

Generalized form of the vibration harvesting system is illustrated in Figure 1-3. The model for vibration micro-generator was first introduced in [21] by Yates and Williams.

Figure 1-3: General model of a VEH

As described in various studies, vibration energy harvesting can be accomplished in two steps:

- 1. Mechanical energy is "captured" by a mechanical part of the system, modeled with the spring-coupled proof-mass

- 2. Accumulated kinetic energy is converted into electrical form, modeled with the damping element

The transducer is usually a mechanical resonator, consisting of a proof-mass which is suspended from the frame via an elastic structure, i.e. a spring. In this domain, there are two references, the global reference frame Oy, in which vibrations take place (y(t)), and the reference Ox related to the oscillating system in which the proof-mass is located, and with respect to which the displacement of the proof mass is measured (x(t)). According to Landau [22], if the external vibrations are represented as y(t), then the overall acceleration of the inertial system is  $a_{ext}(t) = \ddot{y}(t)$ , and the relative motion of the referent system Ox can be modeled by applying force to the proof-mass totaling to  $f(t) = -m \times a_{ext}(t) = -m \times \ddot{y}(t)$ , where m is the mass of the proof-mass. Additionally, the proof-mass is elastically coupled with the frame Ox via spring, and the mass accumulates kinetic energy due to movement in the referent system.

The conversion of the collected kinetic energy to electrical energy is modeled with the damping element, which means that ideally, the dominant damping force acting on the suspended proof-mass should be of electrical origin. In other words, it should perform negative work w.r.t. mechanical vibration, intentionally decreasing the kinetic energy of the system. This damping force can be induced by a electric field, magnetic field or a mechanical strain in piezo-electric material, depending on the type of the electro-mechanical transducer that is used. Each of the transducer types has its own characteristics, i.e. benefits and drawbacks, and consequently is used in the most suitable application scenario. Additionally, the type of transducer specifies the characteristics of the power management circuit in order to achieve a functioning energy harvester, in terms of energy accumulation and power supply to the load, e.g. sensor or transceiver.

To summarize, design procedure for a vibration energy harvester include design and optimization of : a) mechanical structure, in order to maximize the amount of "captured" kinetic energy; b) transducer, in order to maximize the conversion efficiency; and c) power management electronic circuit, to accumulate, store and distribute harvested energy as efficiently as possible while consuming very low amount of power itself [19].

### 1.5.2 Mechanical structure working principle

Mechanical structure, modeled as a suspended mass-spring-dashpot system, can be one of two types: 1) non-resonant, which is typically used in applications where the amplitude of vibrations is large enough w.r.t. maximum allowed mass displacement and the vibration power is spread over a wider spectrum of low frequencies; 2) resonant, typically used in applications where the amplitude is relatively small compared to feasible mass displacement and designed to target a specific narrow band of frequencies.

Considering a given resonant mechanical structure, the maximum mass displace-

ment is given when the external vibration frequency equals the structure's resonant frequency, and the displacement drastically lowers with even the slightest deviation from the structure's resonant frequency. This is a major challenge for the designers, since the ambient vibrations can be, and usually are inconsistent or variable, and with the linear resonators having very narrow and selective frequency bands, there is a possibility that it will not perform in real conditions, which renders it unusable for any real-life application.

The efforts to overcome these challenges take form of widening the response bandwidth of the mechanical resonator structures, involving the utilization of non-linear mechanical properties to create more complex coupling between the mass and the referent frame. Such works exist in different forms, including resonators with non-linear springs [23, 24], bi-stable springs [25] or non-linear springs with two mass elements [26]. These approaches contribute to the increase in efficiency by allowing a "conversion" of frequency, i.e. a resonator made for low frequency, with a low quality factor is used as excitation of a resonator designed for high frequency and has a high quality factor, which is used as the transducer.

According to [27], maximum obtainable power by a mechanical resonator structure can be described with simple equation:

$$P_{max} = \frac{1}{2} X_{max} m \omega A_{ext} \tag{1.1}$$

where  $X_{max}$  is the maximum proof-mass displacement, m is the mass,  $\omega$  is the angular frequency and  $A_{ext}$  is the amplitude of the external vibrations. This expression relates solely to the mechanical structure and is not related to the transducer or its electro-mechanical efficiency, but simply represents the maximum power that the the resonating structure can collect from the vibrations. Based on the literature review of some existing harvester designs, Table 1.1 presents a brief comparison, and the evolution of micro-mechanical resonating structures, and their absolute power limit according to (1.1).

Table 1.1: Overview of several micro-scale resonator designs concerning their maximum achievable power

| Design                 | Year | $X_{max}$ [µm] | <i>m</i> [g] | f [Hz] | $A_{ext} \ [m/s^2]$ | $P_{max}$ [ $\mu W$ ] |

|------------------------|------|----------------|--------------|--------|---------------------|-----------------------|

| Roundy et. al. [28]    | 2003 | 250            | 0.1          | 50     | 1                   | 3.93                  |

| Despesse et. al. [29]  | 2005 | 95             | 2            | 50     | 1                   | 2.98                  |

| Paracha et. al. [30]   | 2009 | 50             | 0.066        | 250    | 1                   | 2.59                  |

| Guillemet et. al. [31] | 2013 | 46             | 0.046        | 163    | 1                   | 1.08                  |

Maximum achievable power in the mechanical resonator reflects the amount of kinetic energy the structure can collect from the external vibrations, which is supported by the results presented in Table 1.1, seeing as the structures fabricated with older technologies are larger and are allowed higher maximum displacement, they have the potential of achieving more power for the same amplitude of external vibrations. However the efficiency of electro-mechanical conversion and power management circuits are much higher, and so is the overall harvesting efficiency, which will be illustrated in following sections.

The design of the mechanical structure is out of the scope of this thesis. However, the author recognizes the importance of understanding the working principle and the connection it bears to the rest of the harvester system, and therefore considers that a brief, but not in-depth, explanation is appropriate.

#### 1.5.3 Electro-mechanical energy conversion

As explained earlier, electro-mechanical transducer is the element which converts harvested mechanical energy into electrical energy, and as such it is the second major design point in the process of vibration energy harvester design, which contributes greatly to the overall harvester efficiency, and also determines the architecture of the power management electronic circuit. On a macro scale, electrical power generation is dominantly based on electromagnetic transducers, e.g. windmills, hydroelectric power plants etc. Electrostatic and piezoelectric transduction is highly impractical and inefficient on a macro scale, but well suited and effective when it comes to micro-scale devices. Thus, for the purpose of micro-scale harvesting systems, three basic methods are recognized and used for energy conversion: 1) electromagnetic; 2) piezoelectric; and 3) electrostatic energy conversion. Consequently, we recognize three types of transducers for each of the methods.

#### **Electromagnetic transducers**

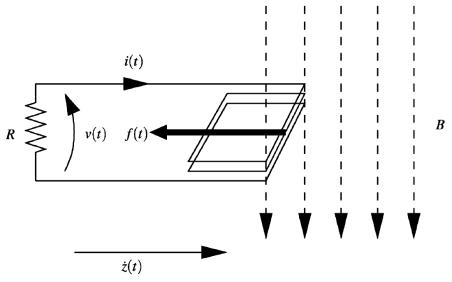

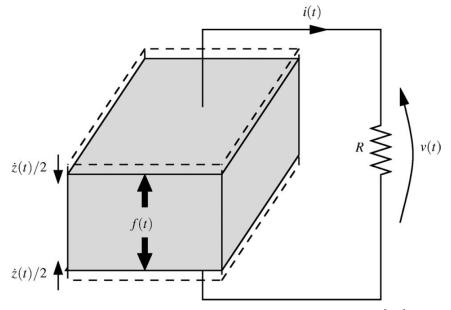

The main principle of electromagnetic energy conversion is based the Faraday's law of induction, which is illustrated in Figure 1-4). The change of magnetic flux  $\Phi$ , through a coil with N windings, induces a voltage:

$$v(t) = -Nd\Phi/dt, \tag{1.2}$$

forcing a current i(t) through a closed circuit.  $\Phi$  is given by:

$$\Phi = \iint_{\Sigma(t)} \mathbf{B}(t) d\mathbf{A},$$

where  $d\mathbf{A}$  is an infinitesimally small element of surface area of the moving surface  $\Sigma(t)$ and **B** is the magnetic field. The total force f(t) on the charges moving through the magnetic field is opposing the relative motion (Lenz's law), i.e. it acts as a damper in the mass-spring-dashpot micro-generator system illustrated in Figure 1-3. Energy converted to heat, due to resistance, and stored in the coil, due to inductance, comes from the mechanical work done against the opposing force. There are a lot of issues

Figure 1-4: Electromagnetic transduction principle [27]

of utilizing electromagnetic transduction on a micro-scale, including the difficulty to integrate or fabricate a large number of windings on a MEMS device resulting in low output voltages, which imposes a requirement for the integration of ferromagnetic materials or permanent magnets for the flux path. Another inconvenience is that the strong damping forces require rapid flux variations, according to equation (1.2), whereas ambient vibrations are in a low frequency range.

#### **Piezorelectric transducers**

These transducers are based on a phenomenon called piezoelectric effect, whereby a material experiencing mechanical strain from applied stress exhibits induction of an electric field in that material, and vice versa, an applied electric field causes the material to experience strain [32]. Piezoelectric transducers utilize the former to act as micro-generators, in terms that some of the mechanical work done by an external force to produce strain is stored as elastic strain energy, and the rest is stored in the electric field associated with the polarization of the material [27]. Principle of operation of piezoelectric transducers is illustrated in Figure 1-5. When an external conduction path is provided the result is a current that neutralizes the net charge. Materials that exhibit piezoelectric properties with high electromechanical coupling

Figure 1-5: Piezoelectric transduction principle [27]

factors are in general ceramics (e.g. lead zirconate titanate - PZT, or aluminum nitride - AlN), and as such they do not tolerate high values of strain. They are normally used in form of thin films, spread across another material that exhibits large values of displacement, and consequently strain. Most common structure of this type of transducer is a proof-mass suspended on a cantilever with a thin film of a piezoelectric material.

#### **Electrostatic transducers**

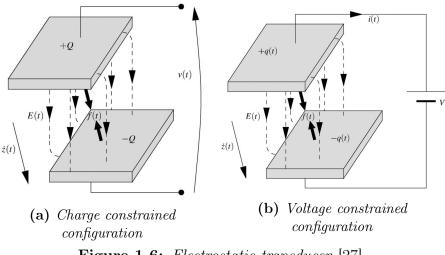

When it comes to electrostatic transducers, work done by external forces is performed against the attractive force between oppositely charged parts. Practically, this represents a variable capacitor, whose gap between the plates vary as a consequence to external vibrations [33]. Two main modes of operation are distinguished: continuous and switched. Switched mode implies reconfiguration in the transducer's surrounding circuitry at certain moments of the operation cycle, through the operation of switches [27]. They can be configured to operate in two different modes: a) charge constrained operation Figure 1-6a; and b) voltage constrained operation 1-6b.

Figure 1-6: Electrostatic transducer [27]

Charge constrained mode (Figure 1-6a) with a fixed overlap length and a variable gap between the plates (i.e. horizontal component of  $\dot{z}(t)$  is zero) operates as follows: electric field is proportional to the charge, which is constant, and energy density is independent of the gap. As the external force exerts work against attractive electrostatic force, and the gap increases, the increased volume of the electric field will store added potential energy. If, on the contrary, the plates are moved laterally, i.e. the vertical component of  $\dot{z}(t)$  is zero, mechanical work, done by external forces, is exerted against the fringing field. This causes an increase in stored energy, since the reduction in plate overlap increases electric field strength.

Voltage constrained mode is illustrated in Figure 1-6b. If the plates move vertically, with a fixed overlap, electric field strength reduces, causing the charges to move in the external conduction path, forming a current i(t). If the plates move laterally, electric field strength stays remains unchanged, but the reduction in the volume of electric field forces the current to flow through the external conduction path. In either case, exerted mechanical work is converted into added electrical potential energy in the source [27].

In both of these modes, the basic equations for the capacitor apply: charge Q = CV, and energy that is stored in the capacitor  $W_s = \frac{1}{2}CV^2$ . Electrostatic force is found to be proportional to the rate of change of the capacitance in the direction orthogonal to the plates surface:

$$F = \frac{1}{2}V^2 dC/dz \tag{1.3}$$

Having explained these two modes from physics point of view, some additional explanations from electronics point of view will be left for further sections.

One drawback of electrostatic transducers is that they require pre-charging in order to function properly. An alternative to pre-charging is the use of electret materials, which are dielectric materials with quasi-permanent electric charge or dipole polarization. Even with this drawback, electrostatic transducer have an advantage over electromagnetic and piezoelectric transducer, due to the ease of integration and compatibility with MEMS and IC fabrication processes.

#### Comparison of electromechanical transducers

Main advantages and drawbacks of these three types of transducers are summarized in Table 1.2.

|            | Electromagnetic                                                                                                                                                    | Piezoelectric                                                                                           | Electrostatic                                                                                                                                                                                |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advantages | -robustness<br>-high output currents<br>-proven long lifetime                                                                                                      | <ul><li>-no need to control<br/>gaps</li><li>-high output voltages</li><li>-high capacitances</li></ul> | -lower system costs<br>-high output voltages<br>-coupling factors easier<br>to manipulate<br>-feasible high coupling<br>factors<br>-size reduction<br>increases capacitances                 |

| Drawbacks  | -low output voltages<br>-typically expensive<br>(material)<br>-inefficient for low<br>frequencies and small<br>size devices<br>-not suitable for MEMS<br>processes | -expensive (material)<br>-coupling factor highly<br>dependent on material<br>properties                 | -low capacitances<br>-highly affected by<br>parasitics<br>-necessity for control of<br>$\mu$ m dimensions<br>-no direct electro-<br>mechanical<br>transduction without<br>electret materials |

Table 1.2: Comparison summary for different types of transducers [13]

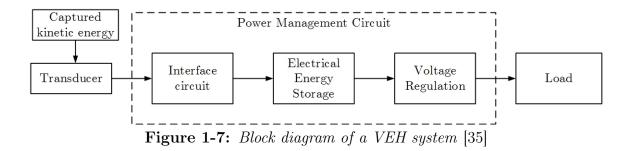

# 1.6 Circuit for power management

Power management circuit is the next major design point, since it greatly contributes to harvesting efficiency, in terms of performance in capturing, storing and redistributing the energy converted by the transducer. As mentioned before, the type of transducer determines the architecture of the circuit. Consequently, harvesters with electromagnetic transducers typically use simple topology, involving a rectifying bridge to rectify relatively low AC voltage [34]. Harvesters with piezoelectric transducers usually require rectification as well, and often voltage level conversion, i.e. regulation, since the transducer output voltage is dependent on many factors. Electrostatic harvesters, on the other hand, require control circuitry, to control charge/discharge process and to store the harvested energy efficiently.

Figure 1-7 illustrates the architecture of a vibration harvesting system, outlines the power management circuit. Interface circuit is used to properly transfer the energy converted in the transducer to the energy storage element, whereas the voltage regulator is most likely necessary to provide consistent operating conditions for the load.

Obvious requirements for the power management circuits include low power consumption and self-starting properties. For instance, basic electrostatic harvester that requires pre-charging is not self-starting, but one with an integrated electret for startup is. Aside from low power consumption, the circuit should minimize the losses between the transducer and the storage element.

A more complex property of a power management circuit is the ability to adapt, i.e. reconfigure itself based on the current requirements. For example, if the ambient energy suddenly becomes insufficient, and the harvester dissipates more power than it harvests, the harvester should be able to recognize this, and enter "sleep" mode until the ambient energy becomes sufficient again. Otherwise, the power management and load circuits might consume all the available energy in the storage element, even the one needed for start-up, rendering the harvester useless and in need of maintenance.

Since this work is based on an electrostatic energy harvester, main focus will be on the circuit topologies relevant for electrostatic energy harvesters, and some of the power management topologies will be presented in Chapter 2.

# 1.7 Thesis scope and limitations

The main goal of this work is to produce a functional design for an autonomous, self-sustaining power management circuit for a VEH system, starting with study and optimization of the work presented in [36], and adapting the topology to fit the requirements.

Most of the previous works done on the topic of electrostatic vibration energy harvesting, as shown in literature review, uses relatively high power circuits for power management, due to the availability of harvested energy. However, the mechanical structure and transducer considered in this work, greatly limit power consumption requirement for this power management circuit due to low amount of harvested energy. As shown in equation (1.3), the electrostatic force which exerts work to generate electrical energy is proportional to the rate of change of capacitance, and this work uses a comb drive capacitor with very small variations which results in low harvested power. Compared to some works, harvested power is up to three orders of magnitude lower, making this project significantly challenging, in terms of power consumption of the power management circuit itself.

Additionally, most designs utilize some external signals for proof of concept, whereas this work aims at a completely autonomous design, including clock signals, current sources etc. Aside from aiming at maximum efficiency of storing the harvested power, this work also focuses decreasing the power consumption of the power management circuit as well.

# 1.8 Thesis Outline

This chapter stated the motivation for this project and briefly introduced the reader to basic principles of energy harvesting, its purpose and applications.

Chapter 2 focuses on the study of the used harvester structure, for the purpose of specifying the requirements for the power management circuit and description of available topologies for power management circuits.

Chapter 3 explains in details the functionality and purpose of each individual block of the circuit and presents the simulation results achieved in the circuit design.

Final Chapter concludes this thesis with the summary of results and suggestions for improvement and future work.

# Chapter 2

# Study of the Electrostatic Vibration Energy Harvesting System

As mentioned in the previous chapter, this work is based on an electrostatic vibration energy harvesting system, since electrostatic transducers are more convenient in a number of ways, including the miniaturization and integration compatibility with MEMS processes. This chapter will focus more on the details of the electrostatic vibration energy harvesting system, highlighting the power management circuit different topologies.

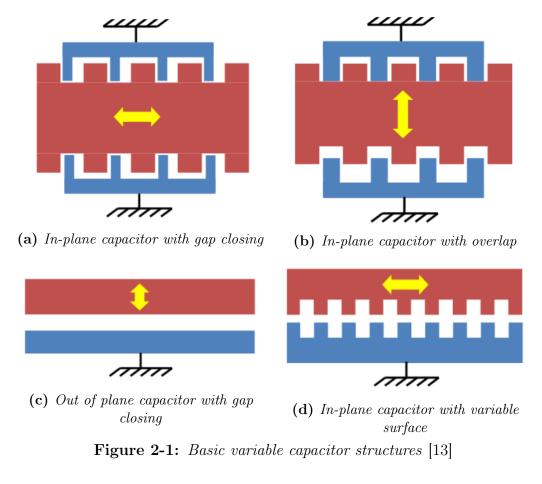

# 2.1 Electrostatic Transducer

Electrostatic harvesting systems are based on variable capacitors, i.e. the moving mechanical part is usually one of the electrodes of the capacitor, which achieves the variation in the capacitance. Based on the movement type, in the previous chapter we recognized the capacitors with lateral and vertical plate movement. However that was purely conceptual classification. In reality, there are four main structure types for variable MEMS capacitors used in modern harvesting systems as outlined in [13]. These are shown in Figure 2-1 as: a in-plane with gap closing; b in-plane with overlap; c out of plane with gap closing; and d in-plane with variable surface.

All four of these basic shapes can be fabricated as electret-free or electret-based capacitors. Due to ease of integration of such structures in MEMS processes, an abundance of work with different structures has been done, including design, simulations, fabrication and characterization. Some examples can be found in [28, 29, 31, 37] etc.

Seeing as the electrostatic forces acting between the capacitor plates, and the capacitor values are determined by shape of each individual structure, the following

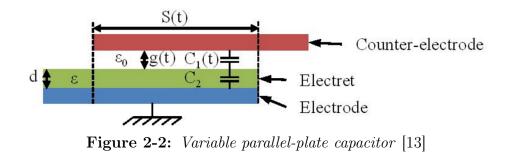

sections will outline the main equations for these quantities. But first, let us examine a basic parallel-plate capacitor with an electret layer, shown in Figure 2-2.

Due to the integrated electret layer, equivalent capacitance can be calculated as two capacitors in series as:

$$C_1(t) = \frac{\varepsilon_0 S(t)}{g(t)}; \quad C_2(t) = \frac{\varepsilon S(t)}{d} = \frac{\varepsilon_0 \varepsilon_r S(t)}{d}$$

(2.1)

$$C_{eq}(t) = \frac{C_1(t)C_2(t)}{C_1(t) + C_2(t)} = \frac{\varepsilon_0 S(t)}{g(t) + d/\varepsilon_r}$$

(2.2)

where  $\varepsilon_0$ ,  $\varepsilon_r$ , d, S, g are the vacuum permittivity, electret relative permittivity, electret thickness, overlap surface area, and gap between the parallel plates, respectively.

Attractive electrostatic force,  $F_{el}$ , between the capacitor's parallel plates is given by:

$$F_{el} = \frac{d}{dx} (W_{el}) = \frac{d}{dx} \left( \frac{1}{2} C_{eq}(x) U_c^2(x) \right) = \frac{d}{dx} \left( \frac{1}{2} \frac{Q_c^2(x)}{C_{eq}(x)} \right)$$

(2.3)

These equations for the basic parallel plate capacitor will make the derivation of the following equations easier and more comprehensible. It should be noted that these equations are derived for structures with an electret layer. Equations for electret-free structures are simply obtained by setting setting the electret thickness to be 0, i.e. d = 0.

## 2.1.1 Out of plane capacitor with gap closing

Equations for configuration shown in Figure 2-3 can be derived straight from the basic parallel plate model, by substituting the terminology from the figure. Plate movement is modeled as deviation x from the initial gap value  $g_0$ , while the overlap surface S is constant.

Figure 2-3: Out of plane gap closing capacitor [13]

$$C(x) = \frac{\varepsilon_0 S}{(g_0 - x) + d/\varepsilon_r}$$

(2.4)

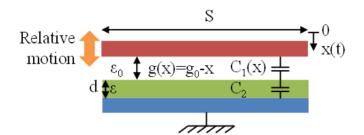

#### 2.1.2 In-plane capacitor with variable overlap surface

Similar to the previous example, equations can be easily derived from the basic model, with the difference of relative plate movement. Namely, in this case the movement is lateral, i.e. the gap is constant and the overlap surface S is variable, which is easily modeled as  $S(x) = w l(x) = w (l_0 - x)$ , where  $l_0$  is the initial overlap length, and wis the width of the plate (orthogonal dimension). This can be seen in Figure 2-4.

Figure 2-4: In-plane with variable overlap surface capacitor [13]

Variable capacitance is now modeled as:

$$C(x) = \frac{\varepsilon_0 w}{g + d/\varepsilon_r} \left( l_0 - x \right) \tag{2.5}$$

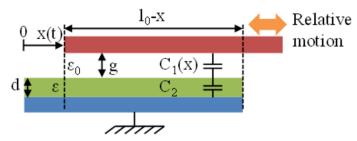

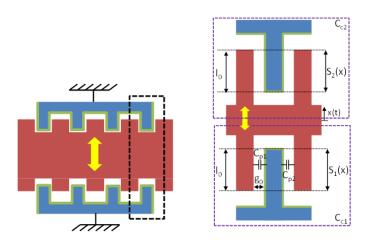

#### 2.1.3 In-plane comb capacitor with variable overlap

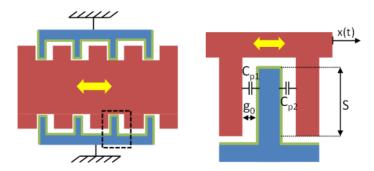

Illustrated in Figure 2-5 is the comb capacitor with N fingers, and in-plane variable overlap. If top and bottom electrodes are not connected, this structure acts as a dual capacitor, whose capacitances,  $C_{c1}$  and  $C_{c2}$  vary in anti-phase, i.e. when one capacitance increases due to increase in overlap on its side, the other capacitance decreases for the same value, due to decrease in overlap on its side.

Figure 2-5: In-plane comb capacitor with variable overlap surface [13]

Gap between the fingers is considered constant,  $g_0$ , and equal for all N fingers of the comb. Thickness of fingers is w (orthogonal dimension), and initial overlap is  $l_0$ , and is equal for both sides in absence of excitation. Variable overlap surfaces are modeled as:  $S_1(x) = w(l_0 - x)$  and  $S_2(x) = w(l_0 + x)$ . Variable capacitances can now be modeled as:

$$C_{c1}(x) = \frac{\varepsilon_0 N w}{g_0 + d/\varepsilon_r} (l_0 - x)$$

(2.6)

$$C_{c2}(x) = \frac{\varepsilon_0 N w}{g_0 + d/\varepsilon_r} (l_0 + x)$$

(2.7)

It should be noted that this is a simplified calculation, and that fringing capacitance, along with the capacitance contribution from the tip of the fingers are neglected. This is justified for long, thick and narrow fingers, or if the gap at the tip of the fingers is sufficiently large.

### 2.1.4 In-plane comb capacitor with gap closing

Similar to the previous example, with the difference in the relative structure motion, this structure has constant overlap length, and therefore constant overlap surface S. Gap between fingers is variable, with the initial value of  $g_0$ . As shown in the Figure 2-6, one of the fingers can be modeled as two parallel capacitors, with anti-phase gap variation, i.e. the gap on one side increases, whereas on the other side it decreases. These capacitances can be represented as:

$$C_{p1}(x) = \frac{\varepsilon_0 S}{(g_0 - x) + d/\varepsilon_r}$$

(2.8)

$$C_{p2}(x) = \frac{\varepsilon_0 S}{(g_0 + x) + d/\varepsilon_r}$$

(2.9)

Figure 2-6: In-plane comb capacitor with gap closing [13]

Total capacitance contribution of one finger is obtained by adding  $C_{p1}$  and  $C_{p2}$ . Total capacitance of the structure can be obtained by multiplying with the number of fingers, N:

$$C_{tot}(x) = C_{p1}(x) + C_{p2}(x) = \frac{2 N \varepsilon_0 S (g_0 + d/\varepsilon_r)}{(g_0 + d/\varepsilon_r)^2 - x^2}$$

(2.10)

Same as in previous case, contribution of the tip of the finger to the total finger capacitance is neglected.

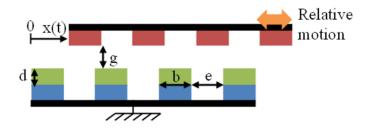

#### 2.1.5 In plane capacitor with variable patterned surface

The motivation behind this structure is to increase the capacitance variation for a given lateral displacement x. The structure is similar to the basic parallel plate capacitor, but the electrode surfaces have been patterned, as shown in Figure 2-7.

**Figure 2-7:** In-plane capacitor with patterned surface electrode [13]

If the structure is micro-patterned as shown in the figure above, it experiences significantly higher capacitance variation then the other presented structures, for a given displacement, which makes it very desirable for low-amplitude vibrations. Accurate analytical modeling is very difficult for this structure, due to a significant influence of fringe effects, and it is practically impossible to accurately calculate the capacitance. Even the FEM analysis would take unreasonable amount of time to calculate the capacitance as a function of displacement point-by-point. However, it is shown that if dimensions e and b are sufficiently small, capacitance experiences sinusoidal-like variation as a function of displacement, with two extrema:  $C_{min}$  and  $C_{max}$  [38]. These two values are relatively easy to obtain with FEM analysis, since it is a computation of capacitance for only two displacement values. Once the two values are computed, variable capacitance is conveniently expressed as:

$$C(x) = \frac{C_{max} + C_{min}}{2} + \frac{C_{max} - C_{min}}{2} \times \cos\left(\frac{2\pi x}{e+b}\right)$$

(2.11)

### 2.1.6 Summary

Previous section gave a brief overview for different MEMS variable capacitor structures. Electrostatic forces are calculated from (2.3), by deriving the electrostatic energy stored in the capacitor. For electret-based devices, the calculation is not as simple as expression change of both voltage and charge of the capacitor when the geometry is changing [13]. The results for electrostatic force for electret-free devices are summarized in Table 2.1 for both voltage and charge constrained mode of operation.

Table 2.1: Electrostatic force for different variable capacitor structures, for both charge and voltage constrained operation modes

| Structure                        | $F_{el}$ -charge constrained                              | $F_{el}$ -voltage constrained                                              |

|----------------------------------|-----------------------------------------------------------|----------------------------------------------------------------------------|

| Out of plane gap closing         | $\frac{Q_{const}^2}{2\varepsilon_0S}$                     | $\frac{\varepsilon_0  S  U_{const}^2}{2(g_0 - x)^2}$                       |

| In-plane overlap                 | $\frac{Q_{const}^2 g_0}{2  \varepsilon_0  w (l_0 - x)^2}$ | $\frac{\varepsilon_0  w  U_{const}^2}{2  g_0}$                             |

| In-plane comb overlap $(C_{c2})$ | $\frac{Q_{const}^2 g_0}{2 N \varepsilon_0 w (l_0 + x)^2}$ | $\frac{\varepsilon_0NwU_{const}^2}{2g_0}$                                  |

| In-plane comb gap closing        | $\frac{Q_{const}^2 x}{2 N \varepsilon_0 g_0 S}$           | $\frac{2 N \varepsilon_0 g_0 S x U_{const}^2}{\left(g_0^2 - x^2\right)^2}$ |

## 2.1.7 Discussion

Even though they offer many advantages, the most important being compatibility and ease of integration with MEMS processes, electrostatic energy harvesters are still the lesser known harvester, especially compared to piezoelectric harvesters. However, with technology advancements, and recent exponential growth of research devoted to MEMS technology, electrostatic harvesters are receiving increased attention of the researchers. Some limitations should be addressed when it comes to electrostatic transducer structures.

- i) Vibration frequency bandwidth and device operation frequency. Environmental vibrations are typically low frequency (< 100Hz). Furthermore, examination of vibration spectrum shows that they are widespread. This calls for low-frequency broadband harvesters. Many solutions are being investigated with complex, non-linear springs. For small-size devices, long and thin springs are needed to achieve this, which makes the structure less robust, since the springs undergo high stress from relatively large proof-masses.</p>

- ii) Some structures require gap control. Seeing as large capacitance variation is the key factor for achieving higher output power, it needs to be maximized, imposing the necessity for precise gap control to avoid the pull-in of the electrodes and discharge of accumulated charge, while considering the mechanical properties, such as maximum allowed strain.

- iii) The problem of start-up voltage. Can be easily solved with the usage of electret materials. However this imposes a new problem of electret stability, which is highly affected by external conditions, e.g. temperature and humidity. Additionally, necessary precautions must be taken to prevent contacts between electrodes and electret material to avoid discharge of electrets.

# 2.2 Power management circuit topologies

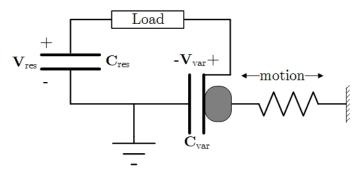

## 2.2.1 Primitive (continuous) topologies

Circuit shown in Figure 2-8 represents the most primitive interface circuit [39], consisting of a transducer modeled as a variable capacitor  $C_{var}$ , much larger reservoir capacitor  $C_{res}$  and a load. While this circuit has very little use for practical implementations in energy harvesters, it can be used in laboratory settings for transducer characterization [29].

Operation of the circuit relies on the assumption that the net charge of both  $C_{var}$ and  $C_{res}$  is constant in time, meaning that the capacitors are ideal and there are no leakage currents, which is not feasible for real devices. For the sake of simulations, we can use ideal components. The reservoir capacitance must be pre-charged. Initially, before the the variation of  $C_{var}$  starts, there is charge redistribution between the pre-charged  $C_{res}$  and  $C_{var}$ . Once the variations start, the charge will start flowing

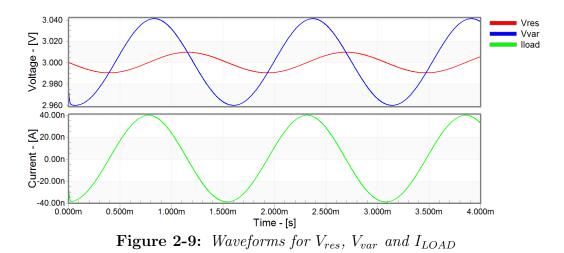

Figure 2-8: Primitive countinuous interface circuit

through the load back and forth between the two capacitances. Energy dissipated by the load is restored by the effort of external force that causes capacitance variation. For further illustration of the charge redistribution process, simulation results are shown in Figure 2-9.

As seen in figure above, this circuit is unable to increase the pre-charge voltage, it only restores small amount of energy dissipated by the load. Were this a real circuit, the leakage currents would eventually dissipate all the charge stored in capacitors, and the device would not function. Another drawback is that the load is supplied by an AC signal, which imposes the need for additional circuitry for rectification.

## 2.2.2 Charge Constrained Topology

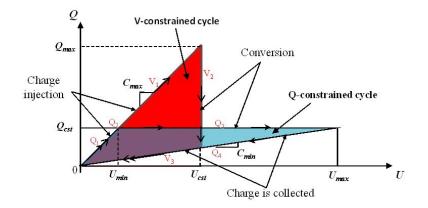

Charge constrained topology has previously been describe in Chapter 1 from a physics theory point of view. In this section, a more electrical approach is explained. Figure 2-10 illustrates the difference between a charge constrained and voltage constrained energy conversion in the Q - V plane. Both types of conversion start once the capacitance has reached its maximum value, i.e. the Q - V characteristic has the maximum slope. At that point charge is injected by an external source, which in most cases is a pre-charged reservoir capacitance.

**Figure 2-10:** Energy conversion cycles for electret-free devices [13]

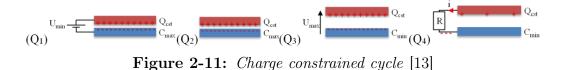

Figure 2-11 depicts a typical charge constrained operation cycle, to further illustrate the charge constrained energy conversion. The cycle starts once the capacitance reaches its maximum value  $C_{max}(Q_1)$ . At this point, an external source supplies the charge  $Q_{cst}$ , and the device is left floating, with a terminal voltage of  $U_{min}$ . Due to the work exerted by external forces, capacitance decreases until it reaches the value  $C_{min}$ , while the voltage increases, according to equation  $Q_{const} = U(t) C(t) = U_{max} C_{min} = U_{min} C_{max}$ . Typically the device is now coupled back into a circuit to resupply the storage element.

Total amount of harvested energy is evaluated as:

$$W_{harvested} = \frac{1}{2} Q_{const}^2 \left( \frac{1}{C_{min}} - \frac{1}{C_{max}} \right)$$

(2.12)

A charge constrained interface circuit topology, proposed by Meninger et. al. [40] is illustrated in Figure 2-12. It uses an inductor as an intermediate element for energy transfer, and two switches. This circuit also requires pre-charging of the large reservoir capacitance.

Figure 2-12: Charge constrained interface circuit

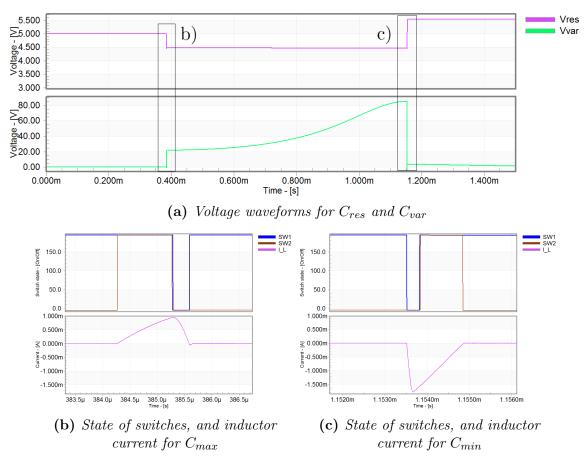

To illustrate the operation of this circuit in terms of voltage and current waveforms, a simple design was implemented and a simulation was performed. Representative waveforms for one harvesting cycle are presented in Figure 2-13.

Figure 2-13: Simulated waveforms for the charge constrained interface circuit

Operation can be described in a few steps: i) When  $C_{var}$  reaches its maximum

value,  $S_2$  is closed, and the inductor L is charged-up with the energy from the precharged  $C_{res}$ ; ii)  $S_2$  opens and  $S_1$  closes. Energized inductor continues to conduct, now charging  $C_{var}$ , which can be seen in Figure 2-13b; iii) both switches are open, and the capacitance varies slowly until it reaches its minimum value, while the voltage  $V_{var}$  increases; iv)  $S_1$  closes, and the inductor is charged-up with the energy from the variable capacitance, with a higher current, due to the high voltage of the variable capacitor now has high voltage; v)  $S_1$  opens,  $S_2$  closes, and the energized inductor recharges the reservoir capacitance. It should be noted that the simulation results in Figure 2-13 are for illustration purposes only, because capacitor and inductor values were not chosen to resemble a realistic scenario, but more as a proof of concept illustration.

### 2.2.3 Voltage Constrained Topology

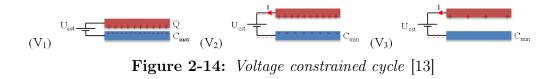

Voltage constrained energy conversion cycle is illustrated in Figure 2-14. Similar to charge constrained cycle, this cycle also begins when the variable capacitance reaches its maximum value. The capacitor is then connected to an external source, which creates a constant voltage  $U_{cst}$  between the plates of the capacitor  $(V_1)$ . In contrast with the charge constrained cycle, the external source is not disconnected from the transducer, and constant voltage will be maintained at the electrodes throughout the cycle. Having a constant voltage, while the capacitance decreases, the amount of charge will also decrease according to  $U_{cst} = \frac{Q(t)}{C(t)}$ . In other words there will be a current  $i = \frac{dQ}{dt} = C\frac{\partial U}{\partial t} + V\frac{\partial C}{\partial t} = V\frac{dC}{dt}$  flowing from the capacitance and resupplying the source  $(V_2)$ . By the time the capacitance reaches its minimum value  $C_{min}$ , total charge of the capacitor will have been collected and stored in the supply  $(V_3)$ .

Total amount of harvested energy is evaluated as:

$$W_{harvested} = -\int_{t_0}^{t_1} u(t) \, i(t) \, dt = U_{const}^2 \left( C_{max} - C_{min} \right) \tag{2.13}$$

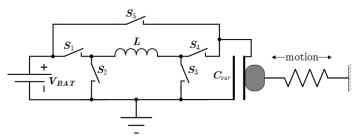

A simple voltage constrained circuit topology, proposed by Torres et. al. [41] is shown in Figure 2-15. Their proposed circuit uses small thin film Li-Ion polymer battery instead of a reservoir capacitance, five switches for circuit reconfiguration, an inductor as an intermediate element for energy conversion and a variable capacitor.

Figure 2-15: Voltage constrained interface circuit

A typical operation cycle can be described with two phases: i) Pre-charge phase: battery energizes the inductor through switches  $S_1$  and  $S_3$ . Inductor current linearly increases, and when the inductor energy becomes sufficient,  $S_1$  and  $S_3$  open. Next step is to drive the energy stored in the inductor to the variable capacitor whose capacitance has reached its maximum value  $C_{max}$ . This is accomplished by closing the switches  $S_2$  and  $S_4$ , which causes the variable capacitor to be charged to the battery voltage level; ii) Harvesting phase begins once switch  $S_5$  closes. Since the voltage on both battery and  $C_{var}$  is constant, and the variable capacitance decreases, causing the charge to flow from  $C_{var}$  into the battery. Harvesting cycle ends once  $C_{var}$ reaches its minimal value. Theoretically, third phase can be energy recovery phase. After harvesting phase, there is still some energy stored in the variable capacitor, which can be recovered through a process reverse of the pre-charge. However the power consumption of the circuit controlling the switches, and power losses of nonideal components are usually higher than the amount of recovered energy, which would decrease the overall efficiency of the system.

### 2.2.4 Charge pump topologies

Charge pump interface circuit has one major advantage over the circuits previously mentioned. Namely, they are self-oscillating in terms of charge transfer onto and out of the variable capacitor, by using diodes instead of switches, which significantly simplifies the interface circuit and increases overall system efficiency by decreasing the power dissipation. Several topologies are presented in the following subsections.

#### Basic charge pump

Basic charge pump circuit, proposed by [28] is shown in Figure 2-16. Operation of the circuit consists of three phases. Initially, diodes are off, and once  $C_{var}$  reaches

$C_{max}$ , diode  $D_1$  is on, and charge is transferred from  $C_res$  to  $C_{var}$ . Once the capacitance starts to decrease, both diodes will be off, until the decrease of capacitance causes sufficient increase in voltage to turn on  $D_2$ . In the third phase charge is transferred to an intermediate storage capacitor  $C_{store}$ .

Figure 2-16: Basic charge pump interface circuit

Since the diodes only enable a unidirectional flow of charge  $(C_{res} \rightarrow C_{var} \rightarrow C_{store})$ , this circuit has no practical significance. After a number of oscillation intervals, the voltage at  $C_{store}$  will begin to saturate at:

$$V_{store,sat} = \left(\frac{C_{max}}{C_{min}}\right) V_{res} \tag{2.14}$$

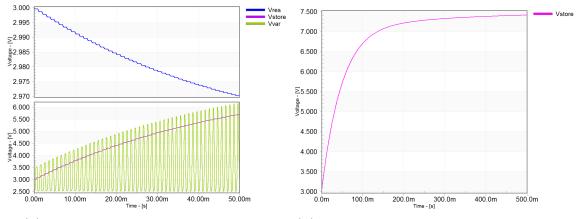

which can be seen in the simulation waveforms shown in Figure 2-17b. Following sections will present a few possible methods for a return path, so the harvested energy is used to resupply  $C_{res}$ .

(a) Waveforms for V<sub>res</sub>, V<sub>var</sub> and V<sub>store</sub>

(b) Saturation of V<sub>store</sub> over a longer period

Figure 2-17: Simulation results for the basic charge pump circuit

#### Charge pump with resistive return path

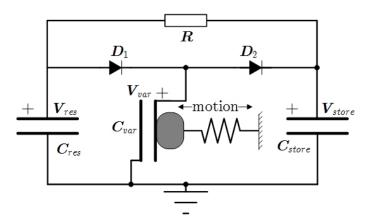

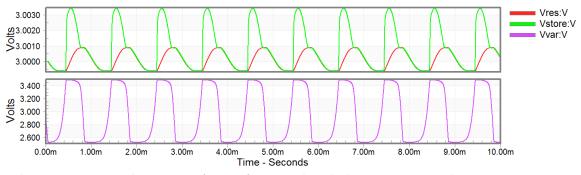

The simplest method for resupplying  $C_{res}$  is by using a resistor in the return path from  $C_{store}$  to  $C_{res}$  [42], as shown in Figure 2-18. Now, there are two paths for flow of charges, one from the reservoir capacitor to storage capacitor pumped by the variable capacitor and diodes, and another in the opposite direction, through the resistor, due to the voltage drop  $V_{resistor} = V_{store} - V_{res}$ .

Figure 2-18: Charge pump with a resistive return path

Although it offers simplicity, this circuit also has very little use in energy harvesters, except for laboratory testing [31], transducer characterization and such. A major drawback of the circuit is that it cannot increase the pre-charge voltage  $V_{res}$ , because the energy cannot be accumulated, as illustrated with simulated waveforms shown in Figure 2-19, it only restores energy dissipated by the resistance. In a real setting, capacitors would have some leakage, and eventually capacitors would discharge and circuit would become inactive.

Figure 2-19: Voltage waveforms for simulated charge pump with a resistive return path

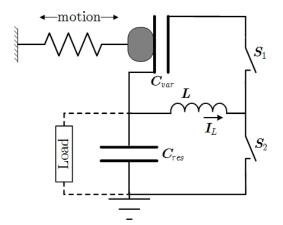

#### Charge pump with inductive flyback path

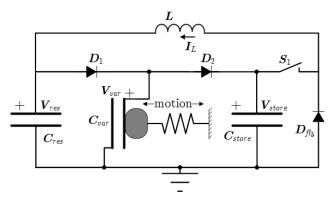

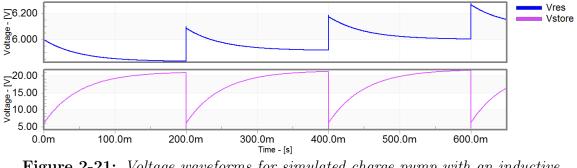

This circuit is based on a famous Buck converter, and was proposed by Yen et. al. [42], and is shown in Figure 2-20. This topology offers various advantages, the most important of which is acuumulation of energy. Namely, while the switch is kept open, the inductive flyback path is not connected, allowing the charge to accumulate on  $C_{store}$ , and once the switch closes, the charge is transferred to  $C_{res}$ , through the flyback inductor. Diode  $D_{fly}$  has the purpose of maintaining the inductor current after the switch opens. As the load is not connected, the energy accumulates on  $C_{res}$ which allows increase of the pre-charge voltage. Another advantage is the reduced complexity of the switch control circuit, compared to previously presented circuits, since there is only one switch in the circuit and its state is a function of  $V_{store}$  instead of  $C_{var}$ .

Figure 2-20: Charge pump with a inductive flyback return path

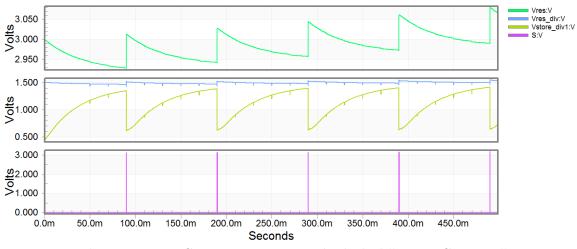

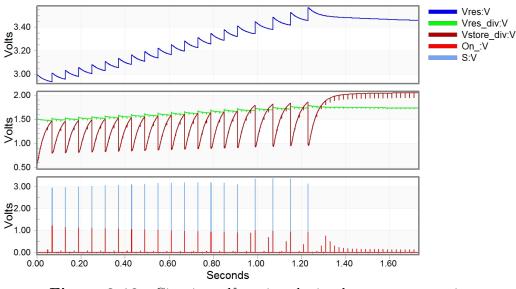

Figure 2-21 represents simulated waveforms for  $V_{res}$  and  $V_{store}$  over a longer period of time. It is shown that once the  $V_{store}$  rises to the proximity of its saturation voltage, the switch is closed, and the charge is transferred from  $C_{store}$  to  $C_{res}$ , through the inductor, causing the increase in  $V_{res}$ .

Figure 2-21: Voltage waveforms for simulated charge pump with an inductive return path

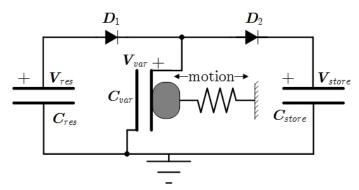

#### Double charge pump

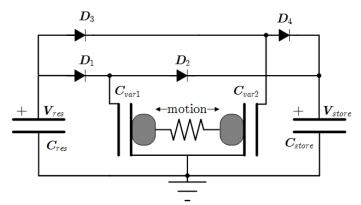

For transducers which allow having two anti-phase variable capacitances, such as the one shown in Figure 2-5, double charge pump circuit can be used, such as the one shown below in Figure 2-22. This circuit has the same working principle as basic charge pump, but it has twice the frequency of charge flow from  $C_{res}$  to  $C_{store}$ . In the first half-period,  $C_{var1} = C_{max}$ ,  $C_{var2} = C_{min}$ . Consequently, diodes  $D_1$  and  $D_4$  are on, whereas  $D_2$  and  $D_4$  are off, allowing  $C_{res}$  to transfer its charge to  $C_{var1}$  and  $C_{var2}$ to  $C_{store}$ . In the second half-period, state of the diodes is complement.

Figure 2-22: Double charge pump interface circuit

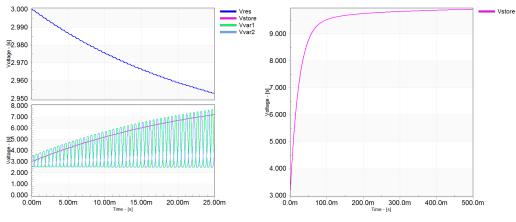

Circuit has been simulated with the same operating conditions and parameter values as the basic charge pump, and the simulation results are presented in Figure 2-23. The charge is transferred from  $C_res$  with twice the frequency: in the first halfperiod to  $C_{var1}$  and in the second  $C_{var2}$ , as shown in Figure 2-23a. Consequently, the saturation voltage  $V_{store,sat}$  on  $C_{store}$  is reached twice as fast, making this circuit topology twice as effective as basic charge pump. Additionally it is easily expanded with an inductive flyback path.

(a) Simulated waveforms for V<sub>res</sub>, V<sub>var</sub>

(b) Saturation of V<sub>store</sub> over a longer and V<sub>store</sub>

(b) Saturation of V<sub>store</sub> over a longer

Figure 2-23: Simulation results for the double charge pump circuit

### 2.3 Summary and Discussion

This chapter presented various transducer structures, outlining their advantages and drawbacks. In summary, structures that offer higher capacitance variations tend to be more efficient for energy harvesting applications, if coupled with an effective interface circuit. In traditional structures, such as ones shown Figures 2-3,2-4, 2-6 and 2-5 capacitance variation is restricted by the by mechanical limits, i.e. maximum displacement of the proof mass, which in some cases makes it difficult to achieve high variations. Structures such as the one shown in Figure 2-7, offer higher capacitance variation with very little limitation from maximum displacement. This comes at the expense of fabrication cost and complexity, since the patterned surface needs to fulfill certain requirements.

Second part of this chapter focused on the energy interface circuits, in terms of their role in energy harvesters, their efficiency requirements and different existing topologies. Even though voltage constrained circuits seem to offer higher efficiency than their charge constrained counterparts [43], their accompanying control circuit is much more complex, and therefore much more power hungry. To avoid the complex operation of switch synchronization with the variable capacitance, charge pump topologies offer a convenient self-oscillating mode of operation, as illustrated above. Since this project is based on a comb structured transducer, with dual, anti-phase variable capacitances, double charge pump topology is chosen as the interface circuit, due to the many advantages it offers. The return path is with an inductive flyback element, because it offers the possibility of energy accumulation, and hence the pre-charge voltage increase, whereas conversely the resistive return cannot.

## Chapter 3

# Interface circuit and flyback switch control circuit design

This chapter is dedicated entirely to the electronic circuit part of the harvesting system. First two sections provide technical information concerning the project. Following sections are dedicated to the previous work on this project, concerning the interface circuit, as well as modifications made in this project, followed up by additional components necessary to make this circuit autonomous.

### 3.1 Software tools

For the purpose of this project, Tanner EDA Tools v16.3 was used for circuit design and simulations. Tanner EDA Tools is an integral part of Mentor Graphics<sup>®</sup>, which allows full analog-mixed signal design process, including schematic capture (S-Edit), circuit simulation (T-Spice), waveform viewing (W-Edit), IC layout design with parasitic extraction (L-Edit) and verification (Verify DRC and LVS). This project was focused on circuit design in schematic view and simulations with T-Spice.

### 3.2 Process technology

For the purpose of this project, energy harvester node with energy accumulation, higher than standard voltages are expected, and to that end, high-voltage CMOS process from Austria-Microsystems was used (AMSH35). Originally released in 2004, it is a very mature process, with vast experience among the circuit designers and reliable models for components. It offers MIM capacitors and both low and high-

voltage MOSFETs.

The most important process parameters are outlined in Table 3.1. Technology is based around a 3.3V MOS transistors using thin oxide, with a minimum feature of  $0.35\mu m$ . Aside from that, there are transistors which can withstand higher gate voltages, 5V and 20V, using medium and thick oxide. Capacitors can be designed using the two available poly-silicon layers, however higher poly-silicon resistivity should be taken into consideration, since it degrades the capacitor properties, such as linearity, ESR etc. Advantage is that the same capacitance occupies less area than its MOS counterpart.

| Process technology                                      | HV CMOS $0.35\mu m$ |  |  |

|---------------------------------------------------------|---------------------|--|--|

| Gate oxide capacitance                                  | $4.54 \ fF/\mu m^2$ |  |  |

| $V_{th}$ for standard NMOS short/long channel           | 0.5/0.46V           |  |  |

| Gain factor $K_N$ for standard NMOS                     | $170  \mu A/V^2$    |  |  |

| $V_{th}$ for standard PMOS short/long channel           | $-0.68/{-0.65V}$    |  |  |

| Gain factor $K_N$ for standard PMOS                     | $58\mu A/V^2$       |  |  |

| $V_{th}$ for thin oxide HV NMOS short/long channel      | 0.45/0.47V          |  |  |

| $V_{th}$ for thin oxide HV PMOS short/long channel      | $-0.63/{-0.7V}$     |  |  |

| Supply voltage                                          | 3.3V,5V,20V,50V     |  |  |

| $ V_{G-S/B,max} $ for thin, medium, thick oxide devices | 3.3V, 5V, 20V       |  |  |

**Table 3.1:** Relevant  $0.35\mu$ m process parameters

In this design, 20V HV MOS transistors with thin oxide are used in high-voltage interface circuits, to be able to withstand higher voltages in the long-term circuit operation. There are several drawbacks of using HV transistors, including the need for longer channel devices in order to achieve high breakdown voltages, which increases the channel resistance as well as higher gate capacitance. However, HV transistors are a necessity, since the circuit would ideally increase the voltage to a higher value, but understanding the limitations of the technology is an important design point for creating a functional and reliable design.

### 3.3 Transducer model

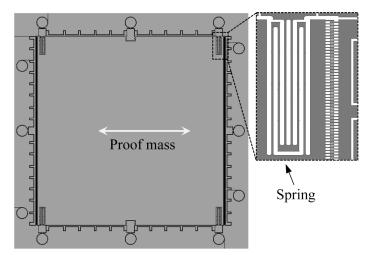

As was previously mentioned, transducer considered for this project is a comb-drive based structure, consisting of a relatively large proof-mass suspended by four springs which are connected to two fixed electrodes (anchors), with N being number of overlap fingers,  $l_0$  initial overlap without excitation,  $g_0$  constant gap, as shown in Figure 3-1.

Figure 3-1: In-plane comb capacitor with variable overlap [36]

Variable capacitance can be expressed as:

$$C_{c1/2}(x) = \frac{N \varepsilon_0 w}{g_0} (l_0 \mp -x) = \frac{N \varepsilon_0 w l_0}{g_0} \left(1 \mp \frac{x}{l_0}\right) = C_0 \left(1 \mp -\frac{x}{l_0}\right)$$

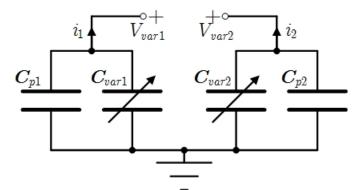

(3.1)

where  $\varepsilon_0$  and x are vacuum permittivity and proof-mass displacement, respectively. However, there is a parasitic capacitance in parallel with the variable capacitor. Including this effect, the transducer can be modeled in electrical domain as shown in Figure 3-2. In real devices, these parasitic capacitances are not equal, due to process variations and mismatch effects, but their difference can be considered negligible for this analysis.

Figure 3-2: Electrical domain transducer model

Take note that the currents  $i_1 = -\dot{q_1}$  and  $i_2 = -\dot{q_2}$  represent the charge flow due to capacitance variation,  $q_1$  and  $q_2$  being charge of the individual capacitors. Transducer

interface voltages can now be expressed as:

$$V_{var1/2} = \frac{q_{1/2}}{C_{var1/2}(x) + C_p}$$

(3.2)

#### Capacitance variation

In order to continue with circuit design and implementation, parameters for the variable capacitors are needed. Disregarding process variations and mismatch effects, variable capacitances are considered to have same parameters, as are their respective parasitic capacitances. These parameters are summarized in Table 3.2.

| Parameter                       | Value             |

|---------------------------------|-------------------|

| Capacitance when idle, $C_0$    | 2.3 pF            |

| Parasitic Capacitance, $C_p$    | 2  pF             |

| Overlap when idle, $l_0$        | $16 \ \mu m$      |

| Maximum displacement, $x_{max}$ | $15 \mu { m m}$   |

| Resonant frequency, $f_0$       | $650~\mathrm{Hz}$ |

Table 3.2:

Parameters of the transducer

For the purpose of simulations, a single harmonic vibration at resonant frequency is assumed. If the the vibration force has a sinusoidal shape, considering linear springs, response of the transducer, in terms of proof-mass displacement, i.e. overlap length x will have the following form:

$$x(t) = x_{max} \sin\left(2\pi f_0 t\right) \tag{3.3}$$

Total variable capacitance, under such excitation is obtained by substituting (3.3) into (3.1) and including the parasitic capacitance:

$$C_{v1/2} = C_p + C_{var1/2} = C_p + C_0 \left( 1 \mp \frac{x_{max} \sin \left(2\pi f_0 t\right)}{l_0} \right)$$

(3.4)

For further simplification and convenience, expression (3.4) can be rewriten as:

$$C_{v1/2} = (C_p + C_0) \mp C_0 \frac{x_{max}}{l_0} \sin(2\pi f_0 t) = C_{const} + \Delta C \sin(2\pi f_0 t)$$

(3.5)

where  $C_{const} = C_p + C_0 = 4.3 \text{pF}$  and  $\Delta C = C_0 \frac{x_{max}}{l_0} = 2.16 \text{pF}$ . Consequently, the capacitance variation range is:  $C_{v1/2} \in [C_{min}, C_{max}] = [2.14, 6.46] \text{ pF}$ .

These capacitances are modeled in Tanner Tools' *S-Edit* by instantiating a sinewave voltage source with a DC offset of 4.3 and amplitude of 2.16, and using its output as a parameter with which to multiply a 1pF capacitance.

### 3.4 Interface circuit topology

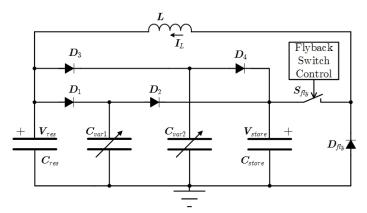

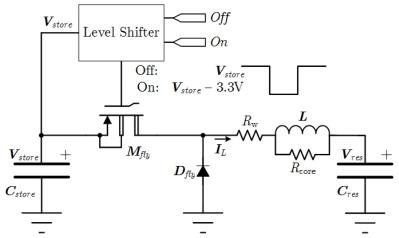

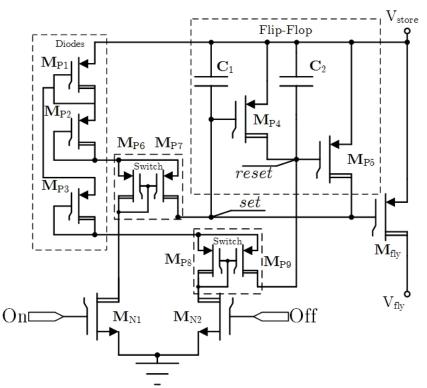

Due to transducer structure with two anti-phase variable capacitances, a double charge pump topology is used, utilizing an inductive flyback return path. Final interface circuit, with the exception of the flyback switch control circuit, can be seen in Figure 3-3. Switch control circuit will be described in details in following sections.

Figure 3-3: Double charge pump interface circuit with inductive flyback return path

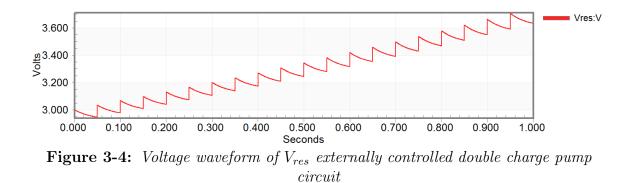

To illustrate energy harvesting process with this circuit topology and transducer parameters, a simulation was preformed using the circuit seen in Figure 3-3, and simulation results are shown in Figure 3-4. For the purpose of this simulation, and estimation of harvested energy with an externally controlled switch, an appropriately connected, ideal pulse generator was used.  $V_{res}$  voltage waveform is presented in Figure 3-4.

As seen in figure above, a voltage simulated increase over 1s of simulation time amounts to  $\Delta V_{res} = 0.63V$ . Estimation of harvested energy can be expressed as a difference of stored energy in the reservoir capacitance at the end and the beginning of the simulation.

$$W_{harvested} = \Delta W_{res} = \frac{1}{2} C_{res} \left( V_{res}^2 \mid_{t=t_{sim}} - V_{res}^2 \mid_{t=0} \right) = 8.33nJ$$

(3.6)

or in terms of harvested power averaged over time period of 1s:

$$P_{harvested,ext} = \frac{W_{harvested}}{\Delta t} = \frac{W_{harvested}}{t_{sim}} = 8.33nW \tag{3.7}$$

Initially, parametric simulations were performed to determine optimal period and pulse width of the pulse generator. It was noticed that maximum voltage increase on  $C_{res}$ , for 1s simulation time, is achieved with a period  $T_{pulse} = 50ms$  and pulse width of  $\tau = 1.2\mu s$ . Choosing an optimal value for the period reflects the trade-off between the amount of the charge collected from  $C_{store}$  for one switching cycle and the average amount of charge collected over a longer period. Since the voltage increase on  $C_{store}$ has a logarithmic form and a saturation limit, waiting longer for harvesting phase is not very efficient. On the other hand, analysis of choosing an optimal pulse width, i.e. the time during which the switch is on, is a more complex analysis which will be explained later. For now, it should be noted that lower pulse width would cause Table 3.3 offers a comparison of harvested energy for different pulse signal periods, with initial, pre-charge voltage  $V_{res} = 3V$  and pulse width  $\tau = 1.2\mu s$ .

| Pulse period, $T_{pulse}$ | $V_{res} _{t=1s}$ | Harvested energy, $W_{harvested}$ |

|---------------------------|-------------------|-----------------------------------|

| 1.563 ms                  | 3.0002V           | 0.006 nJ                          |

| 2ms                       | 3.00V7            | 0.210nJ                           |

| 10ms                      | 3.084V            | 2.555nJ                           |

| 25ms                      | 3.204V            | 6.328nJ                           |

| 50ms                      | 3.266V            | 8.334nJ                           |

| 100ms                     | 3.145V            | 4.455 nJ                          |

| 500ms                     | 2.975V            | -0.747 nJ                         |

Table 3.3: Harvested energy vs. pulse signal period

#### Discussion of the results

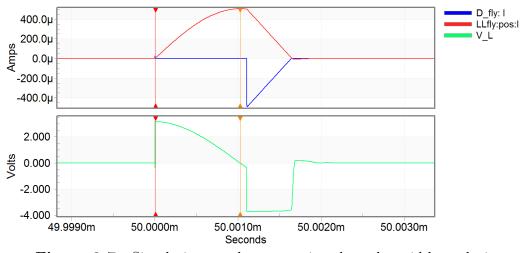

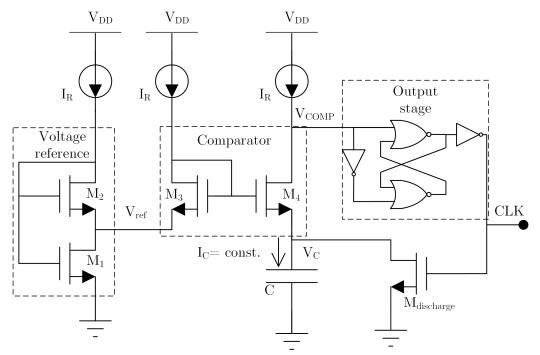

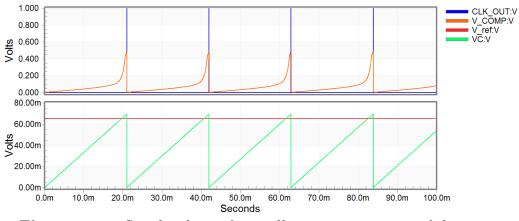

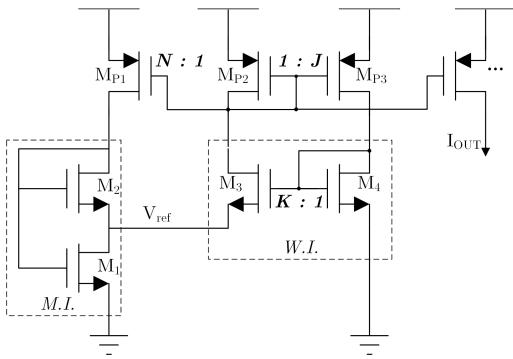

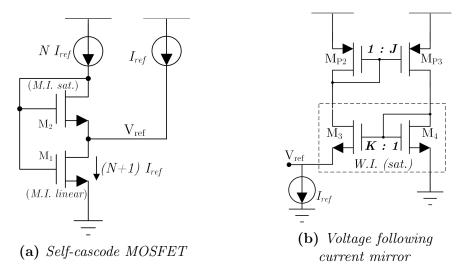

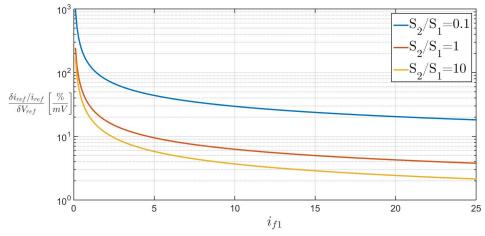

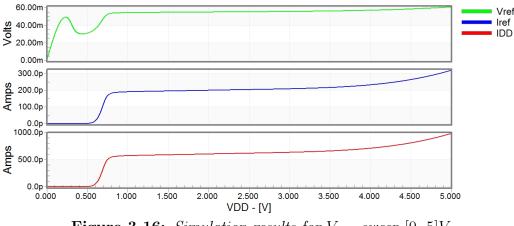

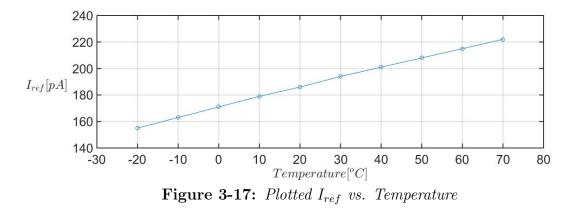

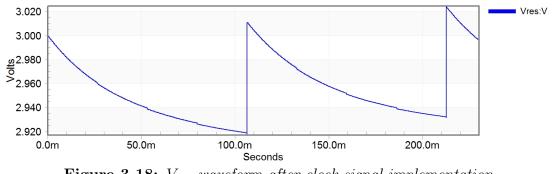

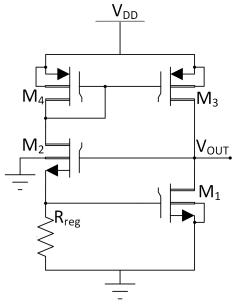

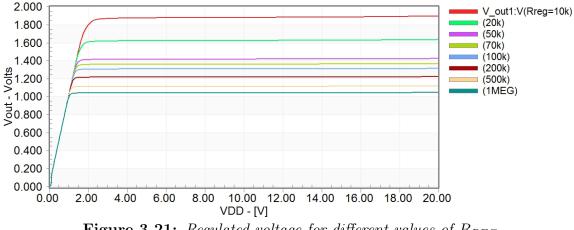

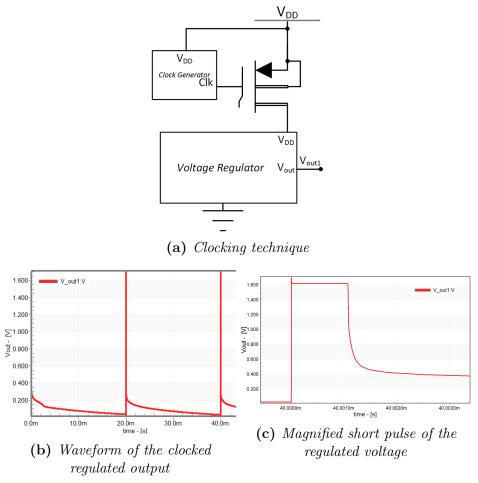

It should be noted that even though harvested energy is negative for  $T_{pulse} = 500ms$ , average harvested power over a longer period of time would not be. This happened because  $C_{store}$  is well saturated before the switching happens, and the time waited for the switch to open is not justified by the amount of energy harvested. It happened that during 1s of simulated circuit operation  $C_{store}$  saturated twice,