Steven Bos

# Beyond 0 and 1:

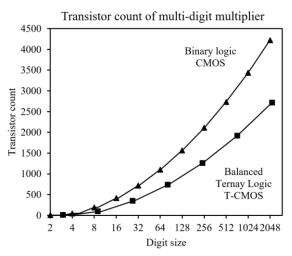

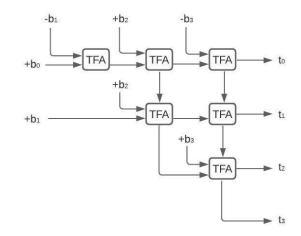

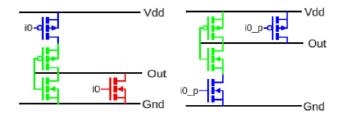

A mixed radix design and verification workflow for modern ternary computers

**Dissertation for the degree of Ph.D** Technology

Faculty of Technology, Natural Sciences and Maritime Studies

### Steven Bos

# Beyond 0 and 1:

A mixed radix design and verification workflow for modern ternary computers

A PhD dissertation in **Technology**

© Steven Bos, 2024

Faculty of Technology, Natural Sciences and Maritime Studies University of South-Eastern Norway Kongsberg

#### Doctoral dissertations at the University of South-Eastern Norway no. 189

ISSN: 2535-5244 (print) ISSN: 2535-5252 (online)

ISBN: 978-82-7206-854-6 (print) ISBN: 978-82-7206-855-3 (online)

This publication is licensed with a Creative Commons license. You may copy and redistribute the material in any medium or format. You must give appropriate credit, provide a link to the

license, and indicate if changes were made. Complete license terms at https://creativecommons.org/licenses/by-nc-sa/4.0/deed.en

Print: University of South-Eastern Norway

To my heroes Koen & Susan Bos-Theuvenet

# Preface

This dissertation is submitted in partial fulfilment of the requirements for the degree of Doctor of Philosophy (PhD) in Technology from the Department of Science and Industry Systems at the University of South-Eastern Norway (USN). The doctoral work presented here took place between June 1, 2019 and June 1, 2023. The majority of the research was conducted at USN campus Kongsberg in Norway and with some work done at USN campuses Vestfold and Porsgrunn. The work has been done under the supervision of Assoc. Professor Henning Gundersen (USN) and Professor Nils-Olav Skeie (USN). Further guidance was received from the midterm evaluation committee Professor Philipp D. Häfliger from the University of Oslo (UiO) and Professor Lars M. Johansen (USN).

The PhD work was financially supported by the Norwegian Ministry of Education and Research (Kunnskapsdepartementet) and USN as a 4 year PhD Research Fellowship (KD-stilling) with 25% teaching duties.

The candidate is a member of the IEEE MVL and CAS societies as well as the research school for Training the Next Generation of Micro- and Nanotechnology Researchers in Norway (TNNN).

# Acknowledgements

During my four year PhD journey I had the pleasure of meeting wonderful and inspiring people and perhaps a new version of myself. Moving from The Netherlands to Norway with my wife and learning the Norwegian language and rich culture was not possible without a long list of people mentioned below – *mea culpa* if I missed some of you!

Without my supervisors Assoc. Professor Henning Gundersen and Professor Nils-Olav Skeie my adventure in the world of ternary computing would not have started. I am deeply grateful for the time they spend with me.

Research is not one solitary endeavour nor does it start at zero as we always build on the insights made before us. Working closely with my fellow co-authors was a true privilege and I like to thank them again for their contributions. Collaborating with Professor Knut E. Aasmundtveit and Assoc. Professor Avisek Roy was immensely valuable as I was able learn about the possibilities of carbon nanotubes and nanofabrication at USN. Thank you for sharing your knowledge and I look forward to continuing our collaboration.

The knowledge landscape is shaped by giants and discussing my research on multi-state memristors with the inventor of these devices, Professor Leon Chua from UC Berkeley was extraordinary. At the start of my PhD I stumbled upon the work of professor Kris Campbell from Boise State University on programming memristors. Her detailed work inspired me to investigate the analog switching properties of resistive memory. I also like to thank the many great minds I met both in-person and virtually due to the COVID pandemic.

A huge thanks to Professor Morten Melaaen (dean), Assoc. Professor Elisabet Syverud (head of department), Professor Olaf Hallan Graven (former head of department) and Rune Romnes for providing me with a great work environment and resources. Thanks to the USN PhD committee and PhD coordinators Mariken Kjøhl-Røsand, Per Morten Hansen and Siri Luise Tveitan for guidance, structure and organizing the inspiring PhD forums. I must mention the colleagues I had the pleasure to teach three courses with the past four years: Professor Dag Samuelsen, Joakim Bjørk, Richard Thue and dr. Richard Anthony. The teaching experience was both academically rewarding and fun. *Tusen hjertelig takk til* Assoc. Professor Sigmund Gudvangen for teaching me the nuances in bokmål and nynorsk and Karoline Moholth Mcclenaghan for sharing her thrilling stories about the first computers in Norway. I am very grateful to Professor Rigmor Baraas from the department of Optometry to allow me to present my PhD work to the Norwegian prime minister Jonas Gahr Støre.

Starting a new research group together with Assoc. Prof. Henning Gundersen brought structure to my work. Meeting weekly with members of the Ternary Research Group, discussing and disseminating the tiniest results was a true joy. I like to thank all members present and past for input on papers and their open-mindedness to explore an unconventional computing paradigm. I especially enjoyed the boundless energy of dr. Radmila Juric.

I had the opportunity to supervise four bright MSc students Halvor Nybø Risto (now PhD candidate), Julian Breivold Nilsen, Mehtab Singh Virk and Erika Fegri and assisted several BSc groups. Thanks for sharing the long hours in pursuit of the adrenaline rush of inevitable progress. I like to thank post-doc dr. Fahim Ahmed Salim and my fellow PhD candidates for an awesome time: Walter Kibet Yego, Haytham Ali, Rune Andre Haugen, Tommy Langen, Agnieszka Lach, Soheila Taghavi Hosnaroudi and Raghav Sikka.

Sharing my work with my old and new friends, brother Niels and sister Jenna-Fay and the always curious Bos and Theuvenet family was immensely relevant. It forced me to find new metaphors and take different viewpoints. Thank you for your support!

This dissertation would not be possible without the unwavering support and extreme patience of my wife Jessica Stokhof. I am hugely indebted and will start returning the immense favor with this ternary thank you:  $3^{\text{thank you}}$

# Steven Bos

Kongsberg, 1st November 2023

# Abstract

For more than 80 years digital computers use the radix-2 or *binary* computer alphabet as their lowest symbolic and physical representation. This doctrine of computing is presumed in every modern computer. The radix economy theorem derives that radix-3 or *ternary* is however the optimal radix. Ternary is the first radix in the Multiple-Valued Logic (MVL) family that enables symmetrical arithmetic using the balanced ternary notation. The ongoing challenge is to engineer devices, circuits and systems that can physically represent three logic levels with competitive power, performance, area and cost metrics. For flash storage and communication MVL is already the industry standard, but logic remains binary. Ever since Dennard scaling stopped in 2005, binary computing is struggling to overcome the increasing power wall, memory wall and Electronic Design and Automation (EDA) wall. A unified MVL compute paradigm can theoretically address these challenges, making it a prime candidate for the beyond-CMOS era.

This article-based thesis is structured in three parts. In the first part binary computing is discussed. The historical reasoning for this choice as well as the current scaling challenges that impede its future were reviewed. The part concludes with a review of several fundamental and engineering limits that are rarely cited but highly relevant when considering another radix such as Shannon's noisy channel theorem and Rent's rule.

In the second part ternary computing is discussed. A brief overview of radix-3 theory and literature is presented. A novel radix comparison methodology is proposed to improve fairness. Historical efforts to build ternary computers were reviewed which started in the 1950's. A categorization of the main benefits of balanced ternary is presented across 7 application domains. The part concludes with an overview of the critique on radix-3.

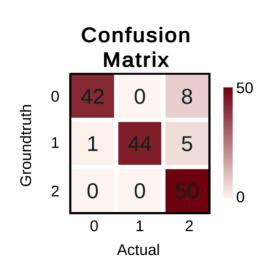

In the third part practical aspects of ternary computing are discussed: multi-stable devices and EDA tooling. For devices, non-volatile ternary memory control with commercially available memristors was studied. A novel open source software tool uMemristorToolbox and hardware platform for multi-state memristor programming were developed. The experiments confirm that ternary memory with memristors is both feasible and low-cost.

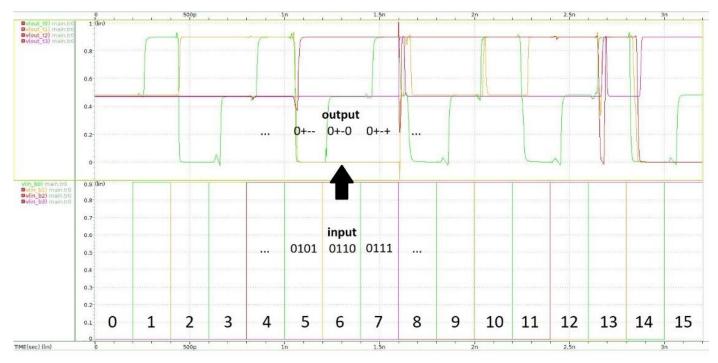

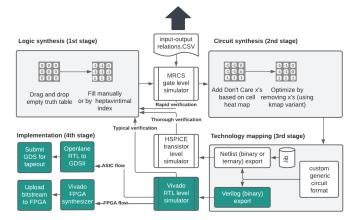

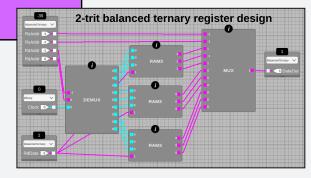

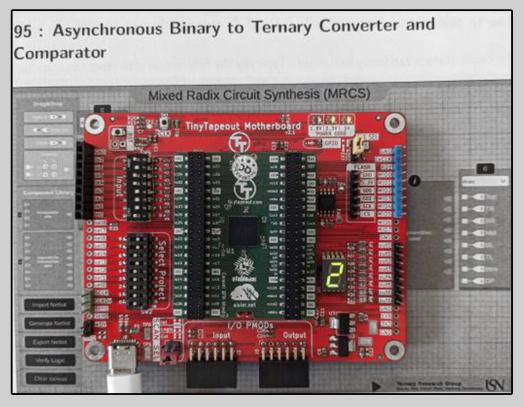

Lastly, EDA tooling and workflows for ternary logic chips are discussed. The open source software tool Mixed Radix Circuit Synthesizer (MRCS) was developed, the first browserbased EDA tool to design and verify binary, ternary and hybrid (mixed radix) circuits. It features a novel MVL circuit synthesis algorithm with HSPICE and verilog output targeting CMOS and multi-threshold CNTFET. The tool was used to design REBEL-2, a novel balanced ternary CPU with RISC-V-like ISA. Four MRCS designs have been tested on a FPGA and submitted for tape-out using the Openlane ASIC workflow.

Keywords: ternary microprocessor, design automation, integrated circuit synthesis

# Contents

| Pre | eface                                    |                                                                                                       |                        | III                                                                                                                                                    |

|-----|------------------------------------------|-------------------------------------------------------------------------------------------------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ab  | stract                                   |                                                                                                       |                        | v                                                                                                                                                      |

| Co  | List c<br>List c<br>List c               | of Papers<br>of Co-sup<br>of Figure<br>of Tables                                                      | s                      | . XIII<br>. XVI<br>. XVI                                                                                                                               |

| 1   | Intro<br>1.1<br>1.2<br>1.3<br>1.4<br>1.5 | Motiva<br>Historia<br>Moore<br>1.4.1<br>1.4.2<br>1.4.3<br>The fur<br>1.5.1<br>1.5.2<br>1.5.3<br>1.5.4 | mputer alphabet        | . 2<br>. 6<br>. 9<br>. 10<br>. 11<br>. 14<br>. 15<br>. 16<br>. 19<br>. 20<br>. 23                                                                      |

| 2   | The 1<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5 | Introdu<br>Ternary<br>2.2.1<br>2.2.2<br>2.2.3<br>Radix o<br>Historie                                  | a of ternary<br>action | <ul> <li>. 29</li> <li>. 29</li> <li>. 30</li> <li>. 31</li> <li>. 32</li> <li>. 34</li> <li>. 36</li> <li>. 36</li> <li>. 37</li> <li>. 38</li> </ul> |

# Contents

|   |       | 2.5.5          | Comprehension                                                     | . 40 |

|---|-------|----------------|-------------------------------------------------------------------|------|

|   |       | 2.5.6          | Cyber-Security                                                    | . 40 |

|   |       | 2.5.7          | Design complexity                                                 | . 40 |

|   | 2.6   | Critique       | e                                                                 | . 41 |

|   | 2.7   | Conclu         | sion                                                              | . 43 |

|   |       |                |                                                                   |      |

| 3 | Mult  |                | RRAM development platform                                         | 45   |

|   | 3.1   |                |                                                                   |      |

|   | 3.2   |                | tate programming                                                  |      |

|   | 3.3   | uMemi          | ristorToolbox: A new tool for experimenting with multi-state RRAM |      |

|   |       | 3.3.1          | Motivation                                                        |      |

|   |       | 3.3.2          | Architecture                                                      |      |

|   |       | 3.3.3          | Experiments                                                       |      |

|   |       | 3.3.4          | Application: Embedded ternary system                              |      |

|   | 3.4   | Ternary        | y memory controller circuit                                       |      |

|   |       | 3.4.1          | Simulation                                                        |      |

|   |       | 3.4.2          | Implementation                                                    | -    |

|   | 3.5   | Conclu         | sion                                                              | . 57 |

|   | Missa | ما برم ما ابر  | EDA for ternary computers                                         | 50   |

| 4 |       |                | <i>,</i> .                                                        | 59   |

|   | 4.1   |                | action                                                            |      |

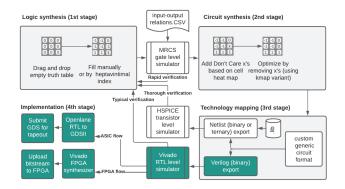

|   | 4.2   | 4.2.1          | A new tool for mixed radix design and verification                |      |

|   |       | 4.2.1          | Motivation                                                        |      |

|   |       | 4.2.2          | Workflows                                                         |      |

|   | 4.3   |                | radix synthesis engine                                            |      |

|   | 4.3   | 4.3.1          |                                                                   | -    |

|   |       | 4.3.1          | Related work                                                      |      |

|   |       | 4.3.2          | Mixed radix synthesis algorithm                                   |      |

|   |       | 4.3.3<br>4.3.4 | Binary coded ternary RTL                                          |      |

|   | 4.4   |                | 2 Balanced Ternary CPU                                            |      |

|   | 4.4   | 4.4.1          |                                                                   |      |

|   |       | 4.4.1          | Balanced Ternary Instruction Set Architecture                     |      |

|   |       | 4.4.2          |                                                                   |      |

|   | 4.5   |                | conversion                                                        |      |

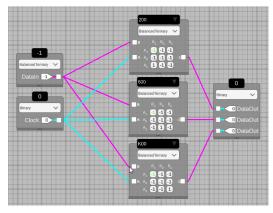

|   | 4.5   | 4.5.1          | Binary to Ternary                                                 |      |

|   |       | 4.5.2          | Ternary to Binary                                                 |      |

|   | 4.6   |                | sion                                                              | -    |

|   | 4.0   | Conciu         |                                                                   | . /7 |

| 5 | Disc  | ussion         |                                                                   | 81   |

|   | 5.1   | Toward         | Is a ternary technology stack                                     | . 81 |

|   | 5.2   | Open q         | Juestions                                                         | . 82 |

|   |       |                |                                                                   |      |

# Contents

| 6   | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 83                                                                                                                                                                                                                                                         |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bil | bliography                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 87                                                                                                                                                                                                                                                         |

| Α   | uMemristorToolbox: Open source framework to control memristors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 113                                                                                                                                                                                                                                                        |

| В   | Automated synthesis of ternary logic functions in CNTFET circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 121                                                                                                                                                                                                                                                        |

| с   | Post-Binary Robotics: Using memristors with ternary states                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 127                                                                                                                                                                                                                                                        |

| D   | Ternary computing; The future of IoT?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 135                                                                                                                                                                                                                                                        |

| Ε   | High speed bi-directional binary-ternary interface with CNTFETS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 143                                                                                                                                                                                                                                                        |

| F   | Ternary and mixed radix CNTFET circuit design, simulation and verification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 151                                                                                                                                                                                                                                                        |

| G   | Additional materialG.1Continuous-time and discrete-time signalsG.2Rebuttal of Buchholz' 9 argumentsG.3A radix compatible form of the CMOS power equationG.4Using the radix economy argumentG.5Overhead calculationG.6Comparing baselines to 58.5% or to 63.1%G.758.5% is an information limit, not a system limitG.8Ternary computers architectures from 2004-2022G.9Experimental 2-trit memristor results using uMemristorToolboxG.10Multi-state RRAM development platform prototypeG.11Getting started with MRCSG.12MRCS LimitationsG.13Ternary algebraG.14Towards a ternary standard cell libraryG.15Combinatorial and sequential building blocksG.16SubcomponentsG.17Online radix conversion tool | <ul> <li>. 161</li> <li>. 162</li> <li>. 164</li> <li>. 166</li> <li>. 167</li> <li>. 168</li> <li>. 169</li> <li>. 171</li> <li>. 173</li> <li>. 174</li> <li>. 176</li> <li>. 176</li> <li>. 179</li> <li>. 181</li> <li>. 185</li> <li>. 194</li> </ul> |

| н   | TNNN 2023: Ternary VLSI with CMOS using MRCS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 199                                                                                                                                                                                                                                                        |

| I   | Tape-outs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 203                                                                                                                                                                                                                                                        |

# **List of Papers**

# Article 1

**S. Bos**, H. Gundersen and F. Sanfilippo, "uMemristorToolbox: Open source framework to control memristors in Unity for ternary applications", *2020 IEEE 50th International Symposium on Multiple-Valued Logic (ISMVL)*, Virtual Conference, Japan, 2020, pp. 212-217, doi: 10.1109/ISMVL49045.2020.000-3.

### Article 2

H. N. Risto, **S. Bos** and H. Gundersen, "Automated synthesis of netlists for ternary-valued n-ary logic functions in CNTFET circuits", 2020 Proceedings of the 61st Conference on Simulation and Modelling (SIMS), Virtual Conference, Finland, 2020, pp. 483-485, doi: 10.3384/ecp20176483

### Article 3

**S. Bos**, J. B. Nilsen and H. Gundersen, "Post-Binary Robotics: Using Memristors With Ternary States for Robotics Control", 2020 IEEE 8th Electronics System-Integration Technology Conference (ESTC), Virtual Conference, Norway, 2020, pp. 1-6, doi: 10.1109/ESTC48849.2020.9229820.

### Article 4

H. Gundersen and **S.Bos**, "Ternary Computing; The future of IoT?", 2021 25th Proceedings of the Society for Design and Process Science (SDPS), Virtual Conference, Norway, 2021, pp. 43-47, link: sdpsnet.org/sdps/documents/sdps-2021/SDPS%202021%20Proceedings.pdf

### Article 5

**S.Bos**, H. N. Risto and H. Gundersen, "High speed bi-directional binary-ternary interface with CNTFETS", 2021 25th Proceedings of the Society for Design and Process Science (SDPS), Virtual Conference, Norway, 2021, pp. 38-42, link: sdpsnet.org/sdps/documents/sdps-2021/SDPS%202021%20Proceedings.pdf

### Article 6

**S. Bos**, H. N. Risto and H. Gundersen, "Beyond CMOS: Ternary and mixed radix CNTFET circuit design, simulation and verification", *2022 IEEE International Symposium on Circuits and Systems (ISCAS)*, Austin, TX, USA, 2022, pp. 80-85, doi: 10.1109/ISCAS48785.2022.9937259.

# **List of Co-supervised Projects**

- 1. Halvor Nybø Risto, "A study of CNTFET implementations for Ternary Logic and Data Radix Conversion", *Master Thesis*, USN, 2020.

- 2. Julian Breivold Nilsen, "Memristor Implementation of a Ternary Storage Circuit", *Master Thesis*, USN, 2020.

- 3. Mehtab Singh Virk, "Memristor Development Platform Dual Source Control For Implementations of Multi-state Memristive Memory", *Master Thesis*, USN, 2022.

- 4. Erika Fegri, "Design of a Balanced Ternary Tri-directional Loadable Counter Using CNTFETs", *Master Thesis*, USN, 2022.

# **List of Figures**

| 1.1  | Performance, Power and Area: 48 years of CPU innovation                        | 4   |

|------|--------------------------------------------------------------------------------|-----|

| 1.2  | The computer technology stack                                                  | 5   |

| 1.3  | The power wall and dark silicon trend                                          | 10  |

| 1.4  | The memory wall                                                                | 12  |

| 1.5  | The memory pyramid                                                             | 13  |

| 1.6  | The EDA wall                                                                   | 14  |

| 1.7  | Trade-offs to increase the radix                                               | 19  |

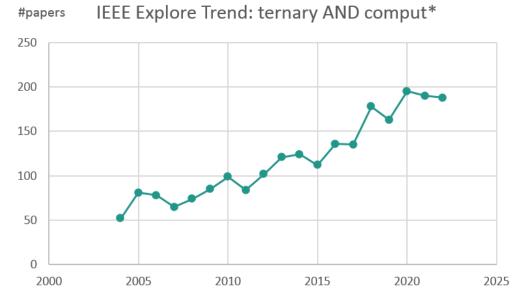

| 2.1  | 20 year IEEE Explore trend for search "ternary AND comput*"                    | 28  |

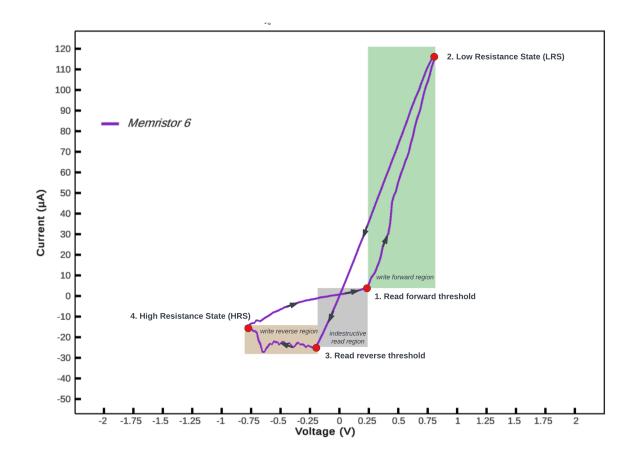

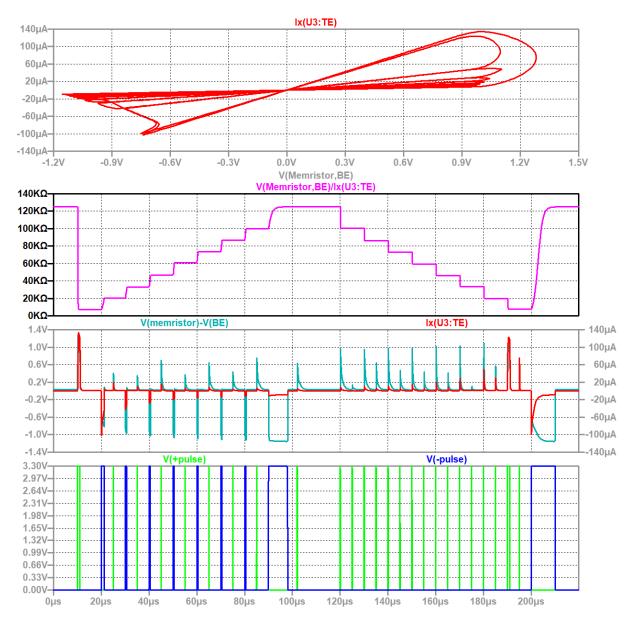

| 3.1  | The 3 regions of voltage-controlled bi-polar memristance programming $\ . \ .$ | 48  |

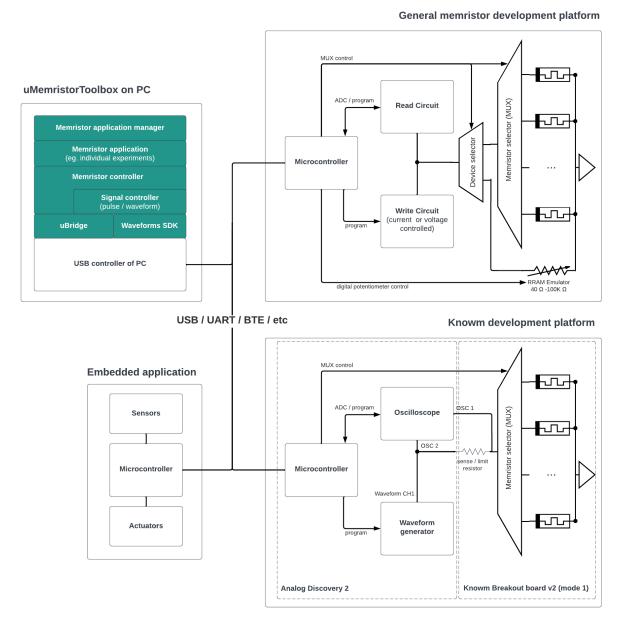

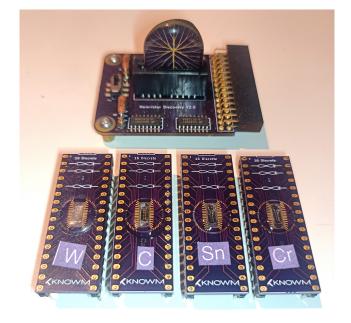

| 3.2  | Architecture of uMemristorToolbox with memristor development platform          | 50  |

| 3.3  | Board check experiment                                                         | 51  |

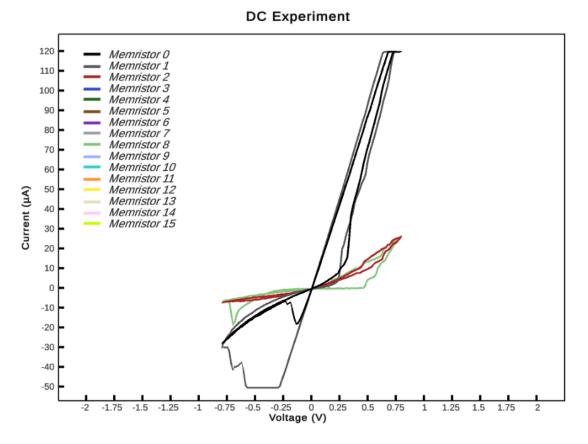

| 3.4  | DC experiment                                                                  | 52  |

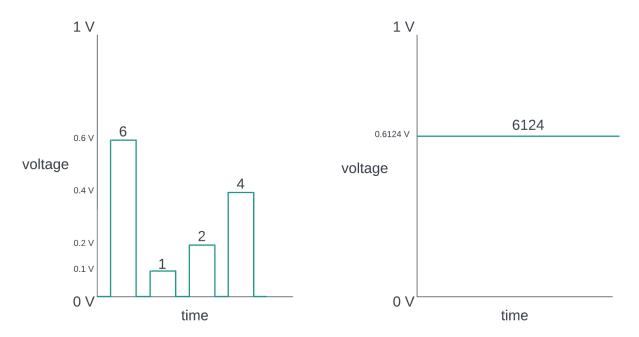

| 3.5  | Random write experiment                                                        | 53  |

| 3.6  | Multi-state programming scheme interface                                       | 53  |

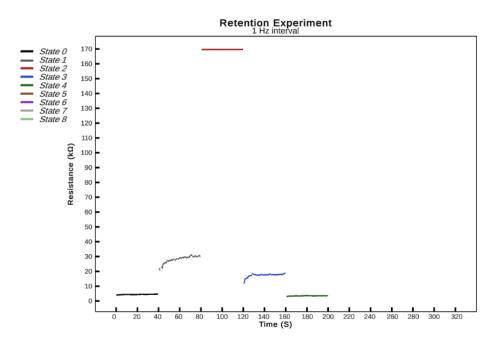

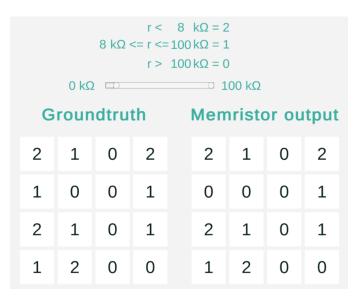

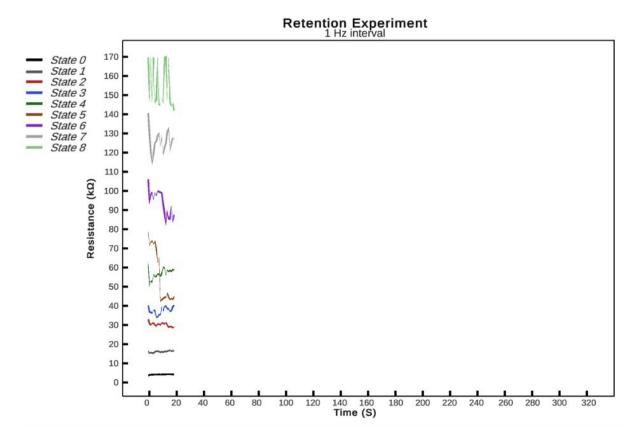

| 3.7  | Retention experiment                                                           | 54  |

| 3.8  | ADC experiment                                                                 | 55  |

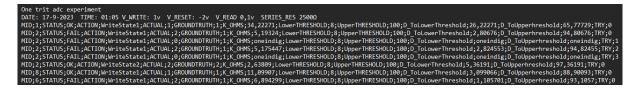

| 3.9  | ADC experiment log                                                             | 55  |

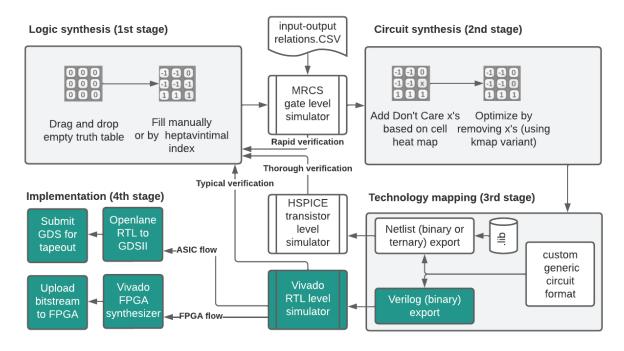

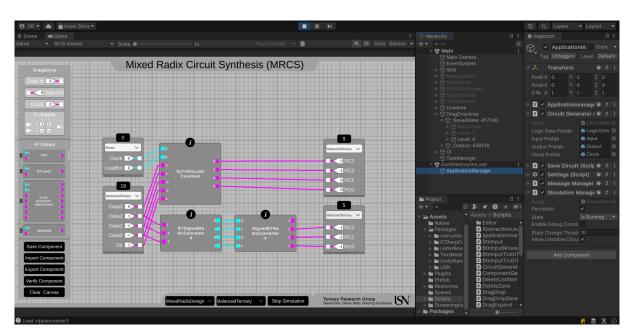

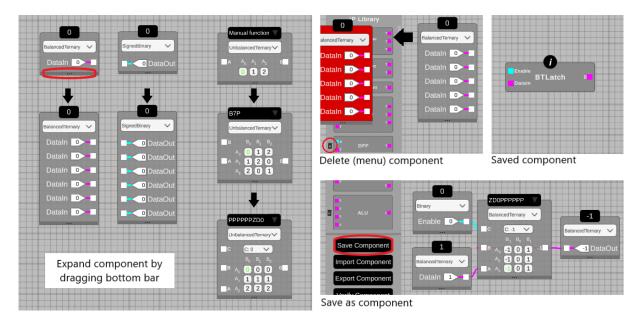

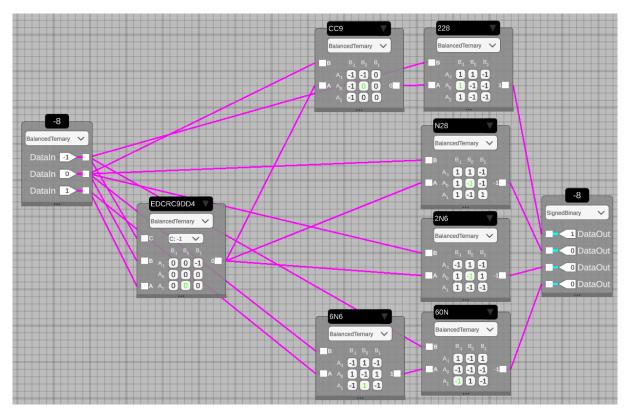

| 4.1  | MRCS architecture and workflows                                                | 61  |

| 4.2  | User interface of the developer version of MRCS                                | 62  |

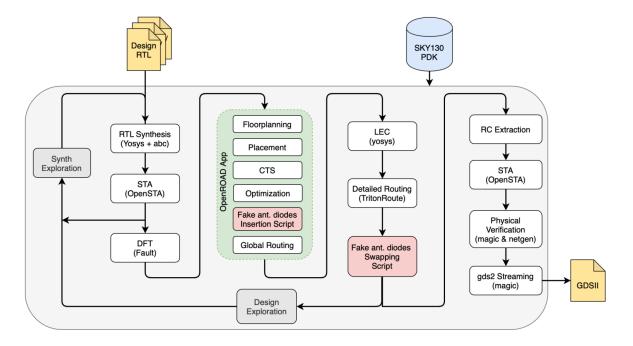

| 4.3  | The RTL-to-GDS ASIC flow from OpenLane                                         | 64  |

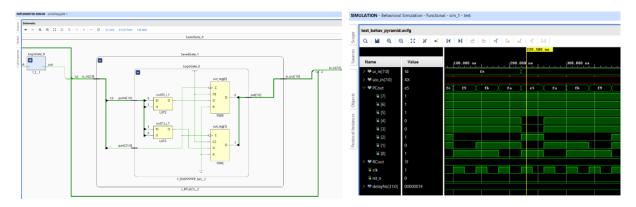

| 4.4  | Schematic and simulation excerpt of a BCT counter in Vivado                    | 65  |

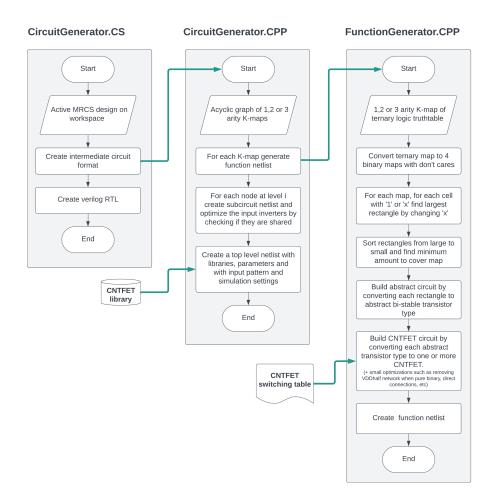

| 4.5  | The mixed radix synthesis algorithm                                            | 68  |

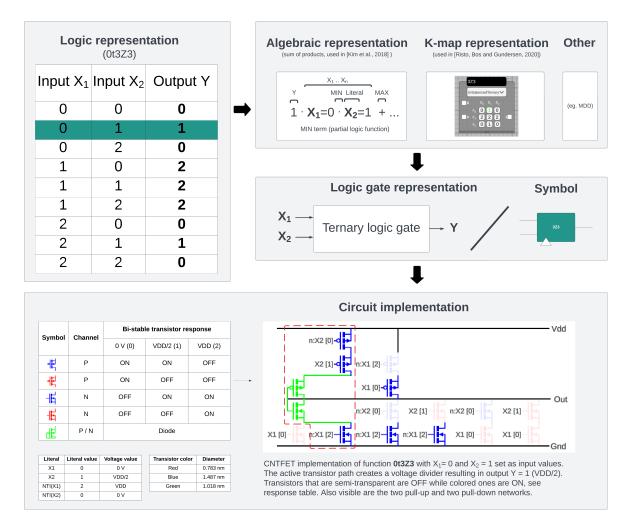

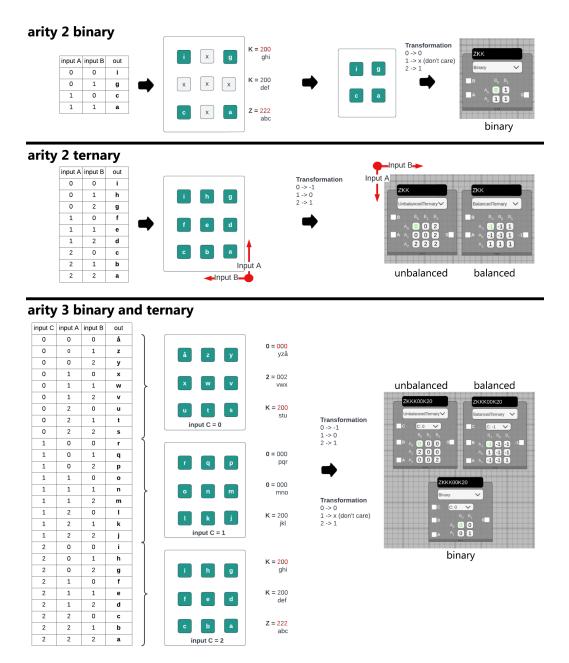

| 4.6  | Logic transformation from truth table to CNTFET implementation                 | 69  |

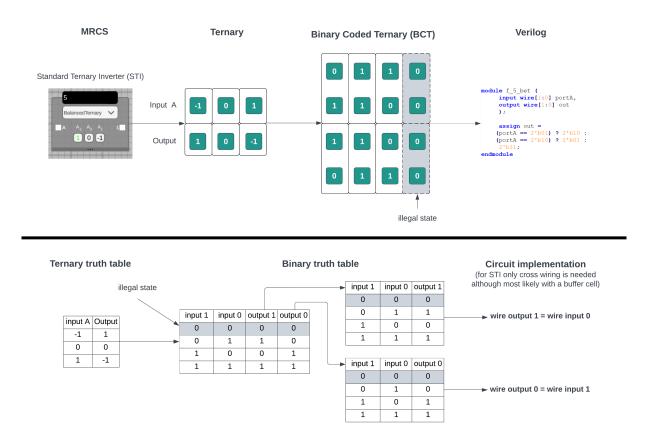

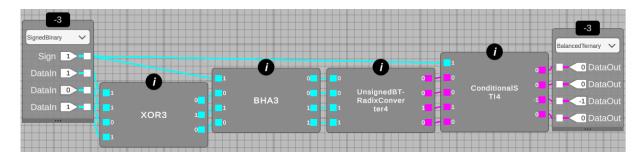

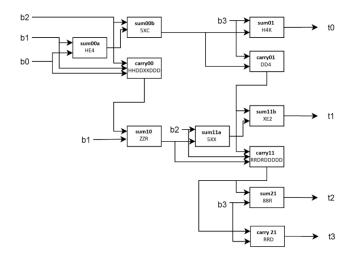

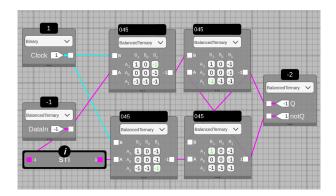

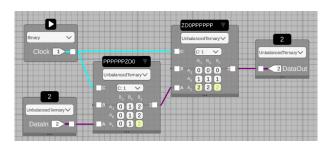

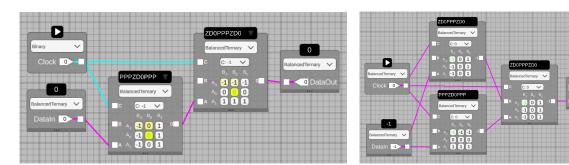

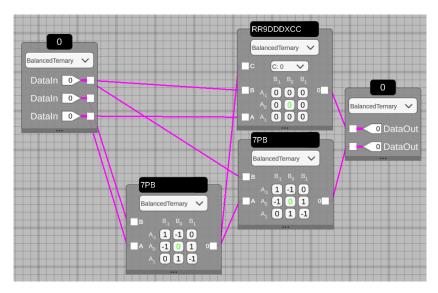

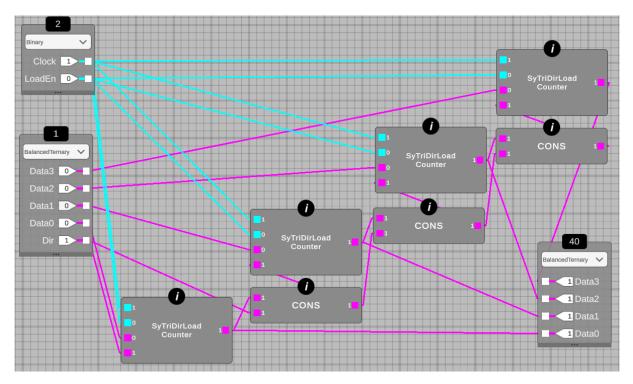

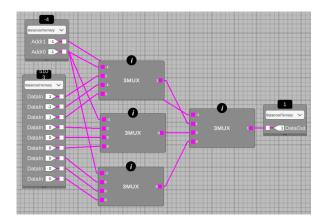

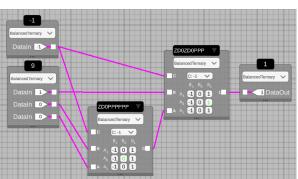

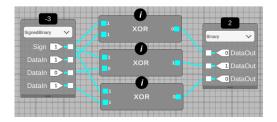

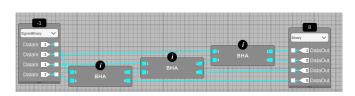

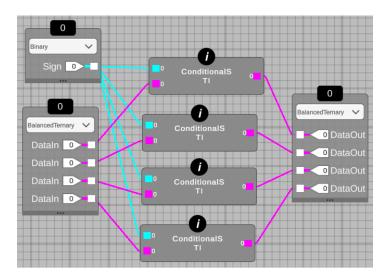

| 4.7  | BCT implementation of an STI made with MRCS                                    | 71  |

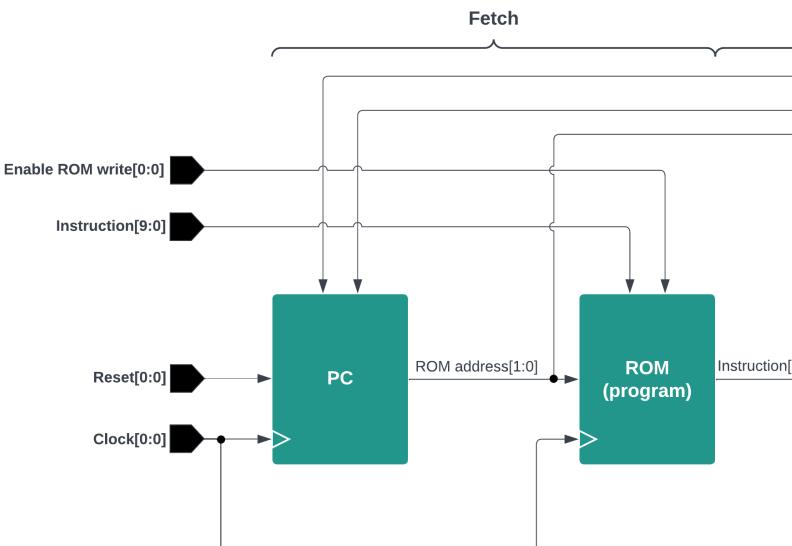

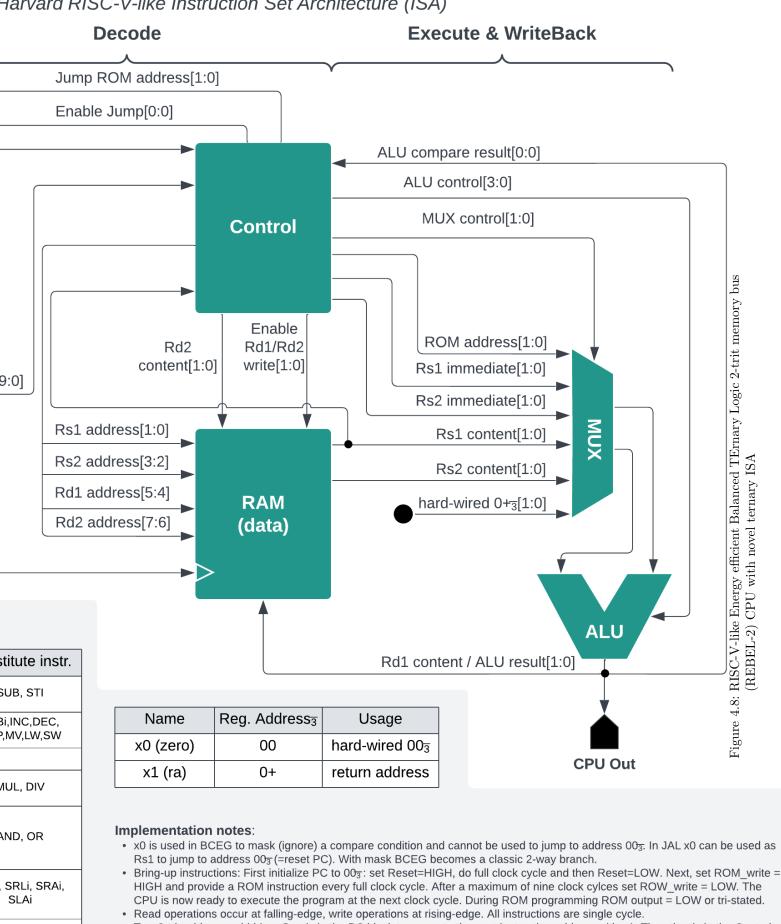

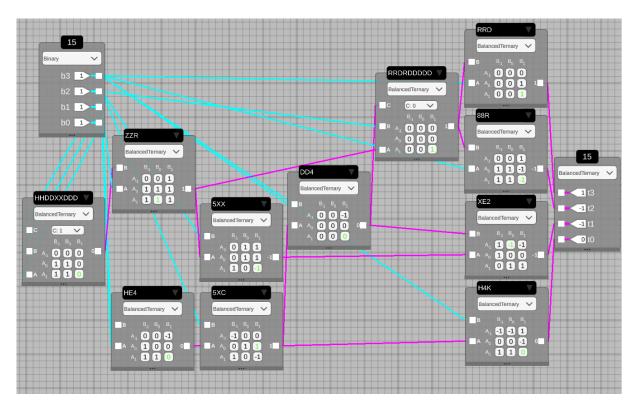

| 4.8  | REBEL-2 balanced ternary CPU and 9-instruction RISC-like ternary ISA .         | 75  |

| 4.9  | 382T 4-bit signed binary to 4-trit balanced ternary radix converter            | 77  |

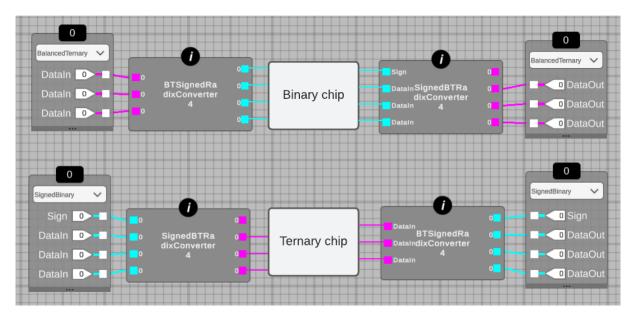

| 4.10 | Radix converter circuits for signed binary and balanced ternary                | 79  |

| G.1  | 1 0 0 0                                                                        |     |

| G.2  | Measurement of nine memristance levels                                         |     |

| G.3  | Simulation of nine memristance levels                                          |     |

| G.4  | A novel multi-state RRAM development platform                                  |     |

| G.5  | First PCB implementation of the multi-state RRAM development platform          |     |

| G.6  | Overview of used memristors                                                    |     |

| G.7  | Mixed Radix Circuit Synthesizer (MRCS) user experience                         |     |

| G.8  | Verilog workaround for BCT with ternary d-latch                                | 176 |

| G.9  | Heptavintimal implementation in MRCS                                               | 178 |

|------|------------------------------------------------------------------------------------|-----|

| G.10 | 28T gated balanced ternary d-latch based on 2:1 MUX                                | 185 |

| G.11 | 46T gated balanced ternary d-latch based on NMIN                                   | 185 |

| G.12 | $54\mathrm{T}$ rising-edge master-slave configuration balanced ternary d-flip-flop | 186 |

| G.13 | 52T rising-edge master-slave configuration unbalanced ternary d-flip-flop          | 186 |

| G.14 | 76T DDR master-slave configuration balanced ternary d-flip-flop                    | 187 |

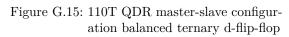

| G.15 | 110T QDR master-slave configuration balanced ternary d-flip-flop $\ldots$          | 187 |

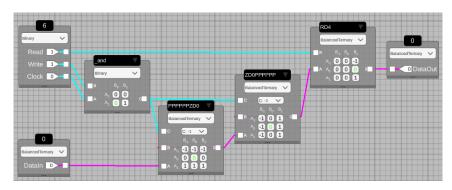

| G.16 | 80T balanced ternary register                                                      | 188 |

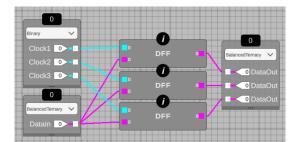

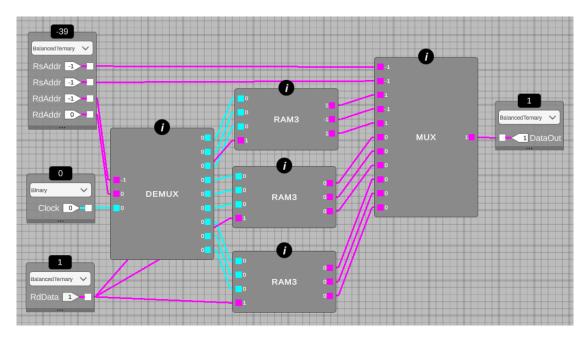

| G.17 | RAM-3 implementation with three d-flip-flops                                       | 188 |

| G.18 | Ternary ROM/RAM                                                                    | 189 |

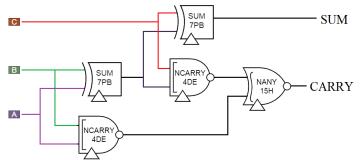

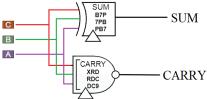

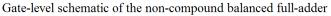

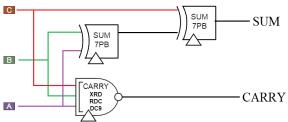

| G.19 | 110T BTA design with SUM-based CARRY                                               | 190 |

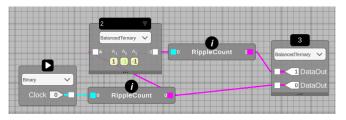

| G.20 | Balanced ternary ripple counter                                                    | 191 |

| G.21 | 2-trit balanced ternary ripple counter                                             | 191 |

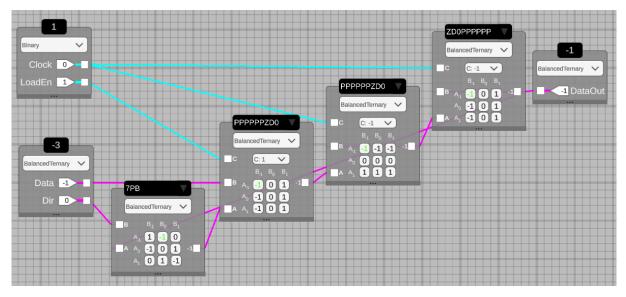

| G.22 | 1-trit synchronous balanced ternary program counter                                | 192 |

| G.23 | 4-trit synchronous balanced ternary program counter                                | 193 |

| G.24 | MUX level 2 implementation                                                         | 194 |

| G.25 | $MUX \ level \ 1 \ implementation \ . \ . \ . \ . \ . \ . \ . \ . \ . \ $          | 194 |

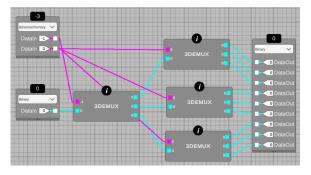

| G.26 | DEMUX level 2 implementation                                                       | 194 |

| G.27 | DEMUX level 1 implementation                                                       | 194 |

| G.28 | binary XOR-3 implementation                                                        | 194 |

| G.29 | binary HA-3 implementation                                                         | 194 |

| G.30 | Conditional-STI-3 implementation                                                   | 195 |

| G.31 | 4-bit unsigned binary to balanced ternary radix converter                          | 195 |

| G.32 | 3-trit balanced ternary to 4-bit signed binary radix converter                     | 196 |

| G.33 | Online radix converter tool                                                        | 197 |

# **List of Tables**

| 1.1 | Relation between discrete radixes, compactness and ambiguity |

|-----|--------------------------------------------------------------|

| 1.2 | Relation between chapters and relevant papers                |

| 2.1 | Radix-2 and radix-3 MAX truth tables                         |

| 2.2 | Heptavintimal (radix-27) encoding                            |

| 4.1 | Variants of binary coded balanced ternary                    |

| G.1 | Bi-stable subset of ternary unary functions                  |

| G.2 | Overview of useful arity-1 building blocks                   |

| G.3 | Overview of useful arity-2 building blocks                   |

| G.4 | Overview of useful arity-3 building blocks                   |

XVIII

# Nomenclature

| $\mathbf{Symbol}$    | Explanation                                         |

|----------------------|-----------------------------------------------------|

| 3VL                  | Three-Valued Logic                                  |

| ADC                  | Analog Digital Conversion                           |

| ALU                  | Arithmethic Logic Unit                              |

| ASIC                 | Application Specific Integrated Circuit             |

| BCD                  | Binary Coded Decimal                                |

| BCT                  | Binary Coded Ternary                                |

| BTA                  | Balanced Ternary Adder                              |

| CMOS                 | Complementary Metal-Oxide Semiconductor             |

| CNTFET               | Carbon Nanotube Field-Effect Transistor             |

| CPU                  | Central Processing Unit                             |

| DRAM                 | Dynamic Random Access Memory                        |

| EDA                  | Electronic Design Automation                        |

| FPGA                 | Field-Programmable Gate Array                       |

| $\operatorname{HRS}$ | High Resistance State                               |

| IC                   | Integrated Circuit                                  |

| ISA                  | Instruction Set Architecture                        |

| LRS                  | Low Resistance State                                |

| MOSFET               | Metal Oxide Silicon Field Effect Transistor         |

| MRCS                 | Mixed Radix Circuit Synthesizer                     |

| MVL                  | Multiple-Valued Logic                               |

| NTI                  | Negative Ternary Inverter                           |

| PCB                  | Printed Circuit Board                               |

| PDP                  | Power Delay Product                                 |

| PPA(C)               | Performance, Power, Area (and Cost)                 |

| PTI                  | Positive Ternary Inverter                           |

| PVT                  | Process, Voltage, Temperature                       |

| RBR                  | Redundant Binary Representation                     |

| REBEL                | RISC-V-like Energy efficient Balanced tErnary Logic |

| RISC                 | Reduced Instruction Set Computer                    |

| RRAM                 | Resistive Random Access Memory                      |

| $\operatorname{RTL}$ | Register Transfer Level                             |

| SPICE                | Simulation Program with Integrated Circuit Emphasis |

| SRAM                 | Static Random Access Memory                         |

| STI                  | Standard Ternary Inverter                           |

| TCB                  | Ternary Coded Binary                                |

| VLSI                 | Very Large Scale Integration                        |

—"At an early point in my thinking about digital computers, I looked at the effects of a change in the base of the number system. How would the structure of a computing machine depend on this choice?"

Prof. John V. Atanasoff, Inventor of the binary computer [1]

—"Computer designers have a common goal: to find a language that makes it easy to build the hardware and the compiler while maximizing performance and minimizing cost and energy"

**Prof. Patterson and Prof. Hennessy**, authors of Computer Organization and Design in [2]

# Introduction

# **1.1** The computer alphabet

For more than 80 years digital computers read, write and "think" in zeros and ones. Remarkably, long and complex patterns of just these two symbols control computers to land a spaceship on the moon, forecast the next Aurora Borealis or provide endless digital entertainment. Computers have propelled us from the industrial age to the information age and these two symbols are at the center. In contrast, most people perform mental calculation with 10 symbols, the digits 0-9. English speakers use an alphabet of 26 symbols. Ancient Greek numerals combined the two symbol sets as each number corresponded to a letter in the alphabet. The fact that most scholars associate  $\alpha$  (alpha) with one or first is a direct consequence of this.

The two-letter computer alphabet structures a computers lowest level language and is known as *binary*. In mathematics and computer science the number of unique symbols in a set to represent a number is called the base or radix (Latin: root) and is analog to the amount of letters in an alphabet. Binary is thus radix-2, ternary with three symbols is radix-3 and denary with its ten symbols 0-9 is radix-10. To express a large number with a set of smaller numbers, a system of transformation rules and notation is required. The ancient Greek numeral system was superseded by the the Hindu-Arabic positional numeral system as it had several advantages. It introduced symbols exclusively for numbers and used positions for order of magnitude. For example, the decimal number "9" (nine) uses one position, while the decimal number "10" (ten) uses two. Crucially, the symbol pattern "10" can be interpreted as something other than a number and is the reason why modern computers should be considered symbol or computer language processors rather than arithmetic processors. Patterson and Hennessy wrote [2]:

"No matter what the instruction set or its size — RISC-V, MIPS, ARM, x86— never forget that bit patterns have no inherent meaning. The same bit pattern may represent a signed integer, unsigned integer, floating-point number, string, instruction, and so on. In stored-program computers, it is the operation on the bit pattern that determines its meaning."

In Origins of Language [3] Tomasello wrote that human language differs from other animal species in two main ways: humans use symbols and grammar. Central in human language are the various writing systems [4], a system for recording and conveying messages such as the alphabet. Man [5] claims the alphabet to be "one of humanities greatest ideas". In alphabetic writing systems the smallest units for causing a contrast in meaning are called *graphemes* for symbols. For the physical representation of speech as sound patterns the smallest units are called *phonemes*. Both Pae [4] and Crystal [6] write (paraphrased) "in a perfect regular system there is one grapheme for each phoneme". Such a system allows compact encoding of the language while at the same time offer great expressive power needed for labelling new concepts [4]. Alphabetic writing system are recognized as the most economic and versatile of all writing systems [4]. The alphabet size of human languages varies from 11 in Rotokas to 74 letters in Khmer [6]. In modern computers graphemes are depicted as the digits 0 and 1 which correlates 1:1 to their physical representation often expressed as a range of voltage levels such as  $0 \text{ V} - V_{DD}$  for symbol 0 and  $V_{DD}$  for symbol 1. Other electrical quantities can be used as physical representation such as resistance as well as other energy domains such as mechanical, thermal and optical.

Power is the number one design constraint for designing computers [7], [8]. Interestingly, modern computers spend 1000x more energy on communication than on computation and this is increasing with every new generation of smaller chips [9], [10]. If language and its structure is so efficient for humans why did the pioneers of electronic computing Atanasoff, von Neumann and others advocate for binary? Does a richer computer alphabet, a higher radix, have the same benefits as it does for humans? If so, then uprooting this foundation of computing is a radical paradigm shift that effects all digital computers.

# **1.2** Motivation and scope

The question of radix, namely choosing the alphabet size, has been prevalent since the ancient predecessor of the digital computer; the abacus. The Sumerian version of this mechanical counting device used radix-60 around 2700 BC while other cultures adopted radix-10 [11, p. 11]. The choice for radix-10 for addition and subtraction was based on the 10 human fingers [12]. The importance of choosing a radix can be observed in table 1.1, where the numbers 0-10 are encoded in radix-1, radix-2, radix-3, radix-8 and radix-10. The formula for encoding any positive number n in radix form is Eq. 1.1 [13]. The solution is unambiguous only for that radix.

$$n = x_p * r^p + x_{p-1} * r^{p-1} + \dots + x_0 \tag{1.1}$$

Where radix r and position p are non-negative integers and  $x_i \in 0..r - 1$

| Decimal Number | Radix          |            |         |                |  |

|----------------|----------------|------------|---------|----------------|--|

| (Radix-10)     | Radix-1        | Radix-2    | Radix-3 | Radix-8        |  |

| 0              | Ø <sub>1</sub> | 02         | 03      | 08             |  |

| 1              | 01             | 12         | 13      | 18             |  |

| 2              | 001            | 102        | 23      | 28             |  |

| 3              | 0001           | 112        | 103     | 38             |  |

| 4              | 00001          | $100_{2}$  | 113     | 48             |  |

| 5              | 000001         | 1012       | 123     | 5 <sub>8</sub> |  |

| 6              | 0000001        | 1102       | 203     | 6 <sub>8</sub> |  |

| 7              | 00000001       | 1112       | 213     | 7 <sub>8</sub> |  |

| 8              | 000000001      | $1000_{2}$ | 223     | 108            |  |

| 9              | 0000000001     | $1001_{2}$ | 1003    | 118            |  |

| 10             | 00000000001    | $1010_{2}$ | 1013    | $12_{8}$       |  |

Table 1.1: Relation between discrete radixes, compactness and ambiguity

Less positions are needed for the same information when using higher radixes (plural of radix). In practice positions need to be physically implemented as a type of switch such as a transistor or memory cell. Each switch uses space, has a transition time, consumes energy and produces heat when switching. It also has design and fabrication costs tied to it. These properties are captured in the industry standard metric Performance, Power, Area and Costs (PPAC). The implications of radix are directly tied to the amount of positions, thus amount of switches needed. If a switch can process more symbols while having the same dimensions information density increases. Fewer switches for the same functionality can be translated into benefits such as smaller chips, reduced power consumption and power dissipation as heat, increased chip performance and decreased costs.

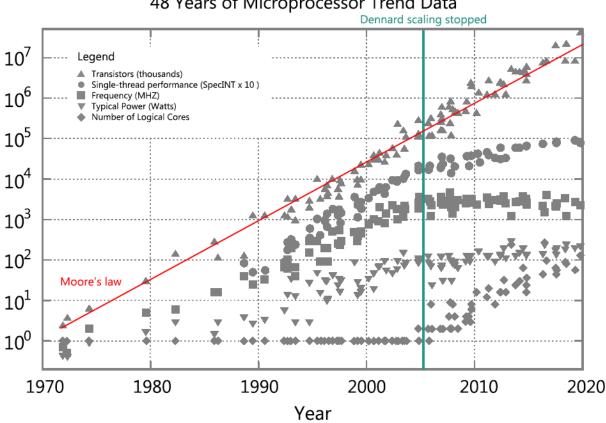

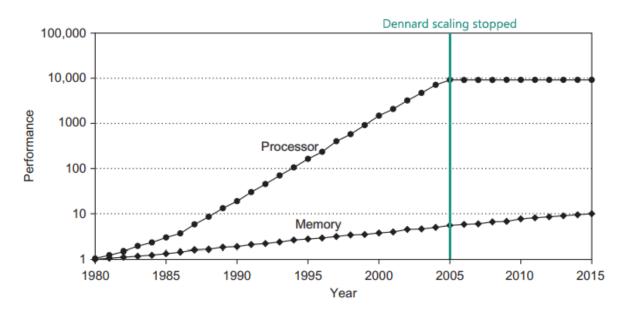

A nearly 50 year trace of performance, power and area of the central processing unit (CPU) is shown in Fig. 1.1. A similar trace for costs can be found in [15], showing 7 decades of decline of cost/transistor in the same period. A more detailed analysis of the cost trends can be found in [16]. The transistor density trend in Fig. 1.3 shows that technically Gordon Moore's observation known as "Moore's law" [17] of doubling transistor density every two years and reducing cost by half in the same period was mostly accurate for this period. Moore's law has become a roadmap for the semiconductor industry although the actual driver was Dennard's scaling law [18]. After this scaling stopped around 2005, advances in performance, frequency and power all stalled. This will be discuss in more depth in the Moore's Curse section below.

48 Years of Microprocessor Trend Data

Figure 1.1: Performance, Power and Area: 48 years of CPU innovation. Adapted from [14]

Nature's solution to information processing, the brain, is both compact and about 5-6 orders of magnitude more efficient than modern computers [10]. Bullock et al. [19] describes the difficulties of modelling the brain as discrete cellular switches with binary action potential (AP), the neuron doctrine:

"In 1959, it was realized that much of the information processing by neurons involves electrical events that are graded in amplitude and decay over distance rather than all-or-nothing electrical spikes that propagate regeneratively".

The brain-inspired computing paradigm *neuromorphic computing* acknowledges that binary digitization is inefficient and uses analog and binary signals - a mixed signal architecture [20]. This includes multiple-valued logic or mixed radix signals [21]. A paper by Sengupta et al. [22, p. 748] mentions that "neurons produce a myriad of APs with different shapes and varying heights and width". They also show an example of an AP with a similar voltage level but different current levels [22, p. 747] indicating multiple values.

Higher radix computing is studied under the umbrella term multiple-valued logic (MVL). Synonymous terms are m-valued, p-valued, multi-valued, many-valued, multi-level and multi-valent logic. Related terms found in literature to indicate digital technology with more than 2 discrete levels include multi-bit, multi-state, multi-stable, complex states and post-binary. Radix-3 (base-3) or three-valued Logic (3VL) is the first radix in the MVL family and is synonymously called ternary, trinary or tri-stable in literature. Many heavyweights in the computer science field including Shannon [23] and Knuth [24] have recognized the unique arithmetic properties of balanced ternary (symmetrical around zero) for computing. Radix-3 is the first radix with the symmetry property. Ternary is the closest integer to optimum e ( $\approx 2.71$ ) discussed in the Fundamental limits section below. Higher radixes give a higher information density but the economy has a diminishing return. Radix-3 is also the minimum radix to higher-order logic with three truth assessments: True, False, Unknown. Ternary logic stands in contrast to Aristotelian/Boolean logic that can only assign True or False. The classical bivalent view is also called *tertium* non datur or the law of the excluded middle. However, this principle limits reasoning about the world tremendously as no future or unverifiable statements are possible. Some statements might not be true or false *now*, but might be *later*.

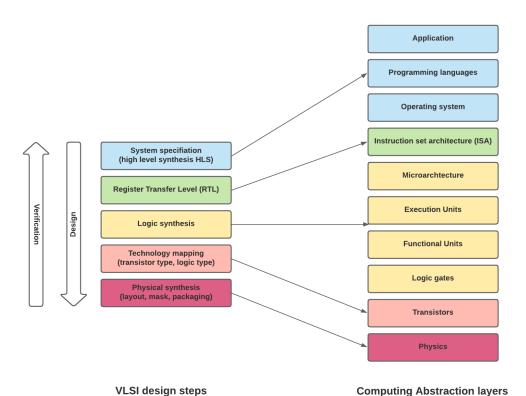

Figure 1.2: The computer technology stack. Layers of abstraction transform atoms into applications. Design and verification steps are supported by EDA tools and flows.

The choice of radix has effect on every aspect of a computer; the hardware and software. The computer technology stack in Fig. 1.2 shows the many abstraction between the individual atoms and the application that interacts with them. Each abstraction is designed and verified by Electronic Design Automation (EDA) tools and elaborate workflows. In many treatments on computing such as [25], the first concept assumed or explained is the binary radix. This work re-investigates the feasibility of radix-3 computing after the first (and last) commercial ternary computer, the 1958 Russian Setun [26]–[28]. Emphasizes is put on EDA tooling and workflows for ternary Very Large Scale Integration (VLSI). The explored transistor technologies are limited to Carbon Nanotube Field-Effect Transistors (CNTFET) and Metal-Oxide-Field-Effect Transistors (MOSFET) for ternary logic. Complementary MOSFETs are made with a CMOS process and is the industry standard to create high transistor density binary logic chips. CNTFET are a potential candidate to replace MOSFETs [29] and have unique properties to create ternary signals [30]. They have been demonstrated to be compatible with CMOS [31]–[33]. For ternary memory commercially available Resistive-RAM (RRAM or ReRAM) is explored. RRAM is commonly known as memristors [34]. Memristor are a potential candidate for beyond CMOS devices and have desirable properties for MVL such as multiple states per devices [35], [36].

# 1.3 Historical evolution of binary computing

Early computers were designed to be highly specialised arithmetic machines. They excelled in solving large systems of equations for applications like missile guidance, decryption and atomic bomb calculations [37], [38]. Although the term digital did not exist in the 1940's, the input and output data on digital computers was done in the radix-10 Hindu-Arabic positional numeral system and could be interpreted by human operators without conversion. A brief primer on digital and analog signals in the context of radix is shown in **Appendix G.1**. The transition from radix-10 (denary) to radix-2 (binary) computer alphabets is due to a long chain of events described in detail in [1], [24], [38], [39]. For example the ongoing evolution of the bi-stable transistor from point-contact to MOSFET is the technological cornerstone of binary's success for 75 years [40]. The concept of encoding information in two symbols and performing arithmetic with them has an even longer history and was used in various ancient cultures [41]. A more complete treatment of the discovery and history of binary for computing can be found in [39], [41]-[43]. They include references to events leading up to the invention of the electrical binary computers such as Jacquard's machine using (binary) punched cards to program a loom in 1804, Babbage's mechanical computer in 1837 and George Boole's logic algebra that expanded Aristotlean logic in 1847. In this section five historical papers are discussed that led to the mass adoption of binary in electronic computers. They are treated in chronological order from the 1930's and onwards.

The first landmark paper was Alan Turing's 1936 "On computable numbers" [44]. This theoretical machine used unary encoding ("tally counting") and laid the mathematical foundation for computing. In the paper Turing described *universal machines*, machines that could do more than arithmetic and are akin to general purpose symbol processors. Turing and von Neumann had met on several occasions and this paper is quoted to have inspired von Neumann [45, p. 10]. Turing also proposed and constructed practical computers, most notable the 1945 ACE [37] which was based on his 1936 paper.

The second influential paper was the Master thesis written by Claude Shannon [46] in 1937. This work laid the foundation for EDA tools describing in detail a link between Boolean algebra and circuit implementation using binary switches. For example, he showed how to synthesize complex functions such as a n-bit full adder with sum and carry signal into a electrical circuit.

The third key paper is a manuscript written by John Vincent Atanasoff [47] who through his pioneering work between 1935 and 1941 is considered by some to be the father of the modern computer [48], [49]. He explicitly investigated the role of radix for building computers [38, p. 307]:

"Considerable thought was given tot the design of a computing mechanism that would simultaneously be simple, fast and accurate. After many attempts to devise a conventional computing mechanism with these properties attention was turned to the possibility of changing the base of the numbers in which the computation is carried out. For a short time the base one-hundred was thought to have promise but a calculation of the speed of computation carried out in terms of this base showed it to be so low as to make its use out of the question. However this same calculation showed that the base that theoretically gives the highest speed of calculation is e, the natural base. But the base of numbers must be an integer, and a further calculation indicated that the bases two and three yield number systems with the same and consequently the highest speed of calculation. The choice of the base for a system of numbers to be used for mechanical calculation."

Together with his PhD student Clifford Berry he build the first electronic binary computer, the Atanasoff-Berry-Computer (ABC). The computer featured many engineering novelties such as electronic switching using vacuum tubes for logic and charge-based storage with capacitors for memory [38]. These two devices were designed to be inherently bi-stable as each device is capable of representing 2 stable states. With them he discovered the devices to implement radix-2 efficiently in computers. It was also very close to the theoretical optimum e. Atanasoff was not aware of Boolean algebra and Shannon's thesis on binary circuit design with Boolean algebra [50].

The fourth seminal paper was a report by John von Neumann on the working details of a new computer architecture [51]. The foreword by Godfrey mentions that this paper inspired the first generation of computer engineers. Von Neumann joined John W. Mauchly's project as advisor to build the successor to the radix-10 ENIAC, the radix-2 EDVAC. Mauchly visited Atanasoff's lab during ENIAC's development and wrote to Atanasoff he was considering to implement his digital approach. Mauchly denied being inspired by it though. A court ruling ended a patent dispute, finding the ENIAC a derivative of the ABC [1], [48]. More controversially, von Neumann wrote a preliminary report based on the internal discussions of the radix-2 EDVAC computer without referencing Mauchly and others. In the same year he published a report with Goldstine and Burke [52] discussing the role of binary. The main argument favoring binary he gave was based on pragmatics [51]:

"Thus, whether the tubes are used as gates or as triggers, the all-or-none, two equilibrium arrangement are the simplest ones. Since these tube arrangements are to handle numbers by means of their digits, it is natural to use a system of arithmetic in which the digits are also two-valued. This suggest the use of a binary system. The analogs of human neurons are equally all-or-none elements."

It is worth noting that this last sentence was based on the 1943 paper by McCulloch-Pitts [53]. This paper was the first computational model of the human brain and was proven quite early to be far too simplistic and inaccurate [19].

The fifth paper considered to be influential for the mass adoption of radix-2 in modern computers is by Werner Buchholz [12]. The 1955 "Fingers or Fist" paper is one of the few academic works that focussed on radix comparison. Buchholz worked for IBM and collaborated with Gerrit Blaauw on computer architectures [54]. Blaauw is the "inventor" of the 8-bit byte [55] and lead architect of the IBM/360, one of the most successful mass-produced computers. In the Fingers (radix-10) or Fists (radix-2) paper, Buchholz wrote that radix-2 was superior to radix-10 for nine reasons. Buchhold cited von Neumann's EDVAC paper for several of the reasons. Important is that for many of the arguments, radix-10 was implicitly assumed to be implemented with bi-stable devices (and encodings such as binary coded decimals, bi-quinary, etc) as this was the most efficient implementation. A brief analysis of the 9 arguments can be found in the **Appendix G.2**.

Lastly, work with less focus on structured radix comparison from this era was "Arithmetic Operation in Digital Computers" from 1955 by Richards discussing radix-2, radix-3 and radix-10. They mention that the ternary system was seriously considered. An important quote from that work is [56, p. 15]:

"When the difficulties which are encountered in the design of a ternary computer are combined with the dearth of ternary computer components and with the difficulties in adapting the system to applications where the decimal system is already entrenched, it appears that the disadvantages of the ternary system with positive and negative coefficients substantially outweigh the advantages."

Shannon's 1950 "A Symmetrical Notation for Numbers" [23] discussed the properties of symmetrical radixes around zero (such as radix-3, radix-5, etc) and mentioned that some of the benefits disappear when for instance radix-3 is used with asymmetric arithmetic. This topic will be relevant in Chapter 2 on balanced vs unbalanced ternary. The third honorable mention on radix comparison is the 1950 work by the Engineering Research Associates Staff who briefly mention symmetrical radix-3 (balanced ternary) adder designs [57, p. 287] but do not divulge in a comparison to binary. The first electrical ternary computer, the 1958 Russian Setun [26]–[28] actually used binary coded ternary (2 bits for 1 trit) [58] and will be discussed in Chapter 2. This computer had some commercial success, unique features and piqued interest from the USA [58] but could not influence the path towards binary dominance. Radix-2 was the best option because the radix implementation was done with bi-stable binary logic and memory devices. Implementing other radixes with them would make them economically inefficient.

Readers that are interested in historical events after the origins of binary computers are referred to the IEEE Annals of the History of Computing. Central is the focus of miniaturization of bi-stable transistors after the invention of integrated circuits. This became the cornerstone for binary computers.

# 1.4 Moore's curse: 3 scaling walls

Moore's law has inspired continuous device-centric scaling for over 50 years and counting through a multi-disciplinary effort involving both academia and industry. Revenue in the global semiconductor industry has grown to 700 billion USD in 2023 [59]. The writing on the wall started after Dennard scaling [18] stopped around 2005. Transistors scaled physically afterwards, but other properties such as power consumption did not. The relentless exponential growth by doubling transistor density every two year is unusual compared to other industries [60]. Like any exponential growth curve it is bound to end. Perhaps more importantly, the continued focus on the area metric masks technical debt. Moore's law has become Moore's curse [60]. Performance and power show marginal growth of 3% for nearly 20 years (see Fig. 1.1) and [2, p. 44]. The 2022 Industry Roadmap for Devices and Systems (IRDS), a leading set of frequently updated white papers [61], [62] that discuss the state of semiconductor research in industry and academia, identify many challenges that are deemed critical for further scaling. This includes the suggestion to explore higher radixes [62, p. 4]. Three categories of challenges relevant for this thesis are highlighted: power consumption, memory access and EDA tooling and workflows. All three challenges can be considered corollaries of Moore's Law.

### 1.4.1 Power wall

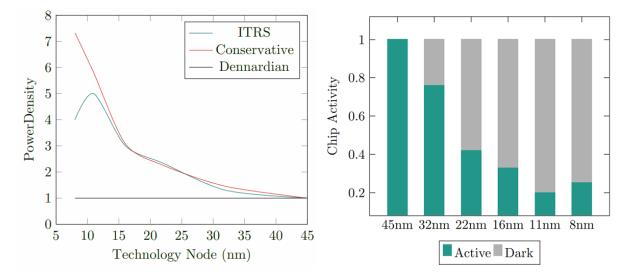

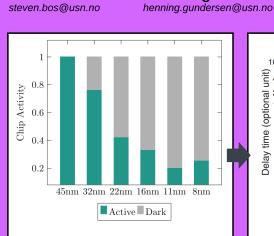

Figure 1.3: (Left) The power wall, a post-Dennard power density trend. (Right) Dark silicon: projected transistor activity over technology nodes. Both plots adapted from [63]

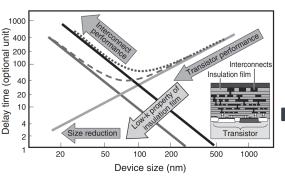

The power wall [64] refers to the increasing problem of power delivery and heat dissipation due increased transistor density (see Fig. 1.3). The problem is not limited to billions of fast switching transistors. Each transistor is wired up from its gate, source and drain terminals. The increasingly lengthier interconnects of these transistors also dissipate heat during switching. The power consumption equation is discussed in **Appendix G.3** as it is slightly more complex for higher radix signals. Power is considered the number one design constraint [8] and limits both low-power and high performance computers [64]. The effect of the power wall visible in Fig. 1.1 shows limited single threaded performance increase after 2005. Dennard's paper [18] observed two major scaling rules. The first was related to scaling interconnects mentioning that "Scaled interconnects provide roughly constant RC delays because the reduction in line capacitance is offset by an increase in line resistance" [65]. This means that as interconnects became smaller no speed was gained. A detailed analysis of the interconnect problem or "interconnect wall" in relation to scaling can be found in [66]. The second scaling rule was about transistor scaling, a formula to improve all PPA metrics. The importance of it is perhaps best phrased in Bohr's retrospective paper on Dennard scaling mentioning that "as transistors get smaller, they can switch faster and use less power" [65].

Unfortunately the second scaling rule is no longer feasible which marks the end of Dennard scaling. The rule to double transistor density required a reduction of transistor dimensions by a factor of 0.7 and keep power density constant by reducing supply voltage by the same factor. To reduce the supply voltage while maintaining a good  $I_{ON}/I_{OFF}$  ratio at room

temperature the voltage threshold needs to scale down proportionally. For 30 years this could be done by scaling the gate oxide thickness. As gate oxide thickness approached just 5 silicon atomic layers in the early 2000's, transistors couldn't switch off properly anymore resulting in constant leakage current [65]. Multiplied with billions of transistors this small leakage became significant - even when doing no computation. This phenomenon is called direct tunneling. Other issues are known as short-channel effects (SCE) [67, p. 496-504] [68] and play an increasing role in sub 100 nm technology nodes [69].

Power density is defined as  $D = P_{device} / Area_{device}$ . With the ongoing scaling of  $Area_{device}$ and without Dennard scaling of  $P_{device}$ , power density keeps increasing every technology node (see Fig. 1.3). Transistors operating at 1.5 THz  $f_{max}$  have been demonstrated [70]. In practise a fraction of that maximum frequency can be used for switching activity. Operating at lower frequencies to curb power is called dim silicon. The phenomena of disabling transistors is called dark silicon [63] and has been increasing every technology node (Fig. 1.3. Markov also classifies grey silicon, which are additional non-functional but power consuming structures such as repeater gates that are needed because the interconnects have become too short [7]. Repeater insertion, both the amount and placement, is an increasing problem with every node [71]. On 130nm interconnects including repeaters can form 50% of the dynamic power consumption and leakage power [71]. Repeaters are critical for minimizing clock skew in the clock tree network (CTN) and signal integrity. Ideally these repeaters are placed in higher metal layers where there is less interconnect congestion and would reduce the amount and placement problems [72]. Currently, repeater gates share the same physical layer as the other logic gates. Device utilization is considered a main challenge in the 2022 IRDS roadmap [61, p. 3]. If power consumption goes unchecked temporary or permanent thermal related defects arise. Defects include lifetime, performance and reliability.

Various approaches have been discussed in literature [8], [64], [73], [74] to reduce power consumption and curb heat dissipation in hardware. At the system level the most common strategy to mitigate heat dissipation is to use active cooling solutions. Good heat transfer reduces leakage current as the thermal noise floor is lowered [75]. A cool CPU allows higher switching activity  $\alpha$  and  $F_{clk}$  because electron mobility is negatively affected by temperature. Active cooling require power drawn from the system and can be significant (for instance 40% in supercomputers [75, p. 10]). Recent innovations in the field include MEMS-based active cooling [76]. The rate of progress in heat transfer research cannot cope with the increase in power density [75] due to Moore's law, necessitating novel approaches at lower abstraction levels.

# 1.4.2 Memory wall

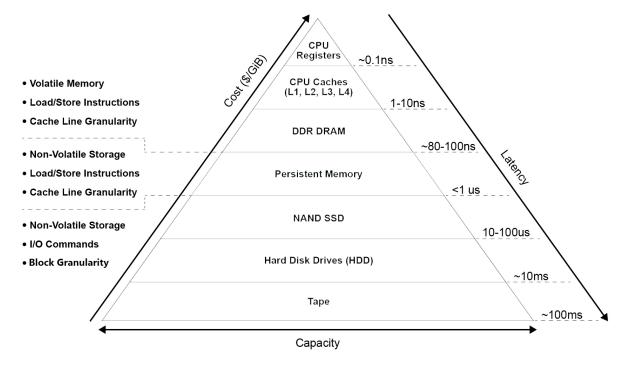

The *memory wall* [77]–[79] is the latency and bandwidth gap between on-chip data processing and off-chip data retrieval from dynamic RAM (DRAM), see Fig. 1.4. It is also

Figure 1.4: The memory wall. The gap between retrieving data and operating on it. Adapted from [78]

called the von Neumann-bottleneck [80]. The gap stabilized as frequency couldn't scale after Dennard scaling stopped. However, in technology nodes after 10 nm Moore's law seems to saturate for both DRAM [81] and static RAM (SRAM) [82] scaling meaning that the gap might widen further again. For DRAM 50% more processing steps are needed to move from technology node 2X to 1Z and include costly double and quadruple patterning steps [81]. Both logic cells and memory cells suffer from lower supply voltages and increased interconnect resistance as a result of scaling. Worse, for memory cells the decrease in supply voltage and increase in interconnect resistance degrades SRAM and DRAM performance [81], [83] making it harder to scale voltage further. The different technical requirements for logical and memory is part of the reason why DRAM is made on much older technology nodes [81, p. 1386]: "The low leakage is required to prevent the discharging of the capacitor, and the high ON-current is expected to write the data in a short time".

The architecture of a conventional computer is unchanged since Burks, Goldstine and von Neumann's paper [52] and consists of 5 components; datapath, control, input, output and memory. The datapath and control components are together called the processor[2]. Memory physically located on the same die as the processor has the shortest path to the processor and is called *cache* or on-chip memory. This type of memory shares the die area with digital logic blocks and analog blocks. The area SRAM occupies depend on the product but even processor's from 2004 like the Intel Itanium 2 6M can occupy 50% [84] with L2/L3 cache. In terms of power SRAM can consume 25-50% of the total power [78]. The further the memory is from the processor the more power and time it takes to retrieve or access the data, see the memory pyramid in Fig. 1.5.

#### 1.4 Moore's curse: 3 scaling walls

Figure 1.5: The memory hierarchy and latency pyramid. Adapted from [86]

Since 1975 on-chip memory is high density SRAM while the nearest off-chip memory is DRAM [78]. SRAM is typically made with 6 transistors, a 6T-SRAM cell [83]. DRAM is made with 1 transistor and a capacitor, a 1T1C-DRAM cell [81]. To improve latency both SRAM and DRAM cells use pre-charge circuits [85] such that the voltage swings are halved or reduced. The average memory access time, the latency, is data dependent as data in cache doesn't require hundreds of clock cycles to fetch from DRAM [10]. A 32-bits memory load also costs 1300x more energy then a 32-bits ALU operation on a 45nm process [10], a significant increase from 260x at 130nm. Electron transport is more expensive than electron manipulation. The SRAM and DRAM average access time is dependent on cache access time, miss rate and miss penalties [78].

The stored-program concept by von Neumann [51] is the architectural reason for the bottleneck between memory and the processor. Both the Harvard and von Neumann architectures define that computers cannot perform operations directly on memory. Using a memory hierarchy like in Fig. 1.5, data is stored and retrieved from memory and moved to a central processing unit. All conventional computers use this architecture and thus implement some sort of fetch-execute-writeback mechanism. New memory paradigms such as compute-in-memory (CIM) or processing-in-memory (PIM) using novel memory cells such as RRAM and a higher radix can break this paradigm [80], [87].

#### 1 Introduction

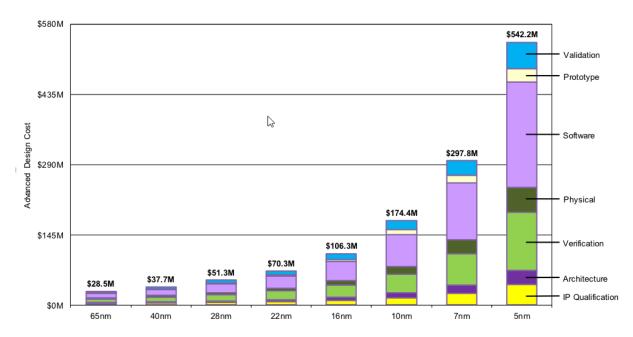

#### 1.4.3 EDA wall

Figure 1.6: The EDA wall. The exponential increase of chip design costs with transistor density. From [88] (original data: IBS)

The exponential increase in electronic design automation (EDA) related cost every technology node [88]–[91] can be considered another wall, the *EDA-wall* and is visible in Fig. 1.6. Moore's exponential pace of scaling enables more transistors for the same design space pressuring EDA manufacturers to scale design, simulation and verification time at the same pace to keep cost equal [92, p. 219]. The average amount of design rule checking (DRC) operations, a critical early verification process, is exploding [93], [94].

In the early EDA days chips were monolithic and designed with a small team of integrated circuit (IC) design and layout engineers. The first microprocessor, the Intel 4004 from 1971 had just 2300 transistors. The logic design, circuit design, layout design and verification was mostly done by a single person, Federico Faggin [95]. Development of silicon products in those days were done without computer aided design (CAD) tools, a synonym for EDA tools [92], [96]. When complexity grew to several thousands transistors in the mid 1970's, EDA tools such as SPICE circuit simulators and place and route (PnR) tools became a necessity. With an abundance of tools came also the need for deeper integration and automated workflows. A comprehensive historical overview about the period 1964-2002 can be found in [96]. Despite nearly 70 years of academic interest in higher radix computing few MVL EDA tools exist to accommodate design and verification of MVL circuits [97], [98]. These tools could aid in scaling the EDA wall for both binary and MVL circuits as some Boolean logic problems are better solved in the MVL domain [97], [99].

Transistor density and verification is not the only reason why the EDA wall grows exponentially. The enormous innovation to keep up with Moore's law forces the industry to keep developing new EDA functionality, tooling and workflows. Advances in materials science (such as high-k dielectrics, memristive materials), device evolution (such as planar MOSFET, finFET, GAAFET, CNTFET) and architectures (such as interconnect stackups, superscaler, in-memory compute) all need software to be supported. In 2018 DARPA launced a 100 million open source investment to drastically curb costs of modern silicon and control the EDA wall. This initiative had lead to OpenRoad [100], Openlane [101] and SiliconCompiler [102] which aim to provide complete or partial RTL to GDS flows. Openlane is used in this thesis work. These flows rely on open process design kits (PDK) which are considered the crown jewels of a foundry. Examples of open source PDK's are Skywater foundry's 90nm and 130nm, GlobalFoundries 180nm and ASAP7, a 7nm FINFET PDK [103].

Another popular measure to reduce cost and complexity is reusing battle-tested components, so called intellectual property (IP) blocks. This is a very similar to the reusable component principle in software engineering. According to [91] a modern System-on-Chip (SoC) uses on average over 175 IP blocks with just 20% of the design being custom. Many commercial chips are no longer designed as monolithic. Rather a multi-process or *chiplet* approach is used, merging several dies on a single substrate to form a complete SoC. Gordon Moore already predicted the cost benefits of this strategy in his 1965 paper [17].

The integration of artificial intelligence (AI) might also reduce cost and complexity. The launch of AI accelerator chips to the market is increasing astronomically [104] and influences many industries. The EDA industry has an interesting dependency dynamic with AI accelerators. EDA functionality is being more and more integrated with AI such as CPU design with ChatGPT [105] and IP block placement based on reinforcement learning (RL) [106]. This in turn leads to better AI chip designs, a self-reinforcing loop. Important is that AI for verification (and validation) is still lacking, often because the test patterns depend on the design.

# 1.5 The fundamental limits of computing

The fundamental limits of computing has historically excited computer researchers [7], [107]–[112]. The discussion if Moore's law has already ended has devolved into semantics. Density scaling is certainly ongoing [15], but the same source shows that transistor costs is not following the same exponential scaling. Renowned chip designer Jim Keller shows that pushing Moore's law has never been a single technology development but rather a series of S-curves [113]. It undeniable though that several parameters depicted in Fig. 1.1 have not seen exponential growth for decades. The availability of more transistors

#### 1 Introduction

made up for the inefficiency of the whole system. This is a similar to the abstraction in higher level programming languages. Simplifying programming with natural language increases application development but at the cost of application performance and power consumption [114].

Investigating the influence of radix on computational limits requires an overview of fundamental principles that govern computing. A comprehensive overview is published by Markov [7] and includes several physical, mathematical and practical limits in domains such as material, devices, circuits and software. From these Shannon's limit and Landauer's limit stand out for inspection against the practical limits since it uses radix-2 in its formulation. In addition the mathematical theorem on radix economy is added and Rent's rule, a complexity heuristic that is directly effected by the radix.

#### 1.5.1 Shannon's limit