University of South-Eastern Norway Faculty of Technology, Natural Sciences, and Maritime Sciences

Master Thesis in Systems Engineering with Embedded Systems Department of Science and Industry Systems November 27, 2020

Halvor Nybø Risto

# A study of CNTFET implementations for ternary logic and data radix conversion

### ⓒ Halvor Nybø Risto, 2020

University of South-Eastern Norway Faculty of Technology, Natural Sciences, and Maritime Sciences Department of Science and Industry Systems PO Box 235 NO-3603 Kongsberg, Norway

http://www.usn.no

This thesis is worth 30 study points

The undersigned have examined the thesis entitled A study of CNTFET implementations for ternary logic and data radix conversion presented by Halvor Nybø Risto, a candidate for the degree of Master in Systems Engineering with Embedded Systems and hereby certify that it is worthy of acceptance.

| Date | Head of Department      |

|------|-------------------------|

|      |                         |

| Date | Supervisor's name       |

|      |                         |

| Date | Committee member's name |

|      |                         |

| Date | Committee member's name |

Date

## Abstract

### Ternary logic theory and CNTFETs

The basic theory of ternary logic and CNTFETs are explored and explained, to set a theoretical context and build a base for the rest of the thesis. For ternary logic, this includes radix economy, ternary notations, ternary-valued logic functions, ternary algebra, and conversion overhead. For CNTFETs, topics discussed are the architecture, voltage threshold and characteristics, nanotube chirality, benefits over MOSFETs, and simulation models.

#### Ternary-valued CNTFET circuit design and logic synthesis

The methods used for transistor- and gate-level circuit design of ternary-valued CNTFET circuits are described, utilized, optimized, and automated with a logic synthesizer for generating simulation files with a research paper accepted in the SIMS 2020 conference, which includes proposed full adder circuits compared with simulation results.

### Radix conversion of data between binary and ternary

Several methods of data radix conversion is discussed and explained. One method is implemented and optimized using the logic synthesizer, with circuit simulation results in HSPICE. It is shown that data radix conversion can be done at high speeds with a low transistor count and power consumption with the CNTFET circuits generated by the proposed logic synthesizer tool, with the proposed gate-level design.

**Comparing binary-valued circuits with ternary-valued circuits for the purpose of basic arithmetic** Several ternary-valued full adder circuits are compared with binary-valued full adder circuits, including synthesized circuits as well as circuits found in related works. These circuits are compared in terms of transistor count, power consumption, and signal delay, while scaling for the digit ratio between binary and ternary. Despite any benefits of ternary logic, a ternary-valued adding circuit could not be found to outperform an equivalent binary-valued circuit for the purpose of basic arithmetic in terms of PDP and transistor count, with the CNTFET circuits used in this thesis.

# Acknowledgements

I would like to thank the Ternary Research Group at USN for their help and cooperation with my research and guidance for this thesis, especially my supervisor Henning Gundersen and co-supervisor Steven Bos for taking their time to discuss in-depth the topics covered in this thesis, and help in writing multiple research papers. Thank you to my classmates, Yasin Yari, Mohanned Hadi, and Julian Breivold Nilsen, for your friendship through good times as well as trying times, and for the amazing experiences we've had together throughout this master's course.

I would also like to give special thanks to the discoverer of caffeine and inventor of caffeinated drinks, as many late nights were spent with coffee or an energy drink as my companion to complete this thesis.

# Contents

| 1        | Introduction                                               | 1         |

|----------|------------------------------------------------------------|-----------|

|          | 1 What is ternary logic?                                   | 1         |

|          | 2 Ternary computation in the past                          | 1         |

|          | 3 Why use ternary logic?                                   | 1         |

|          | 4 What are CNTFETs?                                        | 2         |

|          | 5 The need for efficient radix converters                  | 2         |

|          | 6 Research methodology                                     | 2         |

| <b>2</b> | Theory                                                     | 4         |

|          | 1 Ternary logic                                            | 4         |

|          | 2 CNTFETs                                                  | 10        |

| 3        | Related works                                              | <b>14</b> |

|          | 1 Circuit design and logic synthesis                       | 14        |

|          | 2 Radix conversion between binary and ternary              | 16        |

|          | 3 Comparing ternary logic with binary logic                | 17        |

|          | 4 Conclusion of literature review                          | 18        |

| <b>4</b> | Logic Synthesis and Circuit Design                         | 19        |

|          | 1 Circuit design methodologies                             | 19        |

|          | 2 Risto et al. 2020                                        | 25        |

|          | 3 Optimizing gate-level design                             | 29        |

| <b>5</b> | Radix conversion circuits                                  | 30        |

|          | 1 Radix conversion circuit architecture                    | 30        |

|          | 2 Circuit design                                           | 32        |

|          | 3 Simulation results                                       | 34        |

| 6        | Ternary versus Binary logic circuits                       | 35        |

|          | 1 General overview of synthesized functions                | 35        |

|          | 2 Use cases of ternary logic                               | 37        |

|          | 3 Design of adder circuits                                 | 38        |

|          | 4 Simulation results                                       | 41        |

| 7        | Conclusion                                                 | 43        |

|          | 1 Ternary-logic circuit design and synthesis               | 43        |

|          | 2 Radix conversion and inter-radix compatibility           | 44        |

|          | 3 Comparison of ternary and binary for arithmetic circuits | 44        |

| 4            | 4 Discussions                                           | 44        |

|--------------|---------------------------------------------------------|-----------|

| ļ            | 5 Future work                                           | 46        |

| BII          | BLIOGRAPHY                                              | 48        |

| AP           | PENDICES                                                | <b>53</b> |

| A            | Risto et al., 2020, SIMS                                | 53        |

| B            | Radix converter main simulation file, radixconverter.sp | <b>57</b> |

| $\mathbf{C}$ | Ternary logic function circuit synthesizer, main.cpp    | 66        |

# List of Figures

| 2.1  | Overhead over datasize                                                                                                                                          | 9  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2  | (a)Typical CNTFET (b)SB-CNTFET (c)MOSFET-like (d)T-CNTFET                                                                                                       | 10 |

| 2.3  | Voltage-current characteristic at various CNT diameters                                                                                                         | 10 |

| 2.4  | Chirality vectors of the CNT on a sheet of graphene                                                                                                             | 11 |

| 2.5  | CNTFET implementations of the NTI(a), $PTI(b),$ and $STI(c)$ inverters $\ \ldots \ \ldots$ .                                                                    | 12 |

| 2.6  | DC analysis of 5 STI circuits in series, compared to the input voltage and its inverse .                                                                        | 13 |

| 4.1  | Capacitor-aided ternary circuit                                                                                                                                 | 19 |

| 4.2  | Static ternary gate design type A and type B                                                                                                                    | 20 |

| 4.3  | Transistor switching table                                                                                                                                      | 20 |

| 4.4  | Basic gate-based balanced sum                                                                                                                                   | 21 |

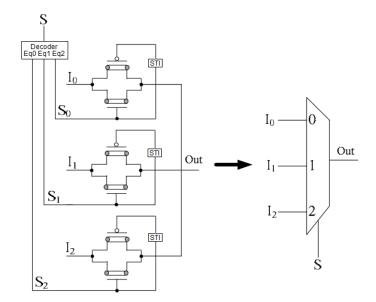

| 4.5  | General MUX-based circuit                                                                                                                                       | 22 |

| 4.6  | 1-trit MUX                                                                                                                                                      | 22 |

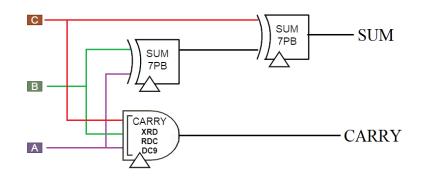

| 4.7  | Balanced sum (a) and carry MUX (b) circuits                                                                                                                     | 23 |

| 4.8  | Balanced full adder circuit (a) with any MUX circuit (b)                                                                                                        | 23 |

| 4.9  | 2-trit decoder extension of the 1-trit decoder                                                                                                                  | 24 |

| 4.10 | Truth tables for arity-2 functions with heptavintimal indexing                                                                                                  | 25 |

| 4.11 | Truth table synthesis for pull-up and pull-down networks for the unbalanced SUM gate                                                                            | 26 |

| 4.12 | Circuit implementation of a pull-up network truth table with 2 groups                                                                                           | 26 |

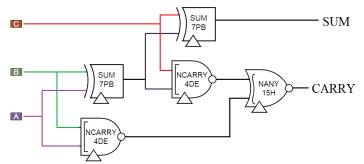

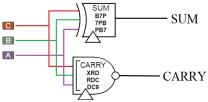

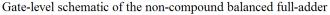

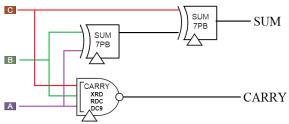

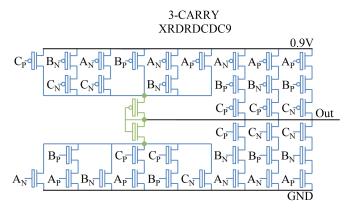

| 4.13 | Circuit implementation of the balanced carry                                                                                                                    | 27 |

| 4.14 | Three proposed balanced ternary full adders "compound" (a), "non-compound" (b),                                                                                 |    |

|      | "hybrid"(c)                                                                                                                                                     | 28 |

| 5.1  | Radix converter with unoptimized adders                                                                                                                         | 32 |

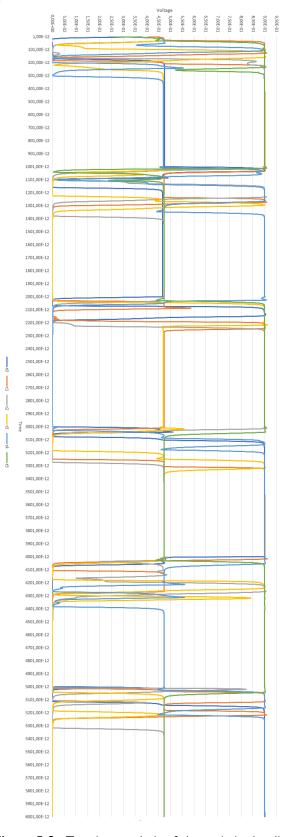

| 5.2  | Transient analysis of the optimized radix converter                                                                                                             | 34 |

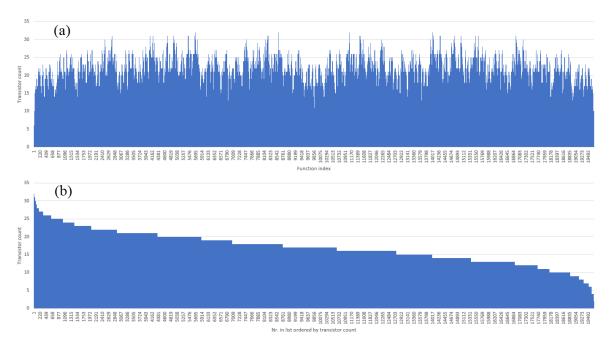

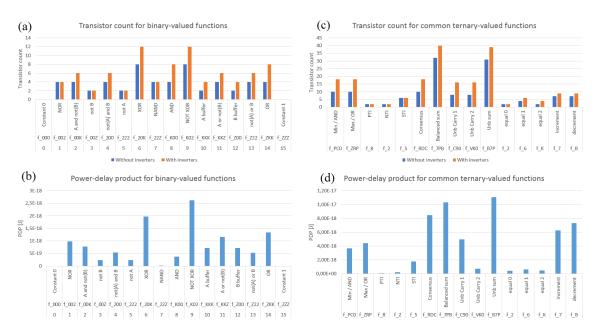

| 6.1  | Transistor count for all ternary-valued functions of arity 2, by index (a), by count (b)                                                                        | 35 |

| 6.2  | $Transistor \ count(a)(c) \ and \ PDP(b)(d) \ for \ binary-valued(a)(b) \ and \ common \ ternary-$                                                              |    |

|      | $valued(c)(d)$ functions $\ldots \ldots \ldots$ | 37 |

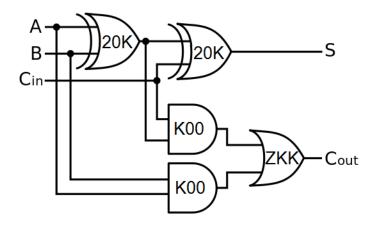

| 6.3  | Common gate-level design of binary full adder                                                                                                                   | 38 |

| 6.4  | Proposed ternary full adder                                                                                                                                     | 39 |

| 6.5  | Gate-based sum                                                                                                                                                  | 39 |

| 6.6  | Capacitor-aided ternary full adder                                                                                                                              | 40 |

| 7.1  | Secondary optimization of the full- $V_{DD}$ pull-up transistor network of function B7P7PBPB7                                                                   | 46 |

# List of Tables

| 1.1  | Parameters for CNTFET model                                                                 | 3  |

|------|---------------------------------------------------------------------------------------------|----|

| 2.1  | Average radix economies for various bases                                                   | 4  |

| 2.2  | Unbalanced and balanced ternary compared to decimal and binary                              | 5  |

| 2.3  | Number of possible logic functions in binary-valued logic versus ternary-valued logic .     | 6  |

| 2.4  | Ternary-valued truth table for unbalanced sum                                               | 6  |

| 2.5  | Binary-valued truth table for "XOR"                                                         | 6  |

| 2.6  | Truth table for MAX and MIN                                                                 | 6  |

| 2.7  | Truth table for increment, decrement, NTI, PTI, STI, equalities                             | 6  |

| 2.8  | Truth table for CON and ANY                                                                 | 7  |

| 2.9  | Data capacity for ternary and binary                                                        | 8  |

| 2.10 | Ternary conversion overheads with standard binary data sizes                                | 9  |

| 2.11 | Binary conversion overheads with standard binary data sizes                                 | 9  |

| 2.12 | Truth tables for the ternary inverters                                                      | 12 |

| 4.1  | Truth table of balanced sum                                                                 | 21 |

| 4.2  | The heptavintimal notation                                                                  | 25 |

| 4.3  | Simulation results with 2fF load capacitor                                                  | 28 |

| 5.1  | Digit relation                                                                              | 31 |

| 5.2  | Radix relation matrix                                                                       | 31 |

| 5.3  | Expected carry signal values from each block in the radix converter circuit $\ldots \ldots$ | 33 |

| 5.4  | Indices of optimized sum functions for the radix converter circuit                          | 33 |

| 5.5  | Indices of optimized carry functions for the radix converter circuit                        | 33 |

| 5.6  | Performance of 8-bit to 6-trit radix converter                                              | 34 |

| 5.7  | Input value sequences for simulation                                                        | 34 |

| 6.1  | The 16 binary-valued functions                                                              | 36 |

| 6.2  | Commonly used ternary-valued functions                                                      | 36 |

| 6.3  | Simulation results of binary and ternary full adders                                        | 41 |

| 6.4  | Minimum digits required for a minimum counting range                                        | 41 |

| 6.5  | Equivalent comparison of full adders with adjusted values for the ternary circuits          | 42 |

### Chapter 1

## Introduction

In recent years, the development of processors with higher processing power has been slowing down [1]. To continue exponential growth and miniaturization, chip manufacturers must shift to new technologies. One promising technology is Carbon Nanotube Field Effect Transistors (CNTFETs) [2] which may allow Moore's law to continue in some form, and to go beyond the limitations of current technology. The current outlook, based on the past 70 years, is that processor technology will advance while keeping the binary-value computing paradigm in place, with little consideration to multi-valued logic with more than 2 logical values for the purpose of general computation [3], outside of research. In recent years, there has been a renewed interest in ternary research with CNTFET circuits.

### 1 What is ternary logic?

Today, most computation and data storage is done with binary, the individual unit of which is called a bit. These bits are represented by the two values 0 and 1, hence the name "binary", or base 2. However, multi-valued logic with a radix higher than 2 can be done as well, and in fact it is used in some cases such as in digital signal processing [4][5][6]. Ternary, represented by trits, makes use of three values for each digit with the logical values of 0, 1, and 2.

### 2 Ternary computation in the past

In 1958, a balanced ternary-valued computer was developed at Moscow State University. This was the Setun [7]. This computer was developed to fulfill the computational needs of the university, and fifty computers were built, until production was halted in 1965. In recent years, there has still been a small amount of research into software development for these types of computers [8]. One reason that binary-valued logic has been dominating over ternary-valued logic in the past is the difficulty and cost of engineering silicon-based transistor circuits as these require large components such as resistors to achieve three stable voltage levels[3]. However, recent work such as [9] demonstrate by circuit simulation that CNTFET-based logic circuits can be engineered to have three stable voltage levels by varying the width of the carbon nanotubes, with no need of extra components other than transistors.

### 3 Why use ternary logic?

It has been suggested in theory that a ternary-value computer, or ternary data processing components in general, may be more cost-efficient than an equivalent binary version. This has been suggested with the calculation of the radix economy [10][11], and the more compact representation of information itself (eg. 8 bit information can be stored in 6 trits, a saving of 25%). Another possible advantage is the much higher number of 19683 possible binary operators in 3-valued logic, compared to 16 in 2-valued logic [12]. This larger number of binary operators may allow for further-reaching abstractions than in binary logic. Some functions such as ternary state machines might benefit from natively ternary states. In safety-critical systems, ternary-value computation may provide a benefit in allowing digits to be in an "uninitialized" stage, with the two remaining digit values functioning as binary values, to ensure that uninitialized values are not read as data values [13]. For safety-critical systems, ternary logic may also be used with ternary decision diagrams [14][15].

### 4 What are CNTFETs?

Carbon NanoTube Field-effect Transistors (CNTFETs) are a type of transistor which can be built with different voltage thresholds by changing the diameter of the carbon tube. This allows for multi-valued logic circuits such as ternary, without the need for extra components such as resistors to create the middle voltage level [9].

Example theorized or realized ternary chips are AI chips [16], graphical co-processors in a GPU, ternary based security [13], or ternary blockchain chips for IOTA [17].

### 5 The need for efficient radix converters

It is imaginable that specialized ternary chips will be integrated next to binary chips and pre-existing technology. This strongly benefits from a hardware radix conversion solution to minimize the conversion penalty of delay, as opposed to converting the inputs and outputs via microprocessors and software. To enable ternary technologies to develop in the near future, solutions for efficient radix conversion must first be developed, so that ternary components may be integrated in a mixed-radix system without too much conversion penalty.

Potentially, in later adoption stages of ternary-valued logic, the need for binary to ternary conversion chips will still be relevant for backwards compatibility or for mixed radix systems where binary and ternary values may coexist. To facilitate the feasibility of mixed radix systems, the signal delay through the proposed converters must be as low as possible, and should be scalable, to allow for fast and large-scale radix conversion of large quantities of data on the fly.

### 6 Research methodology

### 6.1 Research questions

A set of research questions is asked to guide the research project.

- 1. How can CNTFETs circuits perform multi-valued logic computation, and what methods are there to design the ternary circuits on the transistor and gate level?

- 2. How can compatibility be achieved between ternary-valued and binary-valued circuits? To enable ternary technology to develop into practical uses, it has to be compatible with existing technology. How can the data of the established binary radix be converted into the ternary radix efficiently, and what are the conversion penalties in terms of signal-delay, power consumption, transistor count?

- 3. How does ternary-valued logic circuits perform compared to binary-valued circuits? Can the benefits be shown to exist with circuits such as basic arithmetic circuits in terms of PDP?

To answer the research questions posed in this thesis, the primary methodological approach was to automate a logic synthesis algorithm, and simulate the circuits in HSPICE, after which they can be examined objectively. Using this same method for both binary-valued and ternary-valued circuits results in a more fair comparison, as binary-valued technologies have the benefit of many decades of aggressive optimization. Additionally, related research was also recreated and compared.

### 6.2 CNTFET circuit simulation

For simulating CNTFET circuits two components are integral, a SPICE circuit simulator and a CNTFET simulation model. Two SPICE simulators were considered: T-Spice from the Tanner software suite, [18] and HSPICE from the Synopsys software suite [19]. Two simulation models of CNTFETs are provided by Stanford University: the standard 32nm CNFET model [20], and the more compact VS-CNFET model [21]. The VS-CNFET was attempted to be used with T-Spice, with some functional circuits achieved, however did not produce sufficient correctness and functionality in circuit measurements when compared with existing research. As the models are optimized for use with HSPICE, T-Spice produced frequent convergence issues. Through experiment, the best combination was found to be the standard 32nm CNFET model in combination with HSPICE, which is also the most commonly used CNTFET model and SPICE software in research. The CNFET parameters used in this thesis is shown in table 1.1.

| Parameter       | Value  | Description                                                           |

|-----------------|--------|-----------------------------------------------------------------------|

| L <sub>ch</sub> | 32e-9  | Physical channel length                                               |

| $L_{geff}$      | 100e-9 | The mean free path in the intrinsic CNT channel region due to         |

|                 |        | non-ideal elastic scattering                                          |

| $L_{ss}$        | 32e-9  | The length of doped CNT source-side extension region                  |

| $L_{dd}$        | 32e-9  | The length of doped CNT drain-side extension region                   |

| $T_{ox}$        | 4e-9   | The thickness of high-k top gate dielectric material                  |

| Kox             | 16     | Gate oxide dielectric constant                                        |

| Efi             | 0.6    | The Fermi level of the doped S/D tube                                 |

| $C_{sub}$       | 40e-12 | The coupling capacitance between the channel region and the substrate |

| Pitch           | 20e-9  | The distance between the centers of two adjacent CNTs                 |

| Tubes           | 3      | Number of CNTs                                                        |

| Supply          | 0.9    | Gate supply voltage                                                   |

| Temp            | 25     | Temperature                                                           |

Table 1.1: Parameters for CNTFET model

### 6.3 Circuit measurement methodology

With H-SPICE, the performance characteristics or a circuit can be measured.

Transistor count is the number of transistors used in a circuit. For sub-circuits that require extra external components such as input inverters, both the sub-circuit count and total count is included. Current measurement is measured at the voltage supply, with an ideal 0V supply in series with the circuit. To find the power in Watt, multiply by the supply voltage (0.9V). As the inputs may have half-voltage (0.45V), the currents should not be directly added. However, in most circuits the inputs do not produce a significant current, as they are only used as a transistor gate voltage. In the event that they do produce power, they should be measured separately to find the correct power consumption. In the event of alternating current direction, only one way of the current is measured for each voltage source, to prevent duplicate measurements of the same current going through multiple voltage sources. The worst-case delay is the maximum time the circuit takes from a change in inputs to a stable and correct output. It is the worst-case which limits the frequency at which the circuit can be functional. The PDP is the power-delay product, which is found by multiplying the power consumption with the delay of the circuit. For the best-case PDP, the worst-case delay is used. As a circuit output load, a capacitor can be used, or alternatively an FO4 fan out load consisting of 4 inverters in series, to simulate the sub-circuit of interest in the context of a larger circuit with external capacitance.

### Chapter 2

# Theory

This chapter will cover the basic theory of ternary logic and CNTFETs.

### 1 Ternary logic

In the past, there have been claims of ternary being the optimal radix [3], as well as some counterarguments against these claims [22]. There are several reasons ternary-valued logic might have benefits over binary-valued logic.

### 1.1 Radix economy

The radix economy is a measure of the cost of expressing numbers in a given base. This is found by taking the number of digits required to express a number and multiplying by the base [23]. For the general case of base b and number N, this can be expressed as in equation 2.1.

$$E(b, N) = b * |log_b(N) + 1|$$

(2.1)

The radix economy of different bases can be compared by taking the average of the radix economy for a given base b with an increasing N up to a large number. The average is used, since data overhead will cause noise in the data. As N increases, the significance of this overhead will decrease.

| Base b | Avg. E(b,N)  | Avg. E(b,N)   | Avg. $E(b,N)$  | Avg. E(b,N)     |

|--------|--------------|---------------|----------------|-----------------|

|        | N = 1  to  6 | N = 1  to  43 | N = 1  to  182 | N = 1  to  5329 |

| 1      | 3.5          | 22.0          | 91.5           | 2665.0          |

| 2      | 4.7          | 9.3           | 13.3           | 22.9            |

| e      | 4.5          | 9.0           | 12.9           | 22.1            |

| 3      | 5.0          | 9.5           | 13.1           | 22.2            |

| 4      | 6.0          | 10.3          | 14.2           | 23.9            |

| 5      | 6.7          | 11.7          | 15.8           | 26.3            |

Table 2.1: Average radix economies for various bases

According to these equations, the optimal radix can be found to be e, or 2.718, with base-3 and base-2 following in optimality, as seen in table 2.1. Since digital logic operates on integer bases, it follows that ternary-valued logic is the optimal base for computation. One flaw with this logic is the assumption that the number of required components scales proportionally with the base, i.e. an increase by a factor of 1.5 from binary to ternary. This will be investigated further in later chapters.

### 1.2 Balanced and unbalanced ternary notation

There are mainly two methods for expressing a number in ternary. The most straight-forward notation is unbalanced ternary, which is analogous to unsigned binary numbers. It is expressed with the symbols '0', '1', '2'. The other, more elegant notation, is balanced ternary, which is expressed with the symbols '-1', '0', '+1', or '-', '0', '+' as a short form [24][25]. Donald Knuth, a renowned computer scientist, writes in his book "The Art of Computer Programming", that "Perhaps the prettiest number system of all is the balanced ternary notation, which consists of radix-3 representation using -1, 0, and +1 as "trits" (ternary digits) instead of 0, 1, and 2". Furthermore, he stated that "If it would have been possible to build reliable ternary architecture, everybody would be using it." [26].

A comparison of unsigned binary, unbalanced and balanced ternary is shown in table 2.2. While binary requires a sign-bit to express negative numbers, balanced ternary can express both positive and negative numbers, while utilizing

| Table   | 2.2:  | Unbalanced    | and    | balanced |

|---------|-------|---------------|--------|----------|

| ternary | compa | ared to decim | al and | d binary |

| Decimal | Binary | Unbalanced | Balanced |

|---------|--------|------------|----------|

| -3      |        |            | 0 - 0    |

| -2      |        |            | 0 - +    |

| -1      |        |            | 00-      |

| 0       | 000    | 000        | 000      |

| 1       | 001    | 001        | 0 0 +    |

| 2       | 010    | 002        | 0 + -    |

| 3       | 011    | 010        | 0 + 0    |

| 4       | 100    | 011        | 0 + +    |

| 5       | 101    | 012        | +        |

| 6       | 110    | 020        | + - 0    |

the full capacity of the trits. A result of this is a halved range in the positive value range compared to unbalanced, analogous to signed and unsigned binary numbers. Note that balanced ternary sometimes requires one more digit than the unbalanced ternary. To convert balanced ternary between positive to negative, all the digits are inverted, or in other words + is swapped with - and vice versa [27].

Despite the fault of having half the capacity of unsigned ternary numbers, balanced ternary makes up for it with arithmetic convenience[28][29], such as simpler addition and subtraction, and the capability of representing negative numbers.

Since the established norm with binary logic is that 1 represents 'true', it is also sometimes used as 'true' in unbalanced ternary values, with 2 representing 'unknown' or 'undefined'. It is more common to use 2 as 'true', as it is easier to operate on full binary voltage, while the middle voltage level may be used either to represent an uninitialized value, i.e. "unknown" [10], or a logical middle value with radix-3 data encoding.

### 1.3 Logic functions

A logic function, also known as a logic gate, is an abstract element which takes a number of digit inputs and outputs one digit output. With these logic functions, any logical operation can be done [30]. The number of parameters or inputs a function has, is known as the functions "arity". This arity can for example be 1, 2, or 3, which are known as unary, binary, and ternary functions respectively [31]. Note that the arity of a function does not imply the radix of the digit inputs to the function.

The number of possible functions for a specific arity and radix can be calculated as in equation 2.2, where R is the radix and A is the arity.

$$F_{range} = R^{(R^A)} \tag{2.2}$$

An increase of the radix by one offers an extreme increase of number of possible functions as the arity increases, as shown in Table 2.3.

| _ |       |                 |                               |

|---|-------|-----------------|-------------------------------|

|   | Arity | Radix 2         | Radix 3                       |

|   | 1     | $2^{2^1} = 4$   | $3^{3^1} = 27$                |

|   | 2     | $2^{2^2} = 16$  | $3^{3^2} = 19683$             |

|   | 3     | $2^{2^3} = 256$ | $3^{3^3} = 7,625,597,484,987$ |

Table 2.3: Number of possible logic functions in binary-valued logic versus ternary-valued logic

A logic function can be expressed in terms of a truth table. Tables 2.4 and 2.5 show the truth tables for the ternary-valued unbalanced sum, and the binary-valued XOR, both of which are used to find the sum of two digits, a and b.

**Table 2.4:** Ternary-valued truth tablefor unbalanced sum

| a | b | Sum |

|---|---|-----|

| 2 | 2 | 1   |

| 2 | 1 | 0   |

| 2 | 0 | 2   |

| 1 | 2 | 0   |

| 1 | 1 | 2   |

| 1 | 0 | 1   |

| 0 | 2 | 2   |

| 0 | 1 | 1   |

| 0 | 0 | 0   |

|   |   |     |

Table 2.5: Binary-valued truth table for "XOR"

| a | b | XOR |

|---|---|-----|

| 1 | 1 | 0   |

| 1 | 0 | 1   |

| 0 | 1 | 1   |

| 0 | 0 | 0   |

### 1.4 Ternary logic algebra

Like with boolean algebra for binary logic, a similar ruleset can be defined for decomposing ternary logic into smaller functions. With some base functions, such as MIN, MAX, increment, decrement, equalities, as well as the inverters NTI, PTI, STI, any ternary-valued logic function can be constructed [32]. The truth table of these functions are shown in tables 2.6 and 2.7. Note that here, the unbalanced notation is used, however these rules apply to both balanced and unbalanced, with -0+ being interchangable with 012 for the purposes of a logic truth table.

Table 2.6:

Truth table for MAX and

MIN

| a | b | MAX | MIN |

|---|---|-----|-----|

| 2 | 2 | 2   | 2   |

| 2 | 1 | 2   | 1   |

| 2 | 0 | 2   | 0   |

| 1 | 2 | 2   | 1   |

| 1 | 1 | 1   | 1   |

| 1 | 0 | 1   | 0   |

| 0 | 2 | 2   | 0   |

| 0 | 1 | 1   | 0   |

| 0 | 0 | 0   | 0   |

**Table 2.7:** Truth table for increment, decrement, NTI, PTI, STI,equalities

| a | incr. | decr. | NTI | PTI | STI | eq0 | eq1 | $\mathbf{eq2}$ |

|---|-------|-------|-----|-----|-----|-----|-----|----------------|

| 2 | 0     | 1     | 0   | 0   | 0   | 0   | 0   | 2              |

| 1 | 2     | 0     | 0   | 2   | 1   | 0   | 2   | 0              |

| 0 | 1     | 2     | 2   | 2   | 2   | 2   | 0   | 0              |

From table 2.7, it can be seen that NTI is the same function as equal 0, and that PTI is the inverse of equal 2, and STI is the inverse. Thus, we can write the functions used in ternary logic algebra as in equations 2.3 to 2.11

$$STI(a) = -a \tag{2.3}$$

$$NTI(a) = (a = 0) \tag{2.4}$$

$$Equal1(a) = (a = 1) \tag{2.5}$$

$$Equal2(a) = (a = 2) \tag{2.6}$$

$$PTI(a) = -(a = 2)$$

(2.7)

$Increment(a) = a + 1 \tag{2.8}$

$$Decrement(a) = a - 1$$

(2.9)

$$MAX(a,b) = a \lor b \tag{2.10}$$

$$MIN(a,b) = a \wedge b \tag{2.11}$$

As in boolean algebra, DeMorgan's theorem still holds for ternary-valued logic [25], shown in equation 2.12.

$$-(a \wedge B) = -a \vee -b \tag{2.12}$$

Furthermore, MAX and MIN are distributive, the same way AND and OR is in boolean algebra [25], shown in equation 2.13

$$a \lor (b \land c) = (a \lor b) \land (a \lor c) \tag{2.13}$$

With these rules, any ternary-valued logic function can be implemented with the basic functions listed. One method to achieve this is to write out the canonical sum of products for the functions, and optimize the equation. An example of this for the balanced sum function is given in chapter 4.

Two more commonly used basic logic functions, Consensus and Any, can be defined here. They can be defined in terms of the other basic functions as in equation 2.14 and 2.15, and therefore they are not strictly needed as basic functions. However due to their ease of direct implementation they are included here nonetheless. Their truth tables are shown in table 2.8.

**Table 2.8:** Truth table for CON andANY

| а | b | CON | ANY |

|---|---|-----|-----|

| 2 | 2 | 2   | 2   |

| 2 | 1 | 1   | 2   |

| 2 | 0 | 1   | 1   |

| 1 | 2 | 1   | 2   |

| 1 | 1 | 1   | 1   |

| 1 | 0 | 1   | 0   |

| 0 | 2 | 1   | 1   |

| 0 | 1 | 1   | 0   |

| 0 | 0 | 0   | 0   |

$$CON(a,b) = a \otimes b = (a \wedge b)$$

$$\lor ((-(a = 0)) \wedge 1)$$

$$\lor ((-(b = 0)) \wedge 1)$$

(2.14)

$$ANY(a,b) = a \oplus b = ((a = 0) \land (b = 2) \land 1)$$

$$\lor ((a = 1) \land b)$$

$$\lor ((a = 2) \land ((b = 0) - 1))$$

(2.15)

### 1.5 Data sizes and overhead

One clear benefit of ternary-valued logic compared to binary-valued logic is the higher data capacity per digit, which is a given since it is a higher base. This has implications for data storage, transmission, and processing, as data may be expressed more efficiently. The data capacity for binary and ternary scales exponentially as the number of digits increases, as can be seen in equation 2.16 where b is the base, and n is the data size. A comparison between binary and ternary is shown in table 2.9.

$$b^n \qquad b, n \in \mathbb{N} \tag{2.16}$$

| Data size | Binary      | Ternary      |

|-----------|-------------|--------------|

| 1         | $2^1 = 2$   | $3^1 = 3$    |

| 2         | $2^2 = 4$   | $3^2 = 9$    |

| 3         | $2^3 = 8$   | $3^3 = 27$   |

| 4         | $2^4 = 16$  | $3^4 = 81$   |

| 5         | $2^5 = 32$  | $3^5 = 243$  |

| 6         | $2^6 = 64$  | $3^6 = 729$  |

| 7         | $2^7 = 128$ | $3^7 = 2187$ |

| 8         | $2^8 = 256$ | $3^8 = 6561$ |

Table 2.9: Data capacity for ternary and binary

When converting between binary and ternary data, one might want to consider different data sizes to convert. One aspect to consider is the overhead, which is the difference in capacity of the binary number and the ternary number. The capacity of an unsigned number can be expressed as the base to the power of the number of digits. If signed, the capacity is roughly halved. Examine the equation (2.17).

$$2^n = 3^m \qquad m, n \in \mathbb{N} \tag{2.17}$$

One consequence of this equivalence is the ratio between the number of digits required for the two bases. From equation 2.17, equation 2.18 can be derived, which implies that one trit can replace approximately 1.5849 bits.

$$n = \frac{m * \log(3)}{\log(2)} \approx 1.5849 * m \tag{2.18}$$

Another consequence is that while both m and n are integers above zero, there are no integer solutions to equation 2.17, since  $2^n$  will always be even, and  $3^m$  will always be odd. This means that some overhead is unavoidable when converting between binary and ternary numbers. However, the overhead can be minimized by choosing the right data sizes.

#### **Optimized data sizes**

When considering radix conversion, it is here assumed that the ternary data size is larger in capacity than the binary. Data sizes with little overhead may be considered, such as 84 bit to 53 trit. This would have a mere 0.2 percentage overhead, as shown in (2.19).

$$100\frac{3^{53} - 2^{84}}{3^{53}} = 0.208595 \tag{2.19}$$

These data sizes could be used in cases where it is integral to keep overhead to a minimum, such as data storage, or efficiency-critical data processing components. There are also larger pairs of data sizes with even lower overhead. If a large increase of data sizes is allowable, an overhead arbitrarily close to 0 can be achieved. This can be shown to be evident with the following method.

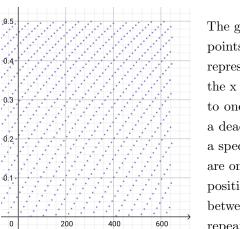

Figure 2.1: Overhead over datasize

$$overhead(m) = \frac{3^{\lfloor m \rfloor} - 2^{\lfloor \log_2 3^{\lfloor m \rfloor} \rfloor}}{3^{\lfloor m \rfloor}}$$

(2.20)

The graph in figure 2.1 can be plotted from equation 2.20. The points in this graph each represent the conversion overhead, represented by the y-axis, of a ternary data size, represented by the x axis. It is clear that this is not a function which converges to one value, and therefore taking the limit of this function is a dead end. Instead, it is observed that all the points land on a specific set of arcs. Furthermore, it is known that the points are only on whole numbers along the x-axis. Thereby, the off-set positioning of the points on each arc is defined by the distance between the arcs. If this distance is irrational, then there are no repeating patterns, and it can be assumed that every rational overhead will be covered as the data size approaches infinite. This is most likely the case, since the log of integers produces irrational numbers.

However, a generally useful converter to be used in standard binary systems should adhere to the standard binary data sizes, which generally have a number of bits which are a power of two.

#### Compatibility with powers of two

If this overhead exceeds the benefits of ternary, it might not be advantageous to use binary data sizes in a ternary setting. Depending on the choice of data sizes, the overhead may be on the ternary side, or the binary side. The radix with overhead must be limited in range to not exceed the limit of the other radix. For this thesis, it is assumed that the ternary data size is bigger than the binary, however here overheads are given for both cases. Tables 2.10 and 2.11 show the data conversion overhead for standard binary data sizes, for the cases of  $2^n < 3^m$ , and  $2^n > 3^m$  respectively.

| Table 2.10:   | Ternary conversion overheads |

|---------------|------------------------------|

| with standard | binary data sizes            |

| Bits     | Trits    | Overhead |

|----------|----------|----------|

| $2^{8}$  | $3^6$    | 64.88%   |

| $2^{16}$ | $3^{11}$ | 63.00%   |

| $2^{32}$ | $3^{21}$ | 58.94%   |

| $2^{64}$ | $3^{41}$ | 49.42%   |

**Table 2.11:** Binary conversion overheadswith standard binary data sizes

| Bits     | Trits    | Overhead |

|----------|----------|----------|

| $2^{8}$  | $3^5$    | 5.08%    |

| $2^{16}$ | $3^{10}$ | 9.90%    |

| $2^{32}$ | $3^{20}$ | 18.82%   |

| $2^{64}$ | $3^{40}$ | 34.09%   |

### 2 CNTFETs

Carbon Nanotube Field-Effect Transistors (CNTFET) is a highly promising transistor technology subject to a lot of research in recent years. One recent major milestone in CNTFET research was MIT's RISC-V processor, RV16XNano, which contains 14 000 CNTFETs[2].

### 2.1 Architecture of CNTFETs

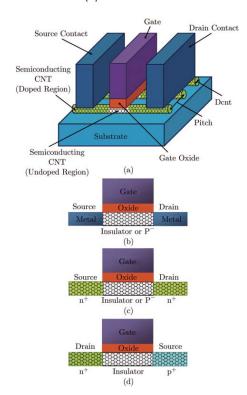

Carbon Nanotube Field-effect Transistors (CNTFET) is a type of FET, which uses semi-conducting carbon nanotubes (CNTs) as the channel, depicted in figure 2.2 from [33], instead of bulk silicon like in traditional fieldeffect transistors like MOSFETs. These CNTs have the same atomic structure as graphene, formed into a tube, usually with one wall a single atom thick. While similar in function to a MOSFET, they've been shown to have significant benefits in terms of performance [34], which may facilitate more compact processor designs, such as 3D-VLSI [35]. A CNT acts as a one-dimensional electron path, resulting in no electron scattering. CNTs have certain benefits over bulk silicon, like a better threshold voltage and sub-threshold slope, a high electron mobility due to the one-dimensional nature of the single-atom thick nanotube resulting in quasi-ballistic transport of electrons, high current density compared to bulk silicon, high linearity in the relationship between voltage and current, and high transconductance [36][37]. The manufacturing of these CNTFETs can use a similar process as MOSFETs, with the exception of the carbon nanotubes, which can be grown or deposited during the manufacturing process [38]. Like with MOSFET transistors, n-type and p-type transistors can be achieved by different chemical dopings in the channel [39].

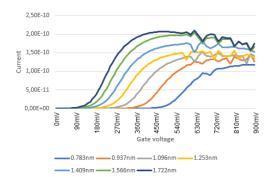

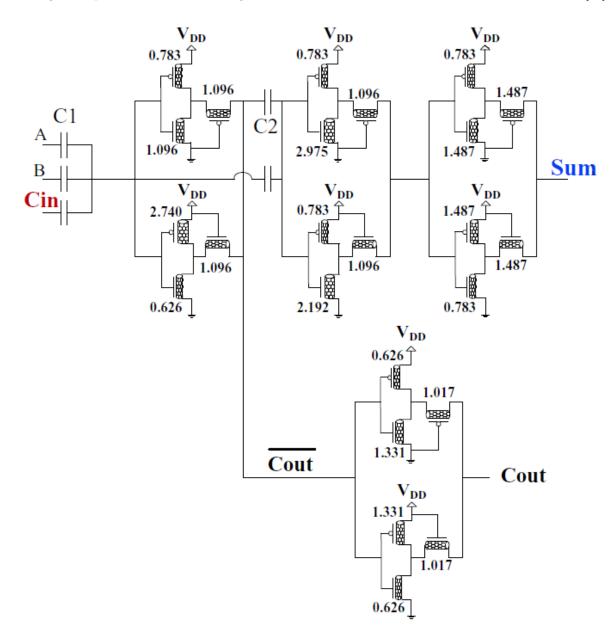

### 2.2 Voltage characteristic and threshold

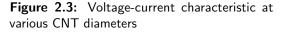

CNTFETs are useful for ternary-valued logic because of the fact that the voltage threshold of a specific transistor is dependant on the diameter of its carbon nanotubes. By using a combination of different voltage thresholds in the same circuit, multi-valued logic can be achieved. The voltage threshold  $V_{th}$  can be found with equation 2.21, where  $d_0$  is the carbon-to-carbon bond distance in carbon nanotubes, and  $V_{\pi}$  is the carbon  $\pi$ - $\pi$  bond energy [40]. Figure 2.3 shows the voltage-current characteristic of CNTFETs of various diameters, simulated in HSPICE. The simulations show that the voltage-current characteristic of the CNTFET matches up with the equation 2.21.

$$V_{th} \approx \frac{d_0 V_{\pi}}{e D_{CNT}} \approx \frac{0.43v}{D_{CNT}[nanometer]}$$

(2.21)

**Figure 2.2:** (a)Typical CNTFET (b)SB-CNTFET (c)MOSFET-like (d)T-CNTFET

### 2.3 Carbon nanotube chirality

The voltage threshold of a transistor can be chosen by specifying the nanotube diameter. The diameter and structure of the CNT can be expressed in terms of a chirality vector. The chirality vector  $\vec{C}_h$ symbolizes the two points which connect when the graphene is formed into a nanotube, i.e. the circumference of the tube. It is defined by the base vectors  $\vec{a}_1$  and  $\vec{a}_2$  and integer scalars (n,m) [41], as in equation 2.22.

$$\vec{C}_h = n\vec{a}_1 + m\vec{a}_2 \tag{2.22}$$

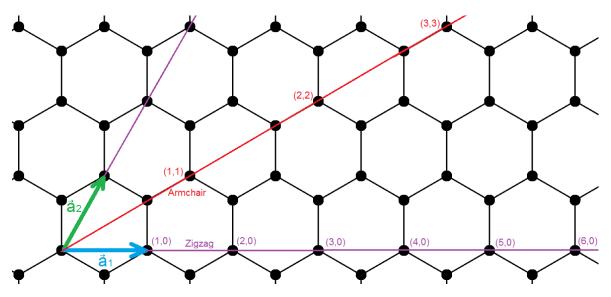

This chirality vector also indicates if the carbon nanotube is metallic or semi-conducting, which is a result of the structure of the tube [20]. For the purpose of CNTFETs, the chirality vector is restricted to semi-conducting values. The metallic CNTs have a structure called "Armchair", which is the case when n and m are equal, while the structure of semiconducting CNTs are called "Zigzag", which are when one scalar is 0, while the other is free to vary to specify the CNT diameter. For CNTFETs, the Zigzag pattern is utilized to produce semiconducting CNTs with variable diameter. Figure 2.4 shows the base vector, with the "Armchair" and "Zigzag" patterns on the atomic structure of flat graphene.

Figure 2.4: Chirality vectors of the CNT on a sheet of graphene

Since the chirality vector represents the circumference of the tube, equation 2.23 shows the relation between diameter of the CNT and the base vector scalars, where  $d_0$  is the carbon-carbon atomic bonding distance.

$$D_{CNT} = \frac{\sqrt{3}d_0}{\pi}\sqrt{m^2 + mn + n^2} \approx 0.0783\sqrt{m^2 + mn + n^2} \quad [nanometer]$$

(2.23)

To ensure the semi-conductivity of the CNT, m is set to 0 while n varies from transistor to transistor. Thus the equation for the diameter can be simplified to equation 2.24.

$$D_{CNT} \approx 0.0783 * n \quad [nanometer] \tag{2.24}$$

### 2.4 Viability for ternary logic circuits

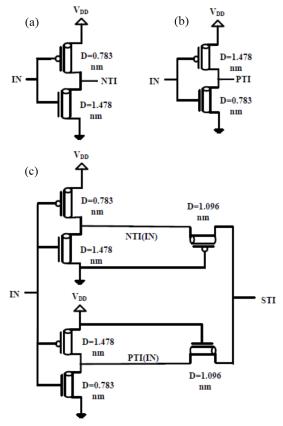

While the transistors themselves are inherently binary (on or off), due to the properties of the carbon nanotube, the voltage threshold of individual transistors can be specified by selecting a precise carbon nanotube diameter. With this knowledge, in combination with knowing how a binary inverter functions, we can build two of the three ternary inverters; the Positive Ternary Inverter (PTI), and the Negative Ternary Inverter (NTI). These two circuits can be combined to produce the Standard Ternary Inverter (STI) [9]. Their truth tables are shown in table 2.12, and circuit implementations in figure 2.5.

**Table 2.12:** Truth tables for the ternary inverters

| a | NTI | PTI | STI |

|---|-----|-----|-----|

| 2 | 0   | 0   | 0   |

| 1 | 0   | 2   | 1   |

| 0 | 2   | 2   | 2   |

This circuit demonstrates that ternary-valued logic circuits can be achieved with complementary circuits with binary-valued outputs, such as NTI and PTI. The middle voltage is achieved through what is essentially voltage division, which naturally results in a higher power consumption. When NTI outputs '0', and PTI outputs '2', there is a path between  $V_{DD}$  and GND. This current is limited by the series resistance of the two 1.096nm transistors connecting NTI and PTI. This has been cited as one of the main flaws of ternary-valued logic in CNTFET logic circuits [22].

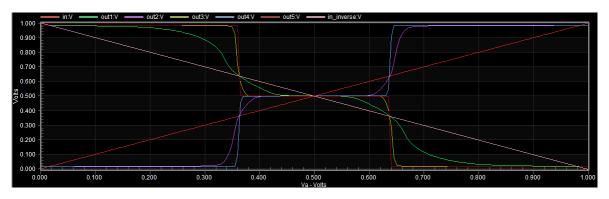

Next, a question of the stability of the middle value comes up. What happens if many STIs are connected in series? Will the voltage drift from the middle value over time? To show that CNTFET circuits such as the STI can produce a stable middle value, the input/output voltage

**Figure 2.5:** CNTFET implementations of the NTI(a), PTI(b), and STI(c) inverters

characteristic of the STI can be generated in simulation using the 32nm CNFET model, which can be compared with that of an ideal linear voltage inverter, which in theory would have no voltage drift in any direction when connected in series. For these circuits, the voltage range used is 0V to 1V. By overlaying the two voltage curves, it becomes clear in which areas the voltage is serially pushed upwards or downwards by the STIs in series. For example, while the ideal voltage inverter would in theory invert 900mV to 100mV, the curve of the input/output characteristic of the STI lies below this line, meaning 900mV outputs a value lower than 100mV, and similarly for an input of 100mV, is inverted by the STI to a voltage higher than 900mV. The consequence of this, is that voltages outside the thresholds of the middle value, which is the area between the two furthest points where the two curves cross, will drift towards the outer values, while the voltages within these thresholds will drift towards the value at the middle crossing point. A comparison of 5 serial STIs and the inverse voltage of the input is show in figure 2.6.

Figure 2.6: DC analysis of 5 STI circuits in series, compared to the input voltage and its inverse

The DC analysis shown in figure 2.6 demonstrates that for complementary ternary-valued circuits such as the STI inverter, the voltage levels are self-regulating, meaning voltage drift from the middle value to the high or low value is not an issue. In this example, the voltage thresholds are at 360mV and 630mV, inside which the voltage will drift towards the middle value of 0.5V, and outside of which the voltage will drift towards 0V and 1V.

### Chapter 3

## **Related works**

Before we continue, a brief literature review is done, which summarizes some pre-existing research and what their significances are in relation to this thesis. Like this thesis, the literature review is divided into three categories; Circuit design and logic synthesis, Binary-ternary data radix conversion, Comparisons of ternary-valued and binary-valued logic.

### 1 Circuit design and logic synthesis

Six papers or studies are identified, which present different methods of ternary-valued circuit design.

### 1.1 Stanley L. Hurst, 1984

Multiple-Valued Logic - Its Status and Its Future [3] surveys the possibility of MVL logic as opposed to binary, to increase information density in digital signals. pre-existing circuit implementations are discussed, realized with a CMOS-resistor design, which can be used to create combinatorial logic circuits with the Min, Max, and Unary logic gates. They consider future possible technologies, however this paper was published before the first demonstration of a CNTFET in 1998 [42][43]. They call the fact that no true multistate device higher than binary exists the major restraint to MVL technologies.

### 1.2 Douglas W. Jones, 2012

The Ternary Manifesto [25], by Douglas Jones from the University of Iowa Department of Computer Science, is a blog detailing ternary logic and how it could be implemented. He takes security-throughobscurity as a fundamental principle, to say that ternary should have security benefits over binary. He postulates that ternary logic, due to the fewer number of digits needed, should reduce the density of interconnect wiring, which is one of the main limiting factors of today's technology [3][44][45]. This benefit may possibly outweigh any additional cost of implementing more complex ternary circuits compared to binary.

The blog covers ternary logic, gate implementations with ternary logic algebra, ternary arithmetic, number and character encoding, heptavintimal encoding of triplets of trits, and proposes an instruction set computer architecture for ternary logic.

### 1.3 Chetan Vudadha et al. 2013

2:1 Multiplexer Based Design for Ternary Logic Circuits [46] investigates the usage of multiplexers to design a ternary full adder. They connect 1-trit multiplexers to produce the circuits used in a half adder, and by extension a full adder. In combination with ternary logic algebra, this method can be used to create combinatorial logic circuits to achieve any logic function.

### 1.4 Mohammad Hossein Moaiyeri et. al. 2015

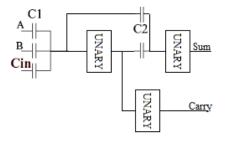

An efficient ternary serial adder based on carbon nanotube FETs [47] proposes a ternary serial full adder with a clocked flip-flop gate. Interestingly, the full adder is implemented with the unary logic gates of an STI inverter, with shifted voltage thresholds, and capacitors to take averages of voltages for the input to the unary gates. This allows for a very low transistor count, however it relies on extra components which take up space in a circuit, and which may cause a larger power consumption due to high-frequency current leakage through the capacitors, as well as high delay due to the capacitance required to produce a functional voltage in the nodes of the circuit. Therefore, its efficiency is debatable.

### 1.5 Sunmean Kim et al 2017

An Optimal Gate Design for the Synthesis of Ternary Logic Circuits [48] proposes a method of synthesising ternary-valued logic gates using a static gate design, based on pull-up and pull-down networks The paper claims that their method produces a minimal number of transistors for logic gates. The optimality is debatable, as other papers have produced full adders with a lower transistor count [49]. They show an decrease in power-delay product compared to earlier work. They claim that the reason ternary logic has not been shown to outperform binary logic is due to the lack of optimization of the ternary circuits. However, they do not show a comparison of their results with binary arithmetical circuits. This method is applicable for the synthesis of any ternary-valued logic gate with a good PDP performance.

### 1.6 Mingqiang Huang et. al. 2019

**Design and Implementation of Ternary Logic Integrated Circuits by Using Novel Two-Dimensional Materials** [50] investigates design of ternary-valued logic through ternary algebra with functions such as MIN and MAX, with the use of two-dimensional materials as opposed to CNTFETs. They argue that in large scale circuits, approximately 70 percent of the chip area is designated for wire interconnections, thus a significant decrease of interconnections can give a strong boost to the performance of a chip.

They show a 50% reduction in number of transistors in 2-dimensional-based transistor circuits compared with research done with silicon-based and CNT-based transistor circuits for an unbalanced ternary full adder, which may give a very significant decrease in interconnection density.

### 2 Radix conversion between binary and ternary

Papers which cover radix conversion are reviewed, particularly ones which relate to binary-ternary radix conversion.

### 2.1 Fu-Qiang et al., 1995

A binary to balanced ternary converter based on Josephson junctions [51] makes use of Superconducting Quantum Interference Device (SQUID) gates to construct a binary to ternary radix converter circuit. This specific circuit requires superconductors at low temperatures. However, their method of binary to ternary radix conversion can be applied to CNTFET circuit design. By decomposing the arithmetic relation between binary and ternary digits, each ternary output can be defined as the sum of a set of binary inputs, with carry signals propagating from the least significant trit to the most significant trit.

### 2.2 Sasao, 2005

**Radix converters: complexity and implementation by LUT cascades** [52] assesses the design methods of general n-ary to q-ary data radix converters with the use of look-up table cascades. They use column multiplicity to mathematically deduce the lower bound of complexity for such a circuit.

This work was continued in [53] and [54], where arithmetic decomposition is used to design the converters.

### 2.3 Arjmand et al., 2012

In [55] an unbalanced ternary to unsigned binary converter for Quantum-dot Cellular Automata (QCA) is proposed. There are four possible states of a ternary QCA cell, two of which are zero, each of which are mapped on to two bits. While this same method could generally be implemented in a ternary logic circuit, this is not a capacity efficient conversion method, as two bits are used to store one trit, while the optimal tends towards approximately 1.58496 bits per trit, and therefore is not applicable to an efficient binary-ternary radix converter based on CNTFETs.

### 2.4 Shahangian et al., 2019

**Design of a multi-digit binary-to-ternary converter based on cntfets** [56] proposes a design method for unsigned binary to unbalanced binary, using the arithmetic decomposition method to produce the binary-ternary digit relation. Optimized adders are constructed with some unary circuits such as increment, decrement, and the inverters, as well as compact optimized 1-trit MUX circuits, and carry generator. These circuits are optimized in regards to the expected values of the inputs. As an example, the mux may only need to decode the select trit to two possible values instead of the full three, depending on the exact circuit. They show performance results for various digit sizes, including 8-bit to 6-trit.

### 2.5 Shahangian et al., 2020

Universal Method for Designing Multi-Digit Ternary to Binary Converter Using CNT-FET [57] is a continuation of [56], and proposes a method of converting unbalanced ternary to unsigned binary. They use similar methods, except that this circuit decodes the individual trits to binary signals to process them with binary adder circuits. They show simulation results, which are significantly better than their binary-ternary results.

### 3 Comparing ternary logic with binary logic

### 3.1 Hande Alemdar et al. 2017

Ternary Neural Networks for Resource-Efficient AI Applications [58] proposes a TNN (ternary neural network) with ternary neuron activations using a step function with two thresholds. With the levels used for weights and activation of -1, 0, and +1, they prune smaller weights by setting them to 0 during training, which makes them sparser, and thus makes the neural network more energy-efficient, compared to the binary counterpart of -1 and +1. Instead of encoding this data directly in balanced ternary with MVL circuits, the balanced ternary digits is encoded in binary data [59]. They consider efficient encoding and decompression of the balanced ternary digits in binary [60]. This will involve some overhead between the data space used and the actual symbols represented with bits. They do not consider the use of natively ternary-valued circuits.

### 3.2 Daniel Etiemble, 2019

Ternary circuits: why  $\mathbf{R} = \mathbf{3}$  is not the Optimal Radix for Computation [22] claims to have disproven that ternary-valued computation is superior to binary-valued computation. They review other existing research without providing simulation data themselves for power consumption or signal delay, with mainly comparisons of transistor count of equivalent binary and ternary circuits, which could possibly outweigh the higher transistor count needed to implement a more complex truth table. They argue that a higher transistor count overall can only lead to a higher interconnection length, however studies such as [61] show that the interconnection length can be reduced with ternary logic circuits.

While they refute the claim of radix economy implying ternary to be optimal, they do not refute the potential of ternary technologies over binary technologies in every aspect, as they do not properly consider factors such as PDP and interconnection wire length densities, and only cover some operators such as sum, and not multipliers. They have only shown that ternary has not yet been shown to outperform binary, due to engineering challenges.

### 3.3 Kiyung Kim et al., 2020

Extreme Low Power Technology using Ternary Arithmetic Logic Circuits via Drastic Interconnect Length Reduction [61] implements cell layouts for a balanced full adder and a multiplier, using the static gate design of [48]. Their balanced full adder is identical to the one proposed in [48], as well as the "compound" balanced full adder described in this thesis in chapter 4 section 2.3. They measure the interconnect wire length of the adder and the multiplier, for 5 trits, and compare it with the wire length for an 8-bit binary-valued adder and multiplier. They show that the ternary 5-trit multiplier significantly outperforms the 8-bit binary multiplier with a 37% reduction in length, however the ternary adder is slightly outperformed by the binary adder. They do not investigate the PDP of the circuits with circuit simulation, or consider the transistor count.

### 4 Conclusion of literature review

There are multiple methods for designing circuits, such as the static gate design with pull-up and pull-down networks, circuits built from unary gates and voltage-averaging capacitor, circuits based on MIN and MAX gates, and circuits built on ternary-valued 1-trit multiplexers. Additionally, circuits may be designed using LUT-cascades such as the radix converter design method proposed in [52]. The research done in regards to arithmetic is mainly focusing on unbalanced ternary as opposed to balanced ternary. An alternative technology, the novel two-dimensional material of [50], may challenge the CNTFET circuits, as they claim to have a 50% reduction in transistor count compared to circuits with CNT and silicon based devices.

Mainly two methods for radix conversion has been proposed, which are the LUT-cascade design and the arithmetic decomposition design. Binary to unbalanced ternary radix conversion circuits and reverse have been implemented in simulation. No CNTFET circuit implementations of 8-bit binary to 6-trit **balanced** ternary was found.

The papers examined in the literature review have not shown a proven improvement over binary logic, although some research indicate that interconnect density may be significantly lower than binary-valued circuits for some ternary-valued circuits such as a multiplier circuit. Furthermore, there are be technologies which encode ternary values in binary, and which could possibly benefit from implementing natively ternary values. However, existing ternary-valued logic circuits in CNTFET circuit research generally have a higher PDP and transistor count compared to equivalent binary circuits, for the purposes of adding.

### Chapter 4

# Logic Synthesis and Circuit Design

In this chapter, the different designs and methods of constructing ternary-valued circuits are explored. Furthermore, the synthesis of the static gate design is automated, along with our SIMS 2020 paper.

### 1 Circuit design methodologies

Multiple design methods to achieve a circuit for logic functions have been considered. These design methods may rely on some gate-level circuit design, as well as transistor-level circuit design. As an example, ternary logic algebra may be used to break a large function into smaller function in the gate-level design, however it does not take into account the transistor-level design or optimizations thereof.

### 1.1 Capacitor-aided circuits

If we allow the use of capacitors, we can achieve circuits such as a ternary full adder with unary functions. These types of circuits work by using capacitors to take the average of multiple voltages, which can be processed by simple unary functions with shifted voltage threshold to achieve the specific function. Figure 4.1 shows one possible example to achieve different types of full adder circuits, such as unbalanced or balanced.

While the transistor count and delay of this circuit may outperform other designs, it has a very severe flaw of a high current leakage through the capacitors at high input frequencies. Current can flow between the inputs, as well as from the inputs to  $V_{DD}$  and GND within the unary functions, and through the two  $C_2$  capacitors. Furthermore, capacitors take up quite a lot of space on a chip. Both the size and the current can be remedied by reducing the size and capacitance of the capacitors, however this limits their ability to produce sufficient output voltages.

Figure 4.1: Capacitor-aided ternary circuit

### 1.2 Static gate design with pull-up and pull-down

The static gate design is a highly versatile and reliable circuit design which can achieve any ternary-valued logic function. It uses complementary transistor networks to pull the output voltage to high or low, or the middle voltage by dividing the voltage between the two transistors in the half- $V_{DD}$  path, which is from an active pull-up network to an active pull-down network.

These 4 transistor networks are binary in function in the sense that they either do or do not connect the output to  $V_{DD}$  or GND. However, with variations in the diameters of the transistors within the network, in combination with NTI and PTI inverters on the inputs, a binary-valued truth table encompassing all combination of the ternary-valued inputs can be achieved.

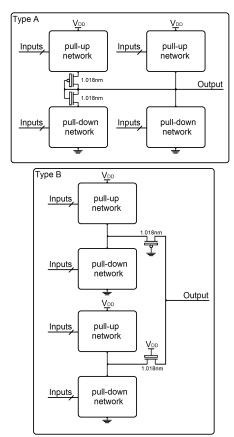

Two types of the static gate design were identified [48][32], as shown in figure 4.2. Type A utilizes two transistor networks purely for the middle value, and two for the binary high and low output values. To limit the leakage current, the two pairs of networks have to be cross-wise exclusive of each other, i.e. no open path between  $V_{DD}$  and GNDwith the exception of voltage division, which results in a higher transistor count required. Type B functions in a similar manner to the commonly used design for the STI inverter. The top pair of networks generate an output analogous to the NTI part of an STI, while the bottom pair of networks are as the PTI part. Unlike type A, the networks are not at risk for cross-wise current leakage, however as neither pair of transistor networks can be active simultaneously, the same restrictions occur, giving the same increase in required transistors.

Type A and type B of the static gate design are found to be approximately equivalent in terms of transistor count, power consumption, and signal delay, and both designs can commonly be found in ternary-valued circuit design and research.

Within each network, the binary-output truth table with ternary inputs is achieved through the 4 transistor configurations shown in figure 4.3 from from [48]. For pull-up networks, p-type transistors are used, while n-type transistors are used for pull-down networks. Within each transistor network, 4 configurations of transistors can be connected in series to form a n-dimensional rectangle on the circuit truth table, which in parallel builds the whole truth table.

**Figure 4.2:** Static ternary gate design type A and type B

| Ternary device switching table |                                      |                                      |                                                    |                                      |  |  |  |  |  |

|--------------------------------|--------------------------------------|--------------------------------------|----------------------------------------------------|--------------------------------------|--|--|--|--|--|

| Pull-up<br>network             | (19, 0)<br>I                         | (10, 0)<br>I                         | (19, 0)<br>I <sub>N</sub> -<br>0.289 V<br>1.487 nm | (19, 0)<br>Ip<br>0.289 V<br>1.487 nm |  |  |  |  |  |

| Pull-down<br>network           | (19, 0)<br>Ip<br>0.289 V<br>1.487 nm | (19, 0)<br>IN<br>0.289 V<br>1.487 nm | (19, 0)<br>I<br>0.289 V<br>1.487 nm                | (10, 0)<br>I<br>0.559 V<br>0.783 nm  |  |  |  |  |  |

|                                | Swi                                  | itching opera                        | tion                                               |                                      |  |  |  |  |  |

| Input = 0                      | ON state                             | ON state                             | OFF state                                          | OFF state                            |  |  |  |  |  |

| Input = 1                      | ON state                             | OFF state                            | ON state                                           | OFF state                            |  |  |  |  |  |

| Input = 2                      | OFF state                            | OFF state                            | ON state                                           | ON state                             |  |  |  |  |  |

| Operator                       | $A_{\theta}^{+}A_{I}$                | $A_{\theta}$                         | $A_1 + A_2$                                        | $A_2$                                |  |  |  |  |  |

Figure 4.3: Transistor switching table

### 1.3 Ternary Algebra with static gate base-functions

With the use of select base-functions, all ternary logic can be achieved. This method relies on the basic logic functions used in ternary logic algebra, the transistor circuits of which must be designed using some other method. Ternary logic algebra allows gate-level design of circuits, building on these base functions. As an example, the balanced sum gate can be constructed. The truth table is shown in table 4.1. While ANY and CON are simple to implement, the sum function inherently has a much higher complexity, due to the alternating values in the truth table. Therefore, we can use basic functions to achieve the sum function. The SOP form can be written as in equation 4.1. As 0 is equivalent to false, terms 2, 4, and 9 can be removed, as they will not contribute to the output. From equation 4.2, in terms 5 and 6,  $(b=1) \wedge 1$  and  $(b=2) \wedge 2$  can both be replaced with b. In a similar fashion, in terms 1 and 3,  $(b = 0) \land 2$  and  $(b = 2) \land 1$  can be replaced with (b - 1), and in terms 7 and 8,  $(b = 0) \land 1$  and  $(b = 1) \land 2$  is replaced with (b + 1), which results in equation 4.3. From here, there are 3 terms being repeated twice. Thus it is reduced to equation 4.4. The resulting gate-level design of the sum gate is shown in figure 4.4.

Figure 4.4: Basic gate-based balanced sum

| Table  | 4.1:  | Truth  | ta- |

|--------|-------|--------|-----|

| ble of | balan | ced su | m   |

| a | b | sum |

|---|---|-----|

| 2 | 2 | 0   |

| 2 | 1 | 2   |

| 2 | 0 | 1   |

| 1 | 2 | 2   |

| 1 | 1 | 1   |

| 1 | 0 | 0   |

| 0 | 2 | 1   |

| 0 | 1 | 0   |

| 0 | 0 | 2   |

$$\begin{aligned} + b &= ((a = 0) \land (b = 0) \land 2) & [term1] \\ &\lor ((a = 0) \land (b = 1) \land 0) & [term2] \\ &\lor ((a = 0) \land (b = 2) \land 1) & [term3] \\ &\lor ((a = 1) \land (b = 0) \land 0) & [term4] \\ &\lor ((a = 1) \land (b = 1) \land 1) & [term5] \\ &\lor ((a = 1) \land (b = 2) \land 2) & [term6] \\ &\lor ((a = 2) \land (b = 0) \land 1) & [term7] \\ &\lor ((a = 2) \land (b = 1) \land 2) & [term8] \\ &\lor ((a = 2) \land (b = 2) \land 0) & [term9] & (4.1) \end{aligned}$$

$$\begin{array}{lll} a+b=((a=0)\wedge(b=0)\wedge2) & [term1] & a+b=((a=0)\wedge(b-1)) & [term1] \\ & \lor((a=0)\wedge(b=2)\wedge1) & [term3] & \lor((a=0)\wedge(b-1)) & [term3] \\ & \lor((a=1)\wedge(b=1)\wedge1) & [term5] & \lor((a=1)\wedgeb) & [term5] \\ & \lor((a=1)\wedge(b=2)\wedge2) & [term6] & \lor((a=1)\wedgeb) & [term6] \\ & \lor((a=2)\wedge(b=0)\wedge1) & [term7] & \lor((a=2)\wedge(b+1)) & [term7] \\ & \lor((a=2)\wedge(b=1)\wedge2) & [term8] & (4.2) & \lor((a=2)\wedge(b+1)) & [term8] & (4.3) \end{array}$$

a

$$a + b = ((a = 0) \land (b - 1)) \lor ((a = 1) \land b) \lor ((a = 2) \land (b + 1))$$

$$(4.4)$$

The basic functions needed, being the unary functions of equality, increment and decrement, and the binary functions of MAX and MIN, can be generated with the logic synthesizer using the static gate circuit design method.

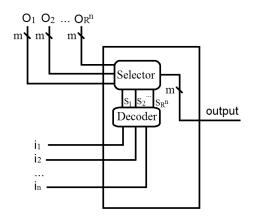

### 1.4 MUX-based LUT circuit

By utilizing multiplexer(MUX) circuits on the inputs as selection digits, the multi-digit output can be connected to a selection of sets of predefined values in the form of a look-up table(LUT). This method allows for circuits with n inputs and m outputs. The selection of outputs can be hard-wired voltages, outputs from other circuits, or the inputs themselves. Alternatively, it can be read from a configurable memory, making it a universal programmable function. Figure 4.5 shows the concept of a MUX-based n-input m-output circuit. While these types of circuits are generally fast, they require a large circuit which may result in a high passive current. In the general case, the number of selectable outputs is equivalent to the number of possible input combinations, and each selectable output combination can have a variable number of digits regardless of number of digit inputs. Since the multiplexing circuit can become exponentially complex for a high number of inputs, this circuit is mainly applicable for a smaller number of inputs. The MUX consists of decoders of the inputs, which check if each digit input is a specific value. This is done with the 3 equality functions. These decoders can give 3 outputs, to activate one of 3 inputs, as shown in figure 4.6.

Figure 4.5: General MUX-based circuit

Figure 4.6: 1-trit MUX

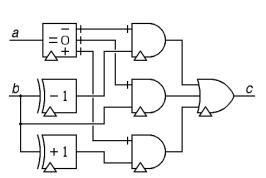

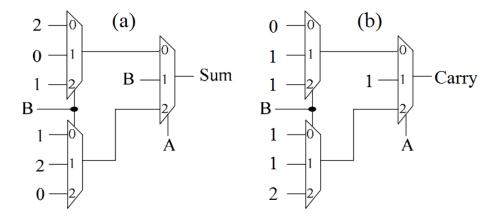

These 1-trit MUX circuits can be connected to create more complex functions. As an example, the sum function can be constructed. Based on the logic algebra equation for the sum function, shown in equation 4.4, the MUX circuit can be constructed, and similarly the same can be done for the carry, also known as consensus, based on equation 2.14 as in figure 4.7.

Figure 4.7: Balanced sum (a) and carry MUX (b) circuits

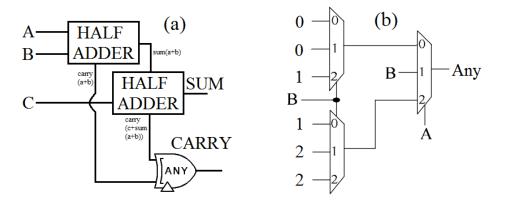

With these two circuits, a half adder can be constructed, and by extension a full adder with the "Accept Any" circuit, as shown in figure 4.8.

Figure 4.8: Balanced full adder circuit (a) with any MUX circuit (b)

One interesting observation to make here is that any 2-input function can be created with this method, however with a relatively high transistor count, as each 1-trit MUX requires 36 transistors to operate.

The decoder circuit for a 1-trit MUX consists of the 3 equality functions. This decoder circuit can be extended to n trits with the addition of 1-trit MUX circuits, as shown in figure 4.9 with an example of a 2-trit decoder with 9 output signals.

Figure 4.9: 2-trit decoder extension of the 1-trit decoder

It is clear that the increase of trits in the decoder brings an exponential growth of circuit complexity, and it's therefore ill-advised to use these multi-trit decoders over the alternative of a combination of 1-trit MUXes based on the ternary logic algebra of the function, as was demonstrated with figures 4.7 and 4.8.

Paper [52] utilizes a cascade of LUT circuit, which are optimized using column multiplicity of the truth table, i.e. how many duplicate columns can be found in different configurations of the specific function truth table. This method can also be used to design a circuit.

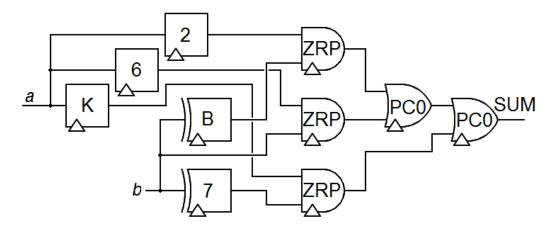

### 2 Risto et al. 2020

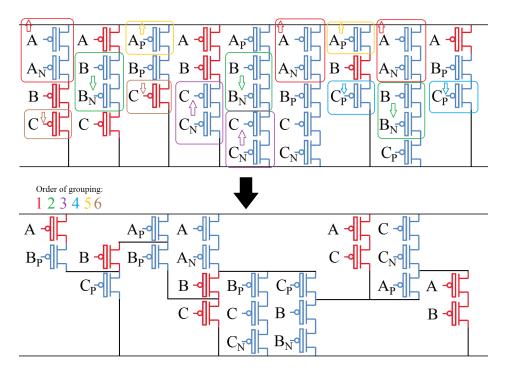

In our research paper "Automated synthesis of netlists for ternary-valued n-ary logic functions in CNTFET circuits", accepted in the SIMS 2020 research conference[62], we presented an open-source ternary-valued logic synthesizer for the transistor-level design using the static gate design, which generates design files for simulation, with CNTFET logic circuits from a truth table with up to 7 inputs, i.e. functions with arity up to 7. We also proposed an indexing system for the logic functions generated, which makes gate-level design much more convenient, as any circuit generated by a specific logic synthesizer can be referenced by an index without the need for a truth table or circuit diagram. Furthermore, we proposed the usage of a combination of different arities of function in a circuit. As an example, we compared three balanced full adders; Purely non-compound, traditional compound, and a hybrid of the two. Using simulation results to compare the three, the hybrid circuit outperformed the two others.

### 2.1 Function Indexing

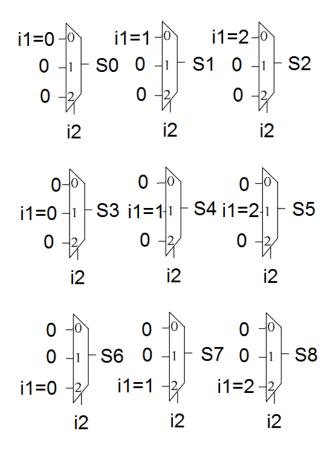

Due to the large quantity of possible logic functions in ternary logic, we proposed an indexing system, which makes use of the base-27 heptavintimal notation shown in table 4.2.

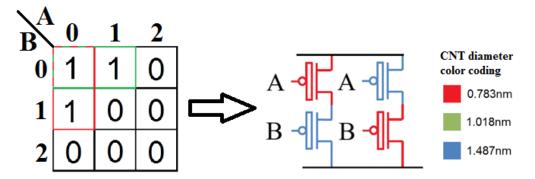

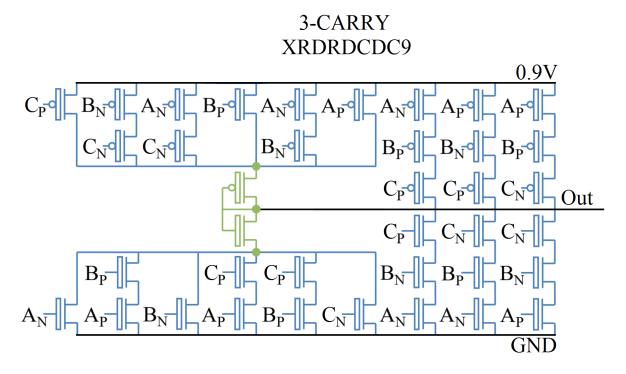

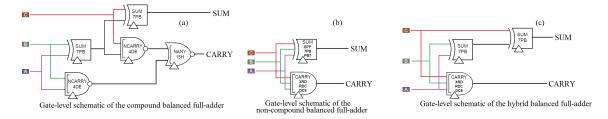

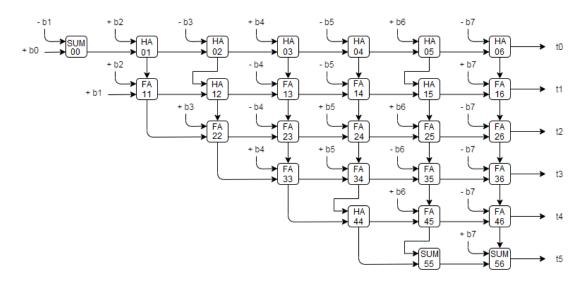

With the heptavintimal notation, 3 trits can be expressed with a single character, which is analogous to hexadecimal encoding of bits in binary logic.