# Ultrasound Transmit-Receive Electronics: Study and Upgrade

Sudha Shrestha

Department of Micro and Nano System Technology, Buskerud and Vestfold University College, Norway  $_{\rm May\ 2014}$

We are stuck in technology when what we really want is the stuff that work. -Douglas Adams.

#### Abstract

The ultrasonic investigation using transmission of ultrasounds and receiving of the back-scattered echoes is a recognized measurement technology since from the decades. One of the heavy and bulky instrumentation parts in a conventional ultrasound transmit-receive system are the function generators along with power amplifiers required to provided appreciable signal for ultrasound transducer excitation. Technology today where miniaturization has become the prime essence, system design in digital hardware by exploiting programmable logic devices is attractive. This work presents the ultrasound transmit-receive instrumentation designed for flexible user interface, portability and ability to be adopted in various types of ultrasound interrogation. The preliminary design of the ultrasound transmitter using a complex programmable logic device has been accomplished. The essential features for making Doppler velocity measurement has been considered in the system design. Some primary acoustic measurement made with the designed instrumentation is illustrated here. The flexibility, challenges and possible upgrade of the design instrumentation for various field of applications is also discussed in the work.

## Acknowledgements

I want to show my sincere acknowledgements to my supervisor Professor Lars Hoff who introduce me with the subject matter. Thanks for his guidance, encouragements and productive discussions. I am sincerely oblige for his cooperation and guidance along the way.

I will also like to express my gratitude to Svein Husa and Lecturer Rune Langy for sharing their knowledge and helping me throughout the work. Thanks to PhD. students Thai Anh Tuan Nguyen and Grundge Wagg for their occasional help and discussion. Thanks to my fellow students for making my time worthwhile and providing a courteous company.

I also want to remember my family for their unconditional love, support and appreciation throughout my life. Its their unconditional love and nurture that helps me become a better individual.

## Contents

| 1        | Intr | roduction                                                                                                                                        | 1  |  |  |  |  |  |

|----------|------|--------------------------------------------------------------------------------------------------------------------------------------------------|----|--|--|--|--|--|

|          | 1.1  | Ultrasound Overview                                                                                                                              | 1  |  |  |  |  |  |

|          | 1.2  | Imaging Modes                                                                                                                                    | 6  |  |  |  |  |  |

|          | 1.3  | Electronics Surrounding Ultrasound System                                                                                                        | 7  |  |  |  |  |  |

|          | 1.4  |                                                                                                                                                  |    |  |  |  |  |  |

|          |      | tion Language (VHDL)                                                                                                                             | 10 |  |  |  |  |  |

|          | 1.5  | Function Generator                                                                                                                               | 10 |  |  |  |  |  |

|          | 1.6  | Ultrasound Transducer                                                                                                                            | 11 |  |  |  |  |  |

| <b>2</b> | Sys  | tem Description                                                                                                                                  | 15 |  |  |  |  |  |

|          | 2.1  | Background                                                                                                                                       | 15 |  |  |  |  |  |

|          | 2.2  | System Hardware                                                                                                                                  | 15 |  |  |  |  |  |

|          |      | 2.2.1 Transmitter Board $[1]$                                                                                                                    | 16 |  |  |  |  |  |

|          |      | 2.2.2 Transmit-Receive Switch                                                                                                                    | 20 |  |  |  |  |  |

|          |      | 2.2.3 Receiver $[2]$                                                                                                                             | 22 |  |  |  |  |  |

|          |      | 2.2.4 Oscillator and Gain Board                                                                                                                  | 24 |  |  |  |  |  |

|          |      | 2.2.5 Power Supply Board                                                                                                                         | 25 |  |  |  |  |  |

|          |      | 2.2.6 Data Acquisition using Analog to Digital Converter                                                                                         |    |  |  |  |  |  |

|          |      | $(ADC) [3] \ldots \ldots$ | 26 |  |  |  |  |  |

|          | 2.3  | Transducer                                                                                                                                       | 27 |  |  |  |  |  |

|          | 2.4  | Software Tools In The Design                                                                                                                     | 27 |  |  |  |  |  |

|          | 2.5  | Limitations of Designed System                                                                                                                   | 30 |  |  |  |  |  |

| 3        | Exp  | periment Method                                                                                                                                  | 33 |  |  |  |  |  |

|          | 3.1  | Experiment Setup                                                                                                                                 | 33 |  |  |  |  |  |

|          | 3.2  | Using Integrate Software Environment (ISE) Tool                                                                                                  | 34 |  |  |  |  |  |

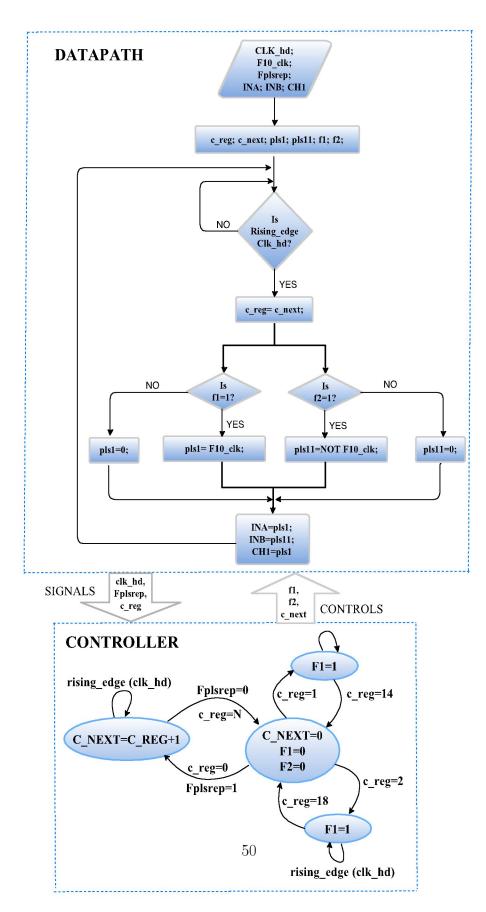

|          | 3.3  | Synthesizeable Design for Ultrasound Transmitter Electronics                                                                                     | 37 |  |  |  |  |  |

|          | 3.4  | Transmitter Board Design                                                                                                                         | 44 |  |  |  |  |  |

|          | 3.5  | Transmit-Receive $(T/R)$ switch Design $\ldots \ldots \ldots \ldots \ldots$                                                                      | 45 |  |  |  |  |  |

|          | 3.6  | Oscillator and Gain Board Design                                                                                                                 | 46 |  |  |  |  |  |

|          | 3.7  | Power Supply                                                                                                                                     |    |  |  |  |  |  |

|          | 3.8  | Ultrasound Receiver                                                                                                                              | 47 |  |  |  |  |  |

|          | 3.9  | ADC                                                                                                                                              | 48 |  |  |  |  |  |

| 4        | Exp  | periment Result                                                                                                                                  | 53 |  |  |  |  |  |

|          | 4.1  | Simulation In ISE Tool and Digital Design with VHDL $\ . \ . \ .$                                                                                | 53 |  |  |  |  |  |

|          | 4.2  | Real Time Measurement Using Oscilloscope                                                                                                         | 55 |  |  |  |  |  |

|              | 4.3  | Measurement Interfaced with Personal Computer (PC) $\ldots$ | 58 |

|--------------|------|-------------------------------------------------------------|----|

| <b>5</b>     | Dis  | cussion                                                     | 61 |

| 6            | Cor  | clusion And Future Work                                     | 65 |

| $\mathbf{A}$ | ppen | dices                                                       | 67 |

# List of Figures

| 1  | Sound wave propagation; Longitudinal wave (Left), Trans-                           |    |

|----|------------------------------------------------------------------------------------|----|

|    | verse wave (Right). $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 1  |

| 2  | Block diagram of conventional analog function generator (left)                     |    |

|    | and the digital waveform generator (right)                                         | 11 |

| 3  | Single element ultrasound transducers                                              | 12 |

| 4  | Ultrasound Beam from single element transducer                                     | 12 |

| 5  | The overall system block diagram                                                   | 16 |

| 6  | The ultrasound transmit-receive system block diagram                               | 17 |

| 7  | The MD1210DB transmitter board [1]                                                 | 18 |

| 8  | The MD1210DB transmitter board circuit diagram [1]                                 | 19 |

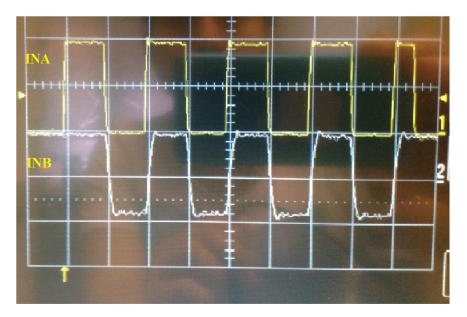

| 9  | The outputs INA and INB from the Complex Programmable                              |    |

|    | Logic Device (CPLD).                                                               | 19 |

| 10 | The transmit-receive switch Printed Circuit Board (PCB)                            | 21 |

| 11 | The transmit-receive switch circuit diagram                                        |    |

| 12 | The receiver board                                                                 |    |

| 13 | The receiver board                                                                 |    |

| 14 | The oscillator and gain board                                                      | 25 |

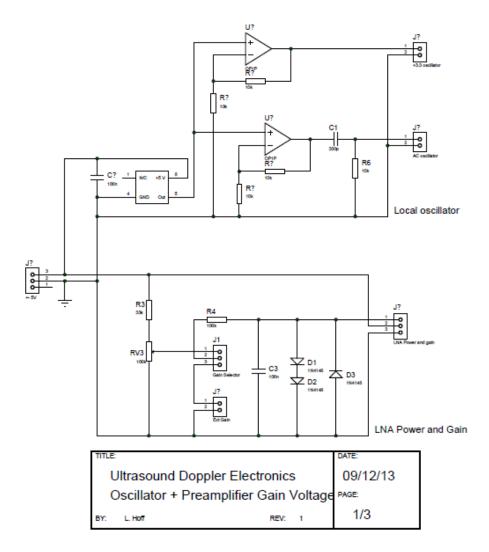

| 15 | The oscillator and gain board circuit diagram.                                     |    |

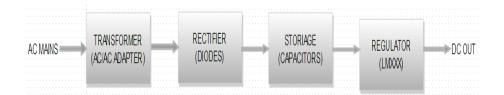

| 16 | Linear Power Supply                                                                |    |

| 17 | The analog to digital converter                                                    |    |

| 18 | Single element ultrasound transducers                                              |    |

| 19 | The Ultrasound Test Setup with the designed system                                 |    |

| 20 | The output waveform of the transmitter                                             |    |

| 21 | Design Flow                                                                        |    |

| 22 | Design properties                                                                  |    |

| 23 | Resource utilization of CPLD                                                       |    |

| 24 | The RTL flow of VHDL design                                                        | 39 |

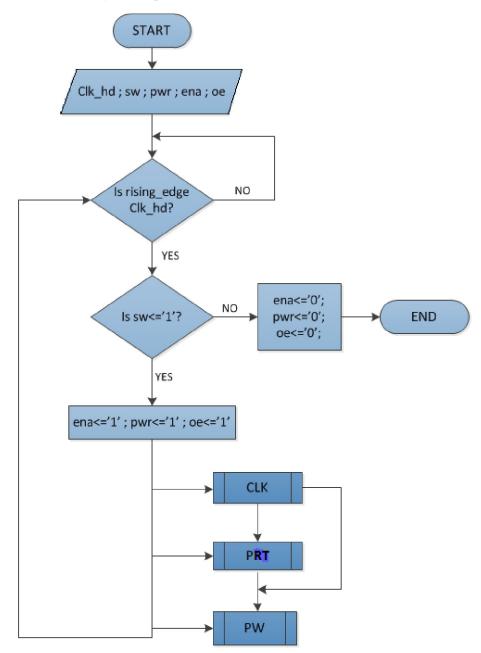

| 25 | Flow chart of the MAIN module                                                      |    |

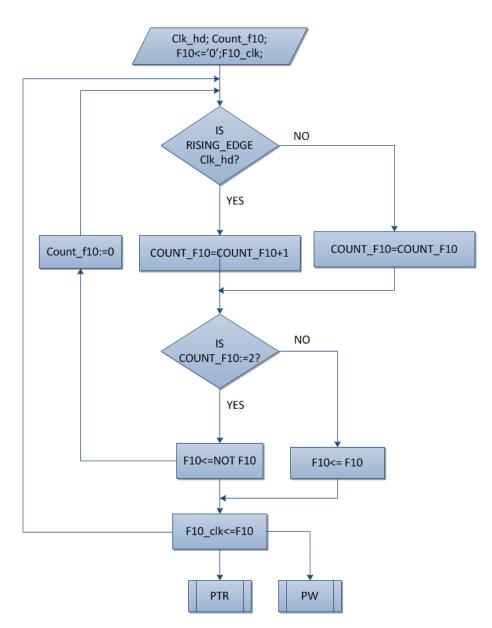

| 26 | Flow chart of the CLK module                                                       | 42 |

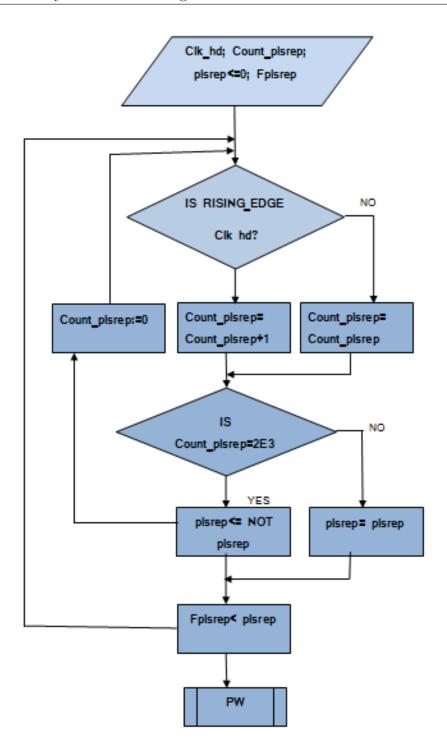

| 27 | Flow chart of the PRT module                                                       | 43 |

| 28 | The pulse lenght of four cycles.                                                   |    |

| 29 | The regulated power supply board block diagram                                     |    |

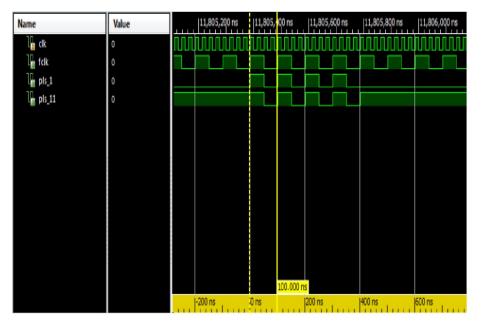

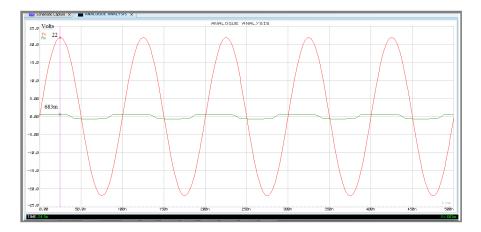

| 30 | The behaviour simulation                                                           | 53 |

| 31 | The behaviour simulation                                                           |    |

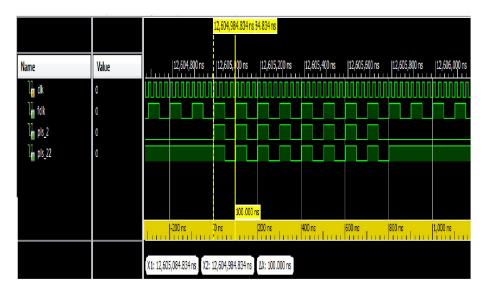

| 32 | CPLD output of 4 pulse cycle                                                       |    |

| 33 | CPLD output of 8 pulse cycle                                                       |    |

| 34 | Synchronization clock and transmitted Pulsed Wave (PW)                             |    |

|    | outputs                                                                            | 57 |

| 35 | Ultrasound measurement in LabView                                                  |    |

| 36 | M-mode ultrasound investigation for 1 MHz single element |    |

|----|----------------------------------------------------------|----|

|    | transducer in water                                      | 59 |

| 37 | Oscillator and gain board reference circuit [4]          | 74 |

| 38 | The simulation of $T/R$ switch in Protetus               | 75 |

## List of Tables

| 1 | Examples of some pulsers                     | 11 |

|---|----------------------------------------------|----|

| 2 | Logical States                               | 20 |

| 3 | Design specifications for power supply board | 27 |

## 1 Introduction

This section introduces the theory behind the Ultrasound and its instrumentation briefly along with short description of some of its field of application and the limitations challenged by the system. The more digging and discussion of ultrasound building block instrumentation is done in the sections following it.

### 1.1 Ultrasound Overview

Acoustic inspection goes way behind in the history regarding search and testing purposes. Starting with the general sense of hearing the perception of acoustics has reached a wider dimension now, connecting it to mechanical vibrations, Sound Navigation And Ranging (SONAR), seismic noise and ultrasounds. Acoustic waves found its importance preliminary in SONAR and underwater research and search system. Due to its non-invasive nature it is greatly valued for materials flaws detection, testing and also in sensitive field like medical diagnosis. Moreover, the development of ultrasound imaging system came forth along with introduction of Radio wave Detection And Ranging (RADAR) which works in the principle of electromagnetic wave propagation.

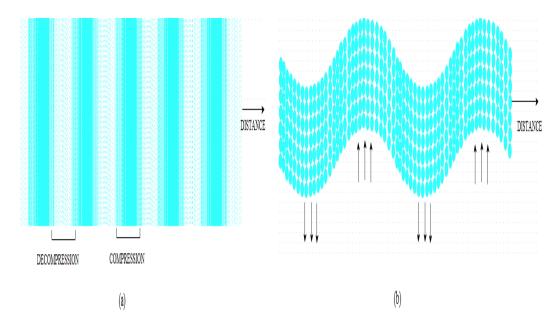

Figure 1: Sound wave propagation; Longitudinal wave (Left), Transverse wave (Right).

#### 1 INTRODUCTION

Ultrasound is generally described as the sound waves with frequencies above the audible range (15-20 KHz). The sound wave can be basically of two types; longitudinal wave and transverse or shear wave. For the first type, the particles in the medium of wave propagation vibrates along the direction of the wave motion or distance creating the pressure difference in the medium known as compression and decompression. They are often known as the pressure waves (P-wave) and are exclusively used in all ultrasound measurements undertaken in fluids. For latter type i.e. S-wave, the particle vibrates in the perpendicular direction of the wave propagation and comprises for the acoustic wave only in solid medium. This two fundamental phenomenon of the sound wave propagation is illustrated in Figure 1. In general the acoustic wave energy is possessed by the oscillation of the particle of the medium around the equilibrium position. It can be viewed as the mechanical vibration of the medium through which it propagates. Since the phenomenon of acoustic wave follows the law of conservation of mass and momentum along with consideration of the density  $\rho$  and the adiabatic compressibility k of the medium though which it propagates, velocity of sound wave(c) is given as in Equation 1[5]. It illustrates that the velocity of sound wave propagation depends on the material through which it travels.

$$c = \sqrt{\frac{1}{\kappa\rho}} \tag{1}$$

Further, the velocity c of acoustic wave propagation can be related to its the frequency oscillation f and the corresponding spatial period of the wave  $\lambda$  as shown by Equation 2. Here the frequency f of the oscillation being inversely proportional to its period  $\lambda$ , it implies that the velocity of wave propagation c increases directly with increase in its oscillation frequency. Then considering the physics of Radio Frequency (RF) wave propagation tells that the attenuation of the wave is considerable with the increase in frequency or short  $\lambda$  i.e. the acoustic wave dies out along the depth of its propagation in the target. But the higher frequency is desired for achieving better spatial resolution during signal processing. Thus trade-offs remains in the depth penetration and spatial resolution provided by specific RF wave.

$$f = \frac{c}{\lambda} \tag{2}$$

In general the principle of ultrasound measurement system is based on the measurement of ultrasound echoes, transmitted or reflected from the stationary or moving targets. The phenomenon of reflection of ultrasound arises due to the variation in the characteristic acoustic impedance of the materials through which the ultrasound wave propagates. The characteristic acoustic impedance is described as the ratio of acoustic pressure P at a point in the medium to the particle speed at the same point u [6] as given in Equation 3.

$$Z = \frac{P}{u} \tag{3}$$

It can also related to mass density  $\rho$  of the medium to the ultrasonic wave of velocity c as given in Equation 4[5].

$$Z = \sqrt{\rho c} \tag{4}$$

It is worthwhile to mention some of the major fields of application for ultrasound technology which will give glimpse of its evolution and approaches.

- Ultrasound For Underwater: Acoustic waves dominates in underwater communication (detection and location ) analogized to the electromagnetic waves for land communication. The reason being quite obvious that they being the mechanical waves are less attenuated in seawater than the electromagnetic radiation which are heavily attenuated by the salt water. For instance, study of the seabed topography, oceanographic conditions, underwater communications with ships and submarines, classification and detection of fish and mines are some of the numerous applications achieved by use of ultrasounds for underwater investigation.

- Ultrasound For Medicine: Ultrasonic diagnosis is widely used in field of medicine due to its minimal side effects. Ultrasonic which is the term use for ultrasound in medical diagnosis is the ongoing field where approaches are developed year after year to make the imaging practice in medicine more efficient, both qualitatively and quantitatively. Medical diagnosis using ultrasound imaging is preferred method among the available technology, such as X-ray, Nuclear or Magnetic ultrasound imaging because of its non-invasive nature, capability of real time imaging, soft tissue and blood flow imaging [7]. Also the low cost and ease of building equipment requirements makes it more attractive. Ultrasonography or the ultrasound imaging in medical term is the well know term in the field of medical diagnosis for the evaluation of the heart, blood vessels, neonatal brain, glands, breast, organs of abdomen and pelvis [7]. Although advance electronic instrumentation and signal processing has been developed in the field of medical ultrasound imaging, the

limitation still remains as ultrasound cannot penetrate through bone setting limitations on chest and abdominal imaging as the ultrasound imaging cannot be performed in air [5].

- Ultrasound For NDT : Ultrasound technology has been extensively used in Non-Destructive Testing (NDT) as for examples; ultrasonic flaw detection, material characterization, pipeline inspection, surface testing for fatigue and environmental cracking in the civil engineering structures. In the last decades various acoustic or ultrasonic system has come forth as a successful NDT system, for instance air-coupled system, optical interferometric detection, laser generation, non-contact acoustical transducers and hybrid combination of the above [8]. Traditional ultrasound system mostly uses some fluids as a coupling media between the ultrasound transducer and the target, since they provides better coupling and low damping for ultrasound transmission. This has been established as an exclusive measure in making ultrasound measurement. Today approaches and researches are being ongoing extensively in the field of air-coupled ultrasound system which uses air as the coupling medium between ultrasound transducer and the target. Air coupled ultrasound has physical importance for NDT as they provide possibilities for the tests to be performed under hostile and inaccessible geometries. Also they are valued for noninvasive and non intrusive measure in the measurement process. It provides ease in ultrasound measurement process as the coupling medium like fluids for acoustic impedance matching is not crucial here. As to mention some examples, it is valued greatly in the measurement of the operating condition within the industrial process plant, particularly in nuclear and chemical industry for pure and sterile processes [9]. But the challenges remains as air-coupled ultrasound induces high acoustic impedance mismatch in the ultrasound measurement. such system demands for high level signal for ultrasound transducer excitation to provide acceptable level of Signal to Noise Ratio (SNR). They require more scientific research and extensive verification before being standardized as a ultrasonic NDT measure.

- Ultrasound For Velocity Measurement: The measurement of velocity of fluid flow using ultrasound is done using PW or Continuous Wave (CW). The PW and CW ultrasound measurement system is often known as Doppler measurement as they exploits some artifact of the Doppler effect. The Doppler Effect comes from the sense when investigating the frequency of the back scatter signal from the moving

target. Since, for the moving target the frequency of the back scattered signal is altered from the transmitted frequency, there is a Doppler shift in the received frequency as shown by the following Equation 5[5]:

$$f_d = \frac{2 f_o v \cos\theta}{c} \tag{5}$$

Where,  $f_d$  is the Doppler shift,  $f_o$  is the frequency of the transmitted ultrasound beam, c the ultrasound wave velocity, v velocity of scatter and  $\theta$  is the angle between the ultrasound beam transmission and the velocity direction of the flow. The CW ultrasound instrument uses this Doppler effect to detect the moving object which scatters the ultrasound wave e.g blood [6]. Here, the ultrasound wave is continuously transmitted from one crystal of the transducer element and the back-scatter ultrasound echoes from the target is continuously received by another crystal in the transducer element [6]. The received signal when multiplied by the transmitted (CW) signal followed by the low pass filtering results a signal with frequency being proportional to the velocity of the moving target [6]. This method of using CW for velocity measurement does not put any limitation on the maximum velocity measurable but the drawback remains in its inability to provide the range resolution in the velocity measurement of the moving targets i.e. the inability to distinguish between the two nearby targets or to give the accurate direction of the flow.

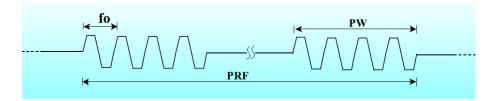

On other hand the PW ultrasound system does not employ the Doppler frequency shift of the ultrasound echoes to detect the velocity of the moving target. In PW ultrasound the pulse burst of ultrasound is transmitted often using a single element ultrasound transducer and the back-scattered ultrasound echoes received by the same element [6]. The sampling is actually performed once for every pulse transmission which implies that the sampling frequency of the PW ultrasound signal corresponds to the Pulse Repetition Frequency (PRF) of the transmitter. Hence, the shift in the position of the scatter is detected here rather than the shift in the transmission frequency. Mover over, as requirement of the Nyquist criteria for the error free reconstruction of the sampled signal, the ultrasound frequency  $f_o$  given in Equation 8 must be less than half of the sampling frequency i.e the (PRF). This criteria to avoid the frequency aliasing in Doppler measurement is given in relation 6.

$$f_o < \frac{PRF}{2} \tag{6}$$

The limitation put forth by Nyquist limit shown in Equation 6 is on the bandwidth of the Doppler signal i.e the PW of ultrasound ultrasound and the maximum measurable velocity. As the limitation put forth by the Nyquist limit (6), aliasing in the velocity measurement is given in Equation 7 [5] which directly relates to the PRF or the sampling frequency. Often the low PRF doppler is preferred to have better range resolution while the high PRF Doppler is for measuring higher velocities. An appropriate choice of pulse width PW, PRF or Pulse Repetition Time (PRT) for the Doppler signal forms the state-of-art for the instrumentation in the Doppler measurement.

$$V_a < \frac{PRF c}{4 f_o \cos\theta} \tag{7}$$

In the Doppler velocity measurement using PW, as the imaging is done in local range using short pulse, the PW ultrasound measurement gives good range resolution in the velocity measurement of the target. Hence, it is often use as an exclusive method for velocity measurement e.g color flow imaging [6]. The main drawback here is the limitation on the maximum measurable velocity as aliasing will be encountered for the higher velocity of the target. The relation of the maximum velocity limit in the PW ultrasound of ultrasound frequency  $f_o$  with velocity of ultrasound in the target c from the maximum range D is given in relation 8:

$$V_{max} = \frac{c^2}{8 f_o D K} \tag{8}$$

Here, K is the correction factor for allowing the reverberations of backscatter ultrasound to disappear (K is normally choosen in range 2 to 5) [6]. Hence, lowering the frequency  $f_o$  of the ultrasound signal is desirable for higher velocity measurement. As shown in Equation 5, the Doppler shift is directly related to the radial velocity component  $V\cos\theta$ , it allows the measurement of the velocity of the range cell as long as the beam transmission perpendicular to the velocity direction is avoided.

#### 1.2 Imaging Modes

The brief description of some of the different imaging modes that has been developed in ultrasound imaging are mentioned below:

- •A-Mode: The earliest ultrasound imaging mode developed is the A-mode imaging which use the intensity or amplitude of the ultrasound echoes received. The ultrasonic pulse is transmitted into the target and the back-scattered signal are picked by the same transducer which forms the one dimensional line image [5].

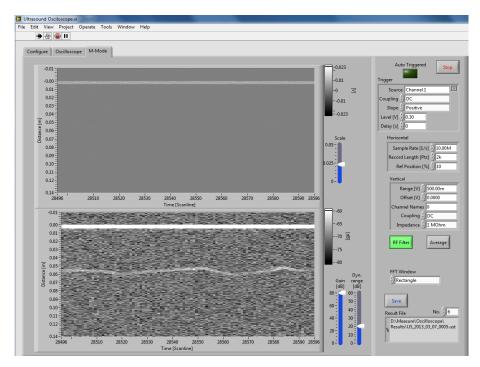

- •M-Mode: M-mode is the motion mode in which the received echoes are plotted against time. So it displays the echoes to image the target that are not static as for example heart [5]. Here, the depth in the target is displayed along one axis with respect to the time in other axis and the amplitude of the back scattered signal is shown in the gray scale.

- •B-Mode: In B-mode imaging the intensity or amplitude of the received ultrasound echoes are displayed as the brightness of the image formed. It is the two dimensional amplitude imaging of the ultrasound signal where the amplitude of the back-scattered signal is coded in gray scale along the axis of beam direction on the display [5].

- •Doppler-Mode: The common Doppler mode can be either PW or CW as described before in section 1.1. Other Doppler modes like as Multi Range Gated (MRG) also exist but is seldom used in ultrasound system which already include gain control in its instrumentation.

- •Three Dimension (3D)-Mode: The 3D ultrasonic imaging being proposed already in 50's provides efficient processing and visualization of the image model with the aid of morden computer display technology [5]. The 3D image is formed by collection of many Two Dimension (2D) image scan lines. Thus, it is a rather slower mode for moving targets since it takes considerable amount of time to collect data for image formation.

Conventional ultrasound system possess some inherent uncertainties since the imaging model are assumed planar while the ultrasound beam reaches considerable thickness (approximately 10mm). Even performing 3D imaging, the chances of error still holds as the images are extremely prone to speckle noises and uncertain imaging artifacts. Also, error in the instrumentation or calibration inaccuracies adds significant error. As for instance, a constant speed of sound assumption and envelope sampling of the RF data [10].

#### **1.3 Electronics Surrounding Ultrasound System**

The principle of ultrasound imaging had been established very early in the history but the underlying instrumentation corresponding for different application desired is still the field of research and development. Looking back in the past, ultrasound instrumentation used to be very bulky and large to provide appreciable signal measurements. For example, the conventional high power amplifier in ultrasound system uses transformer as voltage step-up and impedance matching element for excitation of the ultrasound transducer [11]. The large truns of coil in the transformer eventually leaves the ultrasound system with the large power amplifier box. Although the principle of ultrasound system being very simple, the diversity in its field of applications demands for more stringent electronics, transducer and associate signal processing. As for instance, the ultrasound system while using different imaging modes often requires multiple channels e.g approximately 100 to 200 channels for two dimensional imaging, above 300 channels for three dimensional scanning. Thus miniaturization is prime essence here to make the ultrasound system portable, less expensive and overall flexiblity in operation.

Regarding the above facts, development of ultrasonic electronics spurred along with development of Integrated Circuit (IC) and holds challenges for its upgrading and optimization. Dedicated IC electronics for ultrasound instrumentation electronics have been developed by established manufactures like Analog Devices, National Instruments, Maxim, Texas Instruments. Moreover, micro-processor control based instrumentation is much favored in present context as they enhances functionality, multiple channel signal transmission and processing, flexibility of instrumentation, portability and provides ease in user interface. The ease in development time, cost reduction and design optimization is also accountable here. Such instrumentation exploits digital hardware designing with logic synthesis using Hardware Description Language (HDL) like VHDL and Verilog which allows for the realization of a programmable hardware design. This technique greatly helps in optimization of the design, minimization of cost and development time with less alteration in circuit's hardware. The digital designing of the circuit provides the design much more robust configuration as mounting and soldering of the discrete hardware components to complete the design is greatly reduced. The common hardware bug in the design of analog circuit like a false open circuit or short circuit, poor solder connection are eliminated. Thus for the compactness, robustness and overall celerity provided by such programmable hardware, miniaturization of the electronics here is ultimate.

Today more convenient implementation of the digital integrated electronics using HDL programming are carried out on Programmable Gate Array (PLA)s or Programmable Logic Device (PLD)s comparing to the Appplication Specific Integrated Circuit (ASIC) design which take much more development time and expense with very less flexibility for design alteration. The short description of the two established PLDs are described here as follow:

#### CPLD

The CPLD single chip consist of several programmable logic devices (PLD) which can be programmed. The switch matrices are provided to make connection among the PLDs. It supports interfacing to diverse logic levels as for example 2.5V, 5V, 18V in the XC9572XL-5VQ44 (IC CPLD 72MC 5NS 44VQFP, Xilinx Inc., San Jose, CA, USA) CPLD and allows Joint Test Action Group (JTAG) interface. Examples of some of the leading manufacturers of the CPLD chips are Xilinx, Lattice, Altera [12]. The main strength of CPLD lies in the procession of inbuilt Read Only Memory (ROM) which makes the HDL design configured in it non-volatile. The fast and reliable clock distribution and standard JTAG interface feature allows programming, erasing and verification of the design for high performance application anywhere anytime. On the other hand, space consumption is considerable due to inbuilt memory in semiconductor logic in CPLD, so there is limitation in the number of available flip-flops and the input-output pins that it can offer for the design configuration.

#### File Programmable Gate Array (FPGA)

FPGA were introduced in the mid 1980's by Xilinx. It allows to customize design architecture which can be modified whenever as being named field programmable. The dissimilarities of FPGA with the CPLDs lies in the storage technology, architecture, the built in features and cost. The FPGA are composed of numbers of Configurable Logic Blocks (CLB) surrounded by array of input-output blocks. It is inherently volatile due to the absence of inbuilt memory but provides advantage in wide variety of off chip storage. As for instance Static Random Access Memory (SRAM)memory based are provided from manufactures like Xilinx and Altera, anti-fuse memory based form Actel and Quick Logic are also available. Its operation is normally based on the Look Up Tables (LUT)s where the designs are implemented [12].

Hence, the above mentioned features of CPLD and FPGA makes them both a possible digital hardware for ultrasound instrumentation. An example of a HDL use in programming these PLDs is described in the following topic.

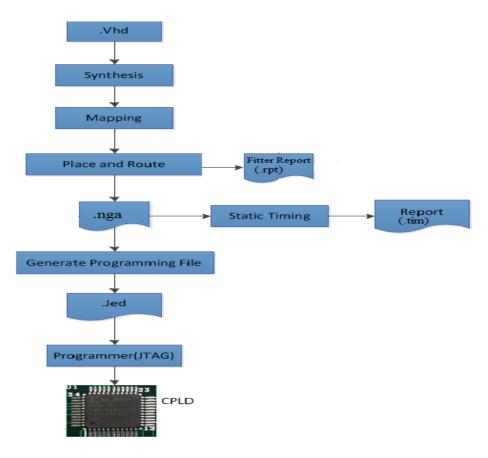

#### 1.4 Hardware Description Language VHDL

VHDL is a hardware description language use to describe the digital electronic system. Its origin came from the Very High Speed Integrated Circuits (VHSIC) program and was subsequently developed as a standard language under Institute of Electrical and Electronic Engineers (IEEE) [13]. First, it allows the description of the system structure by fragmentation and their interconnection. Secondly, means for the specification of the system's function with familiar programming language is provided. Thirdly, it allows the simulation of the design of the system before fabrication process which gives option for alternatives comparison and test for the correctness without expense of hardware prototyping and time. Lastly, the synthesis of the detailed structure of the design is allowed reducing the development time and providing strategic design decision. The Figure 21 gives the understanding of the design flow in the VHDL language. Unlike the high level programming languages like as C (ANSI C, Dennis Ritchie & Bell Labs), C++ (ANSI C) which are sequential, the VHDL code are inherently concurrent i.e execution is parallel. The concurrent feature of the VHDL programm provides an advantage for parallel processing of the digital design implemented in the corresponding PLDs. This ultimately leads to faster signal processing in application where speed is the prime specification of the design.

#### **1.5** Function Generator

The basic function of the function generator in the ultrasound system is to transmit the desired signal functions of various frequencies chosen according to the specific requirements of the ultrasound investigation undertaken. The signal generated are ultimately used in the excitation of the ultrasonic transducer. Two methods are commonly used in signal generation in ultrasound application; spike and burst. Generally the spike signal is the single delta pulse while the burst signal can be of few cycles of sine wave or three level bipolar pulse. The three level bipolar pulse are more common practice in the ultrasound system. There are different types of standard function generator used in the ultrasound transmitter system available from various manufactures. Figure 2 shows the block diagram of some function generators.

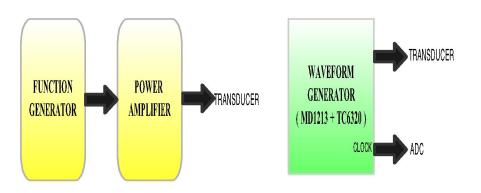

Table 1 list some features of conventional analog function generators e.g. 5800PR (Olympus corp., Shinjuku, Tokyo, Japan) along with the digital pulser demo-board MD1210+TC6320 (Supertex Inc., Bordeaux Drive Sunnyvale, CA, USA) which has been used as the replacement for the function generator in this design.

Figure 2: Block diagram of conventional analog function generator (left) and the digital waveform generator (right).

| PULSER(Transmit-Recive) | Pulse Type                        | Available<br>Voltage (No<br>load) | Weight                  |

|-------------------------|-----------------------------------|-----------------------------------|-------------------------|

| 5800PR [14]             | Negative Impulse                  | 300V                              | 6 kg                    |

| 5900PR [14]             | Negative Impulse                  | 220V                              | 7.27 kg                 |

| 5627Rpp-1 [14]          | Negative Impulse                  | 150V                              | 7.27 kg                 |

| MD1210+TC6320 [1]       | 3-level Pulse (Pro-<br>grammable) | Dual 100V                         | approximately<br>100 gm |

Table 1: Examples of some pulsers.

#### 1.6 Ultrasound Transducer

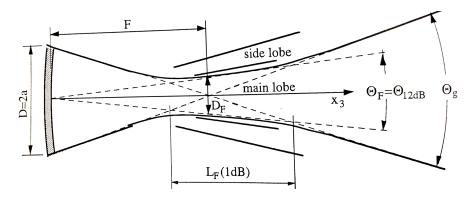

The ultrasound transducer is an active part of the ultrasound measurement system. Its principle function is the conversion of energy from electrical domain to the mechanical domain and vice-versa. There exist a variety of ultrasound transducer using various methods for mechanical and electrical coupling, for example piezoelectric transducer and capacitive transducer [15]. Their diversity also exist in the shape, aperture diameter (lable D in Figure 3) and the number of active element used i.e. single element, linear or phased array for different mechanism of beam focusing and steering [5]. The choice of specific transducer in a ultrasound investigation is often application oriented. For example medical ultrasound often uses 1D or 2D array transducer, underwater SONAR system uses array elements transducer while the fish finding mostly employs a single element transducer, NDT uses either single

Figure 3: Single element ultrasound transducers.

element or array transducer depending on the applications. Today, there exist variety of configuration on the transducer design provided by established manufacturers like Olympus, Vermon, Imasonic for ultrasound interrogation in different applications. The conventional ultrasound transducer exploits piezoelectric effects for the electro-mechanical coupling. The piezoelectric materials like Rochelle Salt, Barium Titanate and quartz are able to generate ultrasonic waves with frequencies above 1MHz [5]. Today's ultrasound transducer are made of ceramic materials e.g Lead Zirconium Titanate (PZT) which also provides good resistant to heat and radiation [9] being is beneficial in many NDTs. Figure 4 shows the basic ultrasound beam from a single element ultrasound transducer. Moreover the available apperature D of the ultrasound transducer is only a limited number of wavelengths  $\lambda$  i.e. a in Figure 4 of the corresponding ultrasound ultrasound [5].

Figure 4: Ultrasound beam focusing from spherical shell disc (D is aperture, a is wavelength of the ultrasound) [5].

Apart of the choice of crystal for ultrasound, other factor that are considered in ultrasound transducer is impedance matching for optimum power transfer during energy conversion. The impedance matching should consider the acoustic impedance mismatch between the transducer and the target and also the function generator or pulser. The acoustic impedance matching for the transducer as shown in Figure 3 is often maintain using backing and the matching layer [6]. Employing an Electrical Impedence Matching (EIM) network for Acoustic Impedence Matching (AIM) is a common practice in improving the bandwidth of the transducer in applications e.g in acoustic emission detection and in medical imaging [16]. So, a special circuit can be used for the purpose of matching the complex impedance of the transducer with the pulser circuit. Since, the modelling of the transducer as a ultrasound device refers to the RLC ultrasound circuit, a dedicated circuit for complex impedance matching of the transducer can be done by using transformer ratio along with the RLC circuit.

The appropriate choice of the ultrasound transducer is more of application oriented. To have the desired beam profile and sensitivity trade-off often come forth for bandwidth and sensitivity they can provide.

### 1 INTRODUCTION

## 2 System Description

This section mentions the motivation for the work undertaken in the background topic. The associate system in the design is elaborated under subsequent topics. Introducing the initiation of work, the short discussion of the overview of ultrasound transmitter system designed and lastly some limitations in the system design is presented here.

#### 2.1 Background

There are numerous valuable motivation for formalizing the task of designing a ultrasound transmit-receive system. This project started as upgrading the building block electronics for the air-coupled ultrasound NDT. Moreover this work was aimed to aid in possible optimization of the electronics in the ultrasound transmitter system for NDT and probably replace the large boxes like as power amplifiers and function generators used in the conventional ultrasound measurement system. Latter it evolved as a generic single channel transmit-receive electronics for ultrasound system which can aid in many ultrasound applications. For example in the Doppler velocity measurement, a general purpose laboratory kit for studying and analysing ultrasonic measurements and so on. Similar system has been used in Rikshospitalet University Hospital (Oslo, Norway) for continuous observation of cardiac function during and after cardiac surgery [17]. The dedicated analog electronics and software used in this system provided the background and motivation to start the task of designing the building blocks for ultrasound system. Here main focus has been done in providing flexibility in function generator that transmits the ultrasonic waveform such that this system can be adopted in many ultrasonic applications. Also optimizing of the transmitter for the Doppler measurement was desired as this transmitter system is intended to be included in the Doppler velocity measurement of oil or fluids in pipelines by Kongsberg Devotek As (Kongsberg, Norway). The field of application of the purposed ultrasound transmit-receive instrumentation seemed to be wide and genuine which provided a good motivation for the system designed.

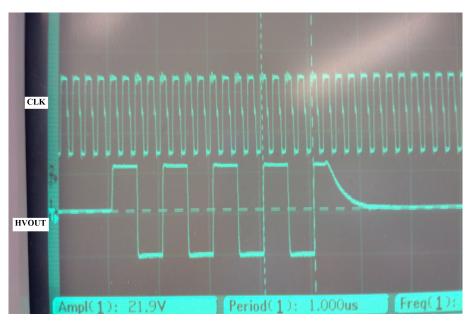

#### 2.2 System Hardware

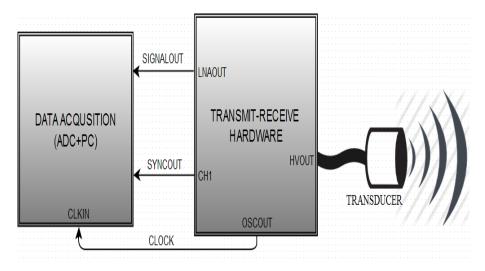

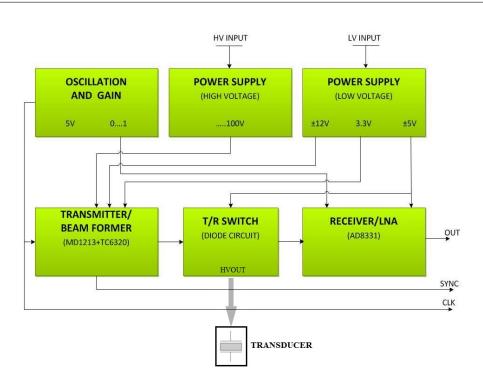

The hardware of the designed system was aimed to scale the sizes of analog power amplifier and function generators, see Figure 2, used in ultrasound measurement system down to the PCB level. Figure 5 shows the outlook of the purposed system. The transmit-receive hardware block features analog and digital hardware of the system designed which is also the main task undertaken. This block provides output signals like HVOUT a high voltage signal to drive ultrasound transducer and the CLOCK to be used as synchronous sampling signal for ADC and SYNCOUT which can be used for the trigger. This output features are valued for making accurate Doppler measurements. It provides additional flexibility and features for different ultrasound inspection processes. Figure 6 shows the detail components of the transmit-receive hardware which are discussed in the following topics.

Figure 5: The overall system block diagram.

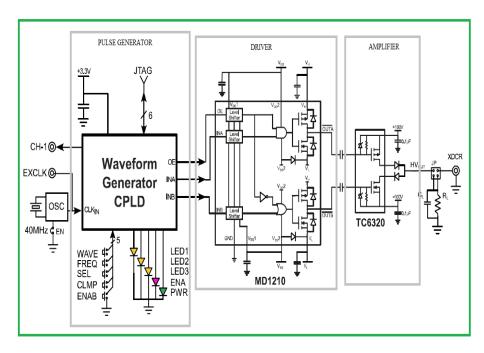

#### 2.2.1 Transmitter Board [1]

The transmitter board is a factory manufactured PCB prototyped of Supertex's MD1210DB demo board (Supertex Inc.), see Figure 7. It provides the ultrasonic pulses of desired frequencies as programmed which is used to interrogate with the target cell. Referring to the data-sheet of MD1210+TC6320 demo board, it is capable of transmitting high speed of 100 MHz, high voltage dual 100V ultrasound pulses with output current sourcing of 2A. Its PCB layout avoid any parasitic coupling from the high voltage outputs to the low voltage inputs by using solid ground plane, good signal and power routing on the board. As depicted in Figure 8, the embedded CPLD when configured with tri-state pulser firmware (see Section 3.3) along with the level translator i.e. MD1213(Supertex Inc.) high speed driver and the power Metal Oxide Semiconductor Field Effect Transistor (MOSFET) amplifier TC6320(Supertex Inc.) stands as a possible replacement for the function

Figure 6: The ultrasound transmit-receive system block diagram .

generator and the power amplifier blocks in the ultrasound system, see Figure 2.

The level translator [1] or the high speed driver MD1210DB (Supertex Inc.) circuitry provides multiple signal levels e.g logic level of range 1.8V to 3.3V for the high speed performance up-to 100 MHz and line level of optimum range dual 10V to 100V for DC coupling. Its input logic level being Complementary Metal-Oxide Semiconductor (CMOS) logic compatible i.e. 1.2V to 5V is favourable for low power and high speed logic solution. The high speed driver allows for the pulse settling time i.e. the rise and fall time down to the order of nanoseconds e.g. 6ns. Its output swing below ground level allows for transmitting the three level bipolar pulse while its logical inputs (INA and INB) can remain in ground reference. Further with all its features and appropriate a appropriate CPLD design configuration can make it an appropriate ultrasound transmit-receive instrumentation for velocity measurements.

The design specification of the output signals from the waveform generator is described as following:

- 1. The logic supply of 3.3V for the input logic.

- 2. The low voltage supply of 12V for output stage in amplifying the output

#### 2 SYSTEM DESCRIPTION

Figure 7: The MD1210DB transmitter board [1].

pulse under low voltage level.

- 3. The high voltage supply of typical 100V for output stage in amplifying the output pulse under high voltage level.

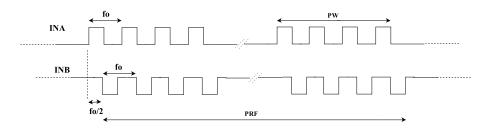

- 4. The two pulse burst output from the pulse generator (INA and INB from CPLD in Figure 8) of few cycles of the desired ultrasound frequency transmitting at a constant repetition rate and are phase inverted with each other but also with the delay of half cycle of the ultrasound frequency between them, see Figure 9.

- 5. The three level bipolar high voltage pulse burst transmitting at the constant repetition rate output (HVout in Figure 8) from the board for ultrasonic transducer excitation.

- 6. The sync output (CH1 in Figure 7) which can be used as a triggering signal while investigating input or output waveforms.

- 7. The enable signal (OE) to turn the transmitter ON and OFF with the on board switch select can be seen in same Figure 7.

Figure 8: The MD1210DB transmitter board circuit diagram [1].

8. The on board Light Emitting Diode (LED) indication to display the normal functioning of the MD1210DB board.

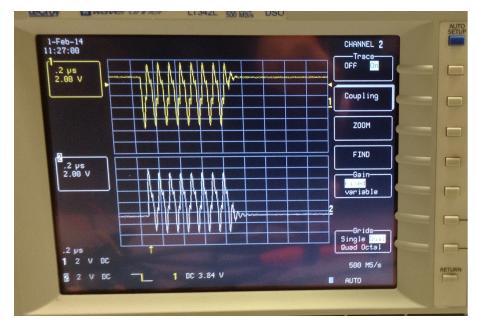

Figure 9: The outputs INA and INB from the CPLD.

The three levels of the output pulse i.e. HVout in Figure 8, from the MD1210DB board relates to the three different states of the output pulse encoded using two logic inputs (INA and INB in same Figure 8) [1]. The summary of this states is shown in Table 2 where bit values 0 and 1 has been used to refer low and high state of the logical inputs respectively.

As shown by the pulser Disable state in the Table 2, when MD1213 is disabled i.e. OE=0, the positive and negative supply voltage (Vh and Vl) sourced from the power supply board for the purpose of pulse amplification are connected to the outputs by default. This subsequently keeps the

| Lo | Logic Input |     |      | Transm | nitter Output          |

|----|-------------|-----|------|--------|------------------------|

| OE | INA         | INB | OUTA | OUTB   | STATE (3-Levels)       |

| 1  | 0           | 1   | 1    | 0      | Ground $(0V)$          |

| 1  | 1           | 1   | 0    | 0      | Positive peak $(+12V)$ |

| 1  | 0           | 0   | 1    | 1      | Negative peak (-12V)   |

| 1  | 1           | 0   | 0    | 1      | Avoided                |

| 0  | Х           | Х   | 1    | 0      | Diasable               |

Table 2: Truth table of logical states for digital pulser.

P-channel and N-channel power MOSFETs (see TC6320 in Figure 8) turn on which helps to complete the power supply path. Thus, when the level translator chip MD1213 is enabled i.e. OE=1, the logical input should never meet the state Avoided as this will turn off the P-channel and N-channel power MOSFETs leading to short circuit of the power supply which might be fatal for the MD1210DB board. The procedure undertaken for meeting these design specifications is discussed in synthesizable VHDL design part 3.3.

#### 2.2.2 Transmit-Receive Switch

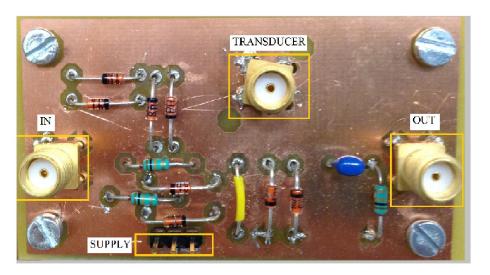

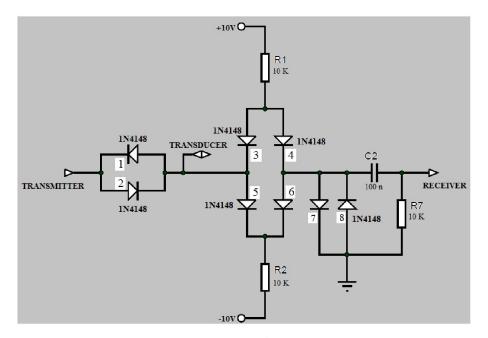

The T/R switch dedicated for ultrasound application are manufactured today by different established manufactures. As for example, the multichannel high speed T/R switch IC for embedded system LM96530 (Texas Instrument Inc., Dallas Texas, USA), MAX4936/MAX4937 (San Jose, California, USA). The model of the passive T/R switch shown in Figure 11 is referenced from the T/R switch passive circuit configuration of these IC switch. Figure 10 shows the single channel T/R switch for the ultrasound transmit-receive system designed and the corresponding circuit diagram is shown in Figure 11.

In the ultrasound transmit-receive system, it is often critical to separate the high power signals from the transmitter end from reaching the receiver circuity such that any possible damage of the receiver electronics is avoided. Since the transmitted signals are in the range of hundreds of volts while the received signal is in the rage of few milivolts. This is often achieved by introducing a transmit-receive switch between transmit and receive hardware in the system path. The T/R switch functions with integrated clamping diodes capable of protecting the receiver's Low Noise Amplifier (LNA) amplifier from high voltage pulse from the transmit channel. The single channel T/R switch, see Figure 10 receives the high voltage signal input from the pulser output (Figure 7). The series noise limiter diodes (1 and 2 in Figure 11)

Figure 10: A single channel T/R switch PCB.

Figure 11: A single channel T/R switch passive circuit.

limits noise RF input pulse and regulates the necessary signal level to drive the ultrasound transducer. The clipping diodes (see 3, 4, 5, 6, 7 and 8 in Figure 11) reduces the high voltage signal level of hundreds of volts to the low level of around 700 millivolts. Thus this passive diode switch basically uses the voltage drop over diodes to isolate the transmitter and receiver.

#### 2.2.3 Receiver

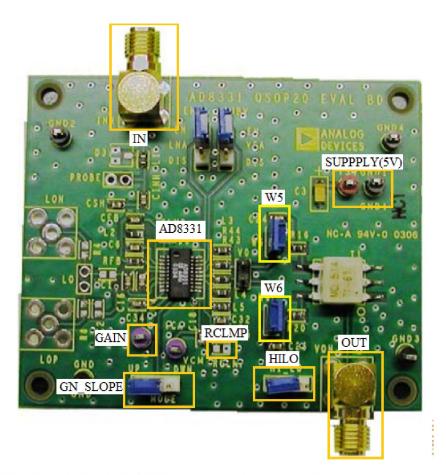

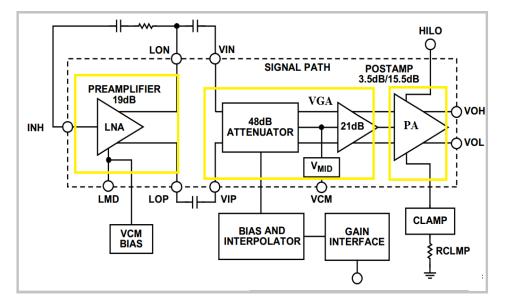

The receiver block in the ultrasound system is used to receive and amplify the back-scattered ultrasound echoes received from the transducer. It can be a single channel or multichannel depending on the number of received RF scanlines from the ultrasound transducer that it can process. Since the received RF signals from the targets are the low level signals whose strength are depth or time dependent i.e. echoes from larger depths are weak than the near ones or signals from larger depths are received latter in time than the near ones. To compensate these factors, its prime function is often to provide the low noise variable gain or time gain amplification of the received signal. Today various type of dedicated receiver for ultrasound application are provided by established manufactures e.g. Analog Device, Texas Instruments which can be readily implemented in the ultrasound measurement signal path. Figure

Figure 12: The dedicated AD8074 evaluation board for ultrasound receiver from Analog Device. [2]

12 shows the single channel ultra low noise amplifier AD8331 (Analog Device Inc., Norwood MA, USA) evaluation board which is a dedicated platform for gain control of the received signals in ultrasound and SONAR applications. The circuit diagram of AD8331, see Figure 13 comprises of a ultra low noise amplifier LNA followed by variable gain amplifier Variable Gain Amplifier (VGA) and a logic programmable amplifier (PA) at its output stage. The LNA plays critical role in minimizing the noise level and user-adjustable impedance matching at the input stage. The ultra low noise characteristic of this preamplifier helps in maintaining the good noise performance in the overall signal chain of AD8331. It provides default impedance of 50  $\Omega$  to match the impedance with function generators and network analyzers or data acquisition board [2] beneficial for maintaining low noise and better performance. Also, the option for programming the input impedance to 6 k $\Omega$ is allowed on the evaluation board. The VGA of AD8331 input is capacitive

Figure 13: The circuit diagram of AD8074 evaluation board from Analog Device. [2]

coupled to the preamplifier (LNA) output as shown in Figure 13. It serves in matching the attenuation of the input ultrasound by providing the variable gain amplification to the received signals. It provides precise interpolation with excellent linear gain and low noise to the input signal. This feature optimizes low gain error, maintains uniform bandwidth and low distortion in signal path which is essential in Timing Gain Control (TGC) of ultrasound measurement system. It features linear -3 db bandwidth of 120 MHz which is ideal for general ultrasound measurement purpose. The analog gain control

voltage (Vgain) controls the gain of VGA which can range from 40 mV to 1V. The Vgain input should be maintain between the range 0.1V to 0.95V for minimum error in gain. This feature is meet by the designed oscillator and gain board, see Figure 14 which can supply the gain voltage between 0V and 1V. The option for up (high) and down (low) slope of the VGA gain is provided by GN\_SLOPE pin on the evaluation board, see Figure 12 which provides negative or positive slope of the gain respectively. The negative gain slope i.e up is favourable for the TGC in ultrasound measurement.

The final output stage of AD8331 i.e. the logic programmable amplifier performs post amplification function. It allows the selection of output noise floor and adjustment of the gain range with the HILO logic pin, see Figure 13. The LO and HI modes option allows for optimization of high speed ADC drive. The HI mode can be suitable in driving ADC with higher noise floor while the LO mode is suitable in driving ADC with lower input noise floor. It also allows the desired output signal clamping with an appropriate resistor value in the RCLMP test pin provided on the board, see Figure 12 which is useful on limiting overloading of the following ADC if necessary. All these characteristic features of the AD8331 receiver board is ideally suitable in ultrasound measurement system. Some of them e.g. HILO, Vgain was exploited in the designed.

#### 2.2.4 Oscillator and Gain Board

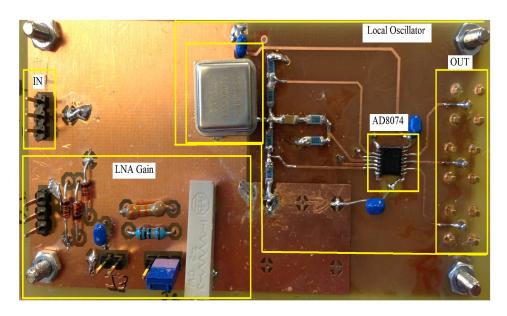

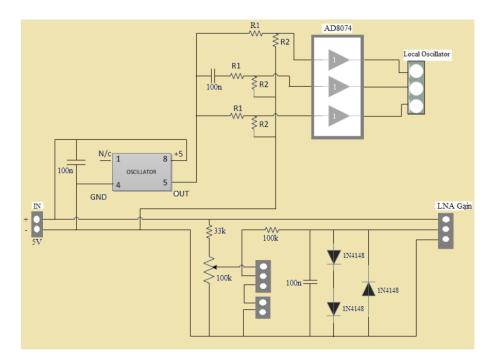

The oscillator and gain board (PCB4) is desired in the ultrasound transmitreceive system to have the local oscillation of desired frequencies for the transmitted signal and the gain control voltage for the received signal. This local oscillation can also be used to provide the synchronizing clock in sampling for further signal processing by ADC. Figure 14 shows the PCB prototype of oscillator and gain board and the corresponding circuit diagram is shown in Figure 15. The referenced circuit is shown in appendix 37 which was upgraded in the design i.e. modifying the local oscillator circuit part using AD8074 (Analog Devices Inc.).

The local oscillator circuit part provides the external input clock signal for the MD1210DB board input logic i.e. EXCLK in Figure 8 and also the reference sampling signal for data acquisition in ADC i.e. CLKIN in Figure 17. The clock signal EXCLK input for the MD1210DB board is required to have the desired ultrasound frequency in ultrasound transducer excitation and the common oscillation signal is required for sampling by the ADC as to avoid the jitter during any Doppler velocity measurements. Here, the on board crystal oscillator can be changed to have the oscillation of different frequencies as desired. The triple video buffer AD8074 used allows buffer-

Figure 14: The oscillator and gain board.

ing of the oscillator output to 50  $\Omega$  loads. The three outputs provided by the AD8074 buffer are two DC coupled and a AC coupled with 50 $\Omega$  termination, see Figure 14. The DC output can be used for the clock signal of the MD1210DB board while the AC coupled output can be used for sampling signal by ADC. AD8074 feature provides -3dB full signal bandwidth of 450MHz with output settling time of 4ns [18]. This extreme bandwidth and high slew rate is an advantage in driving the high speed input logic of the MD1210DB board and also for providing the local oscillation as a clock input for the ADC.

The LNA gain circuit, see Figure 15 provides the voltage for gain of the receiver's LNA. The gain network using a voltage divider circuit of 100 K $\Omega$  potentiometer, see Figure 14, can provide gain voltage in range of 0V to 1V in the design.

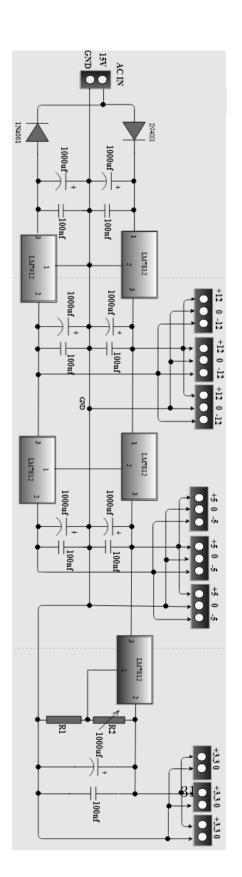

#### 2.2.5 Power Supply Board

A power supply board plays a vital role for overall system functioning and performance by supplying the necessary power. It provides the electrical energy required for normal operation of all the system components.

There exist different topologies in the design of a power supply, e.g. a linear power supply or a switch mode power supply. Most of the power supplies today are switch mode using a complex switch circuit and has better efficiency and wide range of input dynamics. But they are often very noisy

#### 2 SYSTEM DESCRIPTION

Figure 15: The oscillator and gain board circuit diagram.

due to switching topology they exploits for upgrading their efficiency. The conventional power supplies are more of linear types with simple construction i.e. using capacitors and regulators. They are less efficient than switched power but the noise level and AC ripples are considerably low. The low efficiency implies that there is a power dissipation which should be removed using heat sinks.

A linear low noise regulated power supply is favourable in the ultrasound measurement system where the input stages are sensitive to noise. It also needs to provide enough overhead for all the load constantly since any voltage drop or fluctuation will lead to an error in output voltage supplied to the system which can introduce error in the measurement undertaken. Thus a linear low noise power supply for the system designed is shown in Figure 16. The design specification for the low voltage power supply board is given in Table 3.

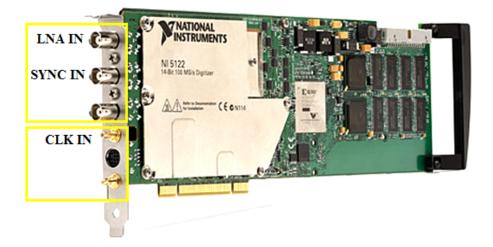

#### 2.2.6 Data Acquisition using ADC [3]

One of the primary data acquisition functions in the ultrasound measurement system is the analog to digital conversion. It is to convert the analog signal into discrete from which can be stored and represented in the digital device like a PC for instance. The digitizer NI PCI-5122 (National Instruments

| Regulated Output(DC) | Description                                     |  |

|----------------------|-------------------------------------------------|--|

| 5V dual              | Input supply for PCB2,PCB3 and PCB4 (6)         |  |

| 12V dual             | voltage amplification supply logic for PCB1 (6) |  |

| 3.3V single          | Input logic for pulse generator (CPLD 7)        |  |

Table 3: Design specifications for power supply board.

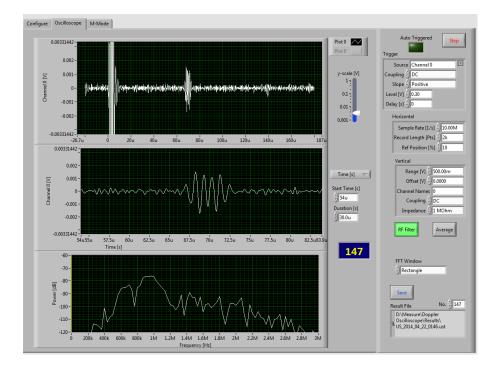

Crop., Austin, Texas, USA) used in digitizing the receiver output is shown in Figure 17. It provides simultaneous digitization of two channels at a maximum sampling rate of 100 Mega Sample per Second (MS/s). It allows high resolution with 14-bits and real-time streaming of the acquire data. It is a dedicated electronics for applications like RF data streaming. It is ideal for both time and frequency domain analysis. Its feature for multiple recording of the received samples is an advantage for any ultrasound data processing. The measurement and analysis function is provided on the software drive or can be interfaced by designing Virtual Instrument (VI) programs in software like LabView.

#### 2.3 Transducer

The ultrasound transducer performs the critical function of electromechanical coupling i.e. conversion of the transmitted high voltage PW into transmitted ultrasound pulse in the target and electrical signal conversion of the received back-scattered echoes from the target. The ultrasound measurement system exploits different types of ultrasound transducer according to the requirement of the specific application. A single element ultrasound transducer of 1 MHz ultrasound frequency, see Figure 18 (left) was used for the corresponding function. The aperture D of the transducer can vary considerably according to desired beam focusing under desired ultrasound investigation. Figure 18 shows some examples of the ultrasonic transducer which will be used along with the designed ultrasound instrumentation in making ultrasonic measurement.

#### 2.4 Software Tools In The Design

For the completion and simulation of the design involving digital and analog part of the system, some software tools were used. This are described briefly below:

#### ISE Design suite

The ISE Design suite V14.3 (Xilinx Inc., San Jose, CA, USA) provides the ground for analysis, design and synthesis of the digital part of the ultrasound transmit-receive system designed. The ISE Design Suite is the development tool from Xilinx which provides a complete front-to-back design environment along with the Register Transfer Level (RTL) to bit-stream design flow suitable in logic design. The upgraded versions available today e.g. Vivado (Xilinx Inc.) can also provide the high-level synthesis like C, C++ specifications directly into the target PLDs without requiring to manually program the RTL as in the HDL program. It is an industry-proven solution for Xilinx all programmable devices. So it was used as the tool for design and implementation of the ultrasound transmitter configuration in XC9572XL-5VQ44(Xilinx Inc.). As the implementation tools for the specified PLD, it is driven by the corresponding timing requirements. The tool assign design constraints e.g. registers, flip-flops, input-output ports for the design. It exerts the appropriate amount of the of effort required to ensure the fulfilment of the timing requirements e.g. the propagation delays in the target PLD, signal slack time constraint. However over constraining of the timing requirements e.g. negative slack in signal path. The routing and mapping of the signals should be correctly by providing a proper user constraint file (.ucf) in the design tool. By properly constraining the target PLD resources the programmed hardware description language e.g. VHDL, Verilog is implemented in the target PLD without ambiguity. Moreover when the timing requirements are over-constraints, the effort to meet this requirements are also significantly increased leading to increased memory use, tool run-time. It can also result in degradation in the performance of the particular requirement as well as other requirements applied to the design. So all the requirements including the timing constraint e.g. signal propagation delay, signal slack should be proper applied according to the specifications provided by the corresponding PLD.

In the firmware design of a single channel PW ultrasound transmitter design, the resources of XC9572XL-5VQ44 was successfully constraint by providing the proper net-list of the user constraint file i.e. the .ucf file and speed grade i.e. -5 in ISE Design tool. The use of ISE tool for VHDL programming to configure the specified firmware is more detailed in the experiment section.

#### **Proteus Professional**

The analysis for the functionality and prototyping the layout for fabrication of the analog electronic circuits of the ultrasound transmit-receive system was desired to complete the design. The Protetus Professional V8 (Labcenter Electronics Ltd., Grassington, North Yorkshire, England) software was used in hardware prototyping and simulation of the analog electronics part of the transmit-received ultrasound system designed. It is an Electronic Design and Automation (EDA) tool from Labcenter that allows for design and simulation of the hardware/software in embedded system [19]. It consist of many service modules which offers different functionality e.g schematic capture, PCB layout. The ISIS schematic capture module allows for interactive circuit simulation of the design which can be exported for PCB production with Advance Routing and Editing Software (ARES) or other PCB layout software. ARES as PCB layout module of the Proteus Design Suite which allows a complete netlist based PCB design.

#### Laboratory Virtual Instrument Engineeering Workbench (LabVIEW)

LabView (National Instruments Crop.) software was used as an optional interface in the PC for the observation of the received ultrasound signal investigation in the designed system. It also allows for further signal processing of the digitized RF signals from the ADC. It provides an option to adopt the designed system for different ultrasound measurements modes e.g. M-Mode, Doppler Mode. As a signal processing tool, it aids in manipulation of digital signal by setting up the corresponding Data Acquisition (DAQ) assistant software to configure the voltage channel from the DAQ e.g. ADC to the PC. Thus the motive here is to provide more flexibility in signal processing at the output stage.

LabView is a visual programming language platform and development environment provided by National Instruments. It is graphically-based programming language which provides an ideal workbench for test and measurement, instrumentation, automation and control system, data acquisition and data analysis applications [20]. The programs in LabView are called Virtual Instruments (VI) since it provides graphical interface for its comprehensive set of tools e.g. oscilloscope, multimeters. It can simulate hardware devices and also provides different built-in-libraries for advance analysis and data visualization by creating the VI programs.

#### 2.5 Limitations of Designed System

The ultrasound transmit-receive electronics designed was a mixed system type i.e. including both analog and digital system. The main focus was to upgrade the system for adopting in different ultrasound applications and miniaturization for its portability. Regarding these goals, the comprehension of a complex system entirely in digital hardware is physically not possible with the technology available today. Thus trade-offs between hardware and software are often unavoidable in mixed system design. The major limitation is often encounter due to the sample rates in the digital system comparing to the analog counterpart. The hardware/software trade-off for cost and performance, power and efficiency is encounter in the design. As for instance, the conventional analog function generator are more robust, simple to operate and cheaper but lacks in efficiency, flexibility and portability. Likewise its possible digital e.g. MD1210DB board counterpart provides flexible user interface, efficiency and portability but holds challenge for arbitrary functions and are costly, see Figure 2 in section 1.5. The analog function generator used in excitation of the ultrasonic transducer, see Figure 6 allows the use of low supply voltage, inexpensive low voltage MOSFETs for switched mode amplification. On the other hand, it can provide significant SNR as being able to produces high level signals e.g. 400V peak-to-peak signal [11]. This optimistically leads for robust configuration to the system block and availability of higher signal level at the output for ultrasonic transducer excitation. On the pessimistic side, it makes the system block huge and bulky creating inconvenience in the overall system portability. It can also basically generates any arbitrary functions i.e. signal of any desired functions but the control of the transmitted signal's phase, length is often challenging. Also the operation bandwidth is often limited for low frequency ultrasonic application (100KHz to 2 MHz [11]) which is not always desirable.

Comparing to these facts, implementing the digital board e.g. Figure 7 allows for miniaturization, system block portability, wider frequency bandwidth for operation and more programmable control of the transmitted waveforms. There is also possibility for providing additional features for further signal processing in digital system e.g. providing the synchronizing sampling clock for Doppler velocity measurement. The shape or function e.g. sinusoidal and strength of the output signal provided for ultrasonic transducer excitation is limited to the pulse shape. However the three level bipolar waveforms are common and acceptable for most of the ultrasonic interrogation. So designing the waveform generator for the ultrasound transmitter seems to be a better approach although some trade-offs are accountable.

Figure 17: The 14-bit 100 MS/s digitizer from National Instruments (NI PCI-5122).[3]

Figure 18: Single element ultrasound transducers.

# 3 Experiment Method

This section elaborates the practical measures undertaken to design the ultrasound transmitter system. The means for software and hardware that has been exploited for the work is explained briefly. The synthesizable VHDL (IEEE Standard) design for the ultrasound transmitter is discussed here. The design flow procedure undertaken in ISE tool for the design implementation in corresponding hardware is illustrated. Also the methods involved in hardware prototyping of different blocks of electronics surrounding the design is discussed in short.

# 3.1 Experiment Setup

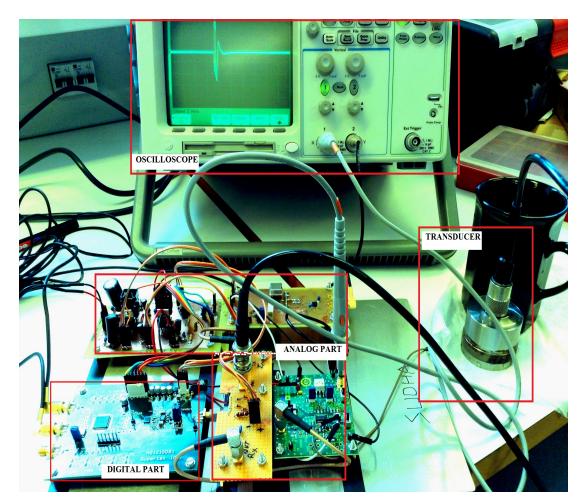

Figure 19: The Ultrasound Test Setup with the designed system.

#### **3** EXPERIMENT METHOD

The ultrasound test setup in laboratory is depicted in Figure 19. The transducer i.e. the single element 1MHz to make ultrasound tests, the oscilloscope Lecroy LT342L (Teledyne LeCroy, Chestnut Ridge, New York, USA) and the water beaker to investigate the ultrasound measurement with the designed system are also included here. The output waveforms on the oscilloscope provides real time observation of the waveforms so that their characteristics can be properly analyzed. The objective of ultrasound trans-

Figure 20: The output waveform of the transmitter.

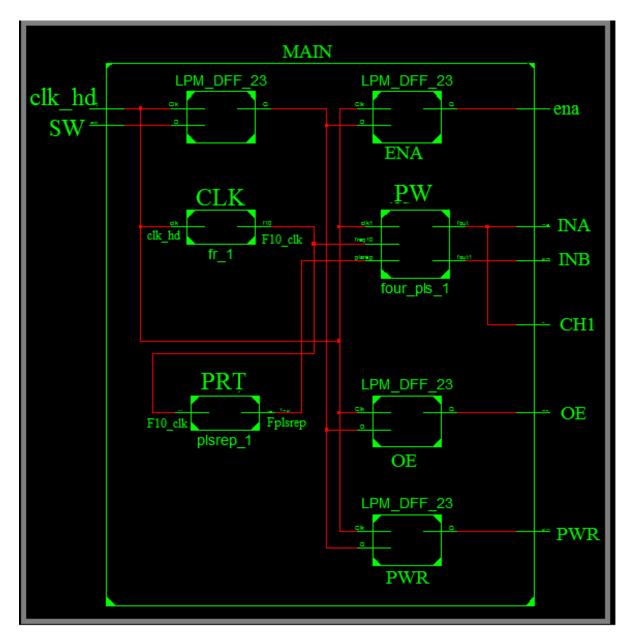

mitter system design was undertaken in two parts; the digital design of the MD1210DB transmitter board and the analog design for electronics surrounding the ultrasound transmit-receive system. In the digital part, CPLD chip XC9572XL-5VQ44 embedded on the MD1210DB board, see Figure 7 was configured by using VHDL program to generate three level ultrasound pulses as shown in Figure 20. This served the purpose of the waveform generator for generating PW of desired ultrasound fo with the repetition frequency of PRF in the design. The analog design part includes the design, analysis, simulation or fabrication of the rest of the PCB blocks i.e. the power supply, the T/R switch, the oscillator and receiver gain shown in Figure 6). The receiver block in the same figure was attained by ultra-low noise preamplifier AD8331-EVALZ (Analog Device Inc.), as seen in Figure 12 whose functionality was analysed and implemented according to our system requirement.

#### 3.2 Using ISE Tool

For the firmware design of the waveform generator, an EDA tool was essential in the design. As mentioned above in section 2.4, the implementation of the function generator, see PCB1 in Figure 6 was done by configuring the CPLD chip XC9572XL-5VQ44 embedded in the Supertex evaluation board MD1210DB. The VHDL programming file for the design was created using the ISE design suit V14.3 (Xillinx Inc.). The design flow of the ISE design tool for the design synthesis and simulation is depicted in Figure 21 which was adopted from [13].

In ISE design suite, initially the design properties for the target chip e.g device name, speed grade, HDL language being used was input in the target chip properties as shown in Figure 22. The CPLD speed grade as given as -5 was chosen to be the correct value for accurate delay in timing simulation and the design synthesis, see figure 22.

Figure 21: The VHDL design flow in ISE design suite.

As shown in Figure 21, first the VHDL code was written on the target CPLD to generate three level ultrasound pulses, see Figure 20 according to the design specifications of the MD1210DB board mentioned in section 2.2.1. Then the behaviour simulation was performed as the test bench to check for the proper performance of the design within the design specification. Some of the behavioural simulation results is depicted in the result section, see Figure 30. The synthesizable VHDL code was programmed in order to implement the design in the targeted device which is discussed in the following and the corresponding source code is attached in the appendix 6. This VHDL program in appendix (6) was interfaced on the CPLD by

#### 3 EXPERIMENT METHOD

| Name: r                              | nytx                   |  |  |

|--------------------------------------|------------------------|--|--|

| ocation:                             | C:\Xilinx\project\mytx |  |  |

|                                      | C:\Xilinx\project\mytx |  |  |

|                                      | Itrasound Transmitter  |  |  |

| Description:                         |                        |  |  |

| Project Settings                     |                        |  |  |

| Property Name                        | Value                  |  |  |

| Top-Level Source Type                | HDL                    |  |  |

|                                      |                        |  |  |

| Evaluation Development Board         | None Specified 🗨       |  |  |

| Product Category                     | All                    |  |  |

| Family                               | XC9500XL CPLDs         |  |  |

| Device                               | XC9572XL               |  |  |

| Package                              | VQ44                   |  |  |

| Speed                                | -5                     |  |  |

| Synthesis Tool                       | XST (VHDL/Verilog)     |  |  |

| Simulator                            | ISim (VHDL/Verilog)    |  |  |

| Preferred Language                   | VHDL                   |  |  |

| Property Specification in Project Fi |                        |  |  |

| Manual Compile Order                 |                        |  |  |

| VHDL Source Analysis Standard        | VHDL-93                |  |  |

|                                      |                        |  |  |

| Enable Message Filtering             |                        |  |  |

|                                      |                        |  |  |

Figure 22: The design properties configuration of the CPLD chip in ISE design suite.

JTAG(IEEE 1532 standard for In-System-Programming (ISP)) interfacing provided in ISE design suite. The procedure of the design implementation in brief is as follows:

- 1. Open ISE design suite impact to configure target device.

- 2. Run impact.

- 3. Do boundary scan.

- 4. Initialize chain.

- 5. Program the target by programming with Joint Electron Device Engineering Council (JEDEC) (.JED) file (Global Standards for the Microelectronics Industry) created by the ISE design suite compiler.

The output waveforms INA and INB from the CPLD with the synthesized VHDL program was viewed in the oscilloscope first, see Figure 32. Finally, the high voltage output stage MD1213 (Xilinx Inc.) as the modification to the MD1210DB board and TC6320 IC were mounted on the MD1210DB board, see Figure 7 to complete the transmitter.

| Performance Summary                  |                           |                            |            |                             |  |  |  |

|--------------------------------------|---------------------------|----------------------------|------------|-----------------------------|--|--|--|

| Min. Clock Period                    |                           | 10.000 ns.<br>100.000 MHz. |            |                             |  |  |  |

| Max. Clock Frequ                     | ency <u>(fSYSTEM)</u>     |                            |            |                             |  |  |  |

| Limited by Clock Pulse Width for w.Q |                           |                            |            |                             |  |  |  |

| Clock to Setup (tCYC)                |                           |                            | 6.600 ns.  |                             |  |  |  |

| Pad to Pad Delay                     | ( <u>tPD)</u>             | 5.700 ns.<br>6.900 ns.     |            |                             |  |  |  |

| Clock Pad to Outp                    | ut Pad Delay <u>(tCO)</u> |                            |            |                             |  |  |  |

|                                      |                           | RESOURCES SUMMARY          |            |                             |  |  |  |