Home Search Collections Journals About Contact us My IOPscience

Graphene synthesized on porous silicon for active electrode material of supercapacitors

This content has been downloaded from IOPscience. Please scroll down to see the full text.

2016 J. Phys.: Conf. Ser. 773 012057

(http://iopscience.iop.org/1742-6596/773/1/012057)

View the table of contents for this issue, or go to the journal homepage for more

Download details:

IP Address: 158.36.231.66 This content was downloaded on 18/08/2017 at 07:24

Please note that terms and conditions apply.

You may also be interested in:

Radiative Properties of Semiconductors: Graphene N M Ravindra, S R Marthi and A Bañobre

Characteristic of Thermally Reduced Graphene Oxide as Supercapacitors Electrode Materials Vika Marcelina, Norman Syakir, Santhy Wyantuti et al.

Electron transport in graphene S V Morozov, K S Novoselov and A K Geim

Optimization of Immobilization of Nanodiamonds on Graphene A Pille, S Lange, K Utt et al.

Graphene quantum dots-carbon nanotube hybrid arrays for supercapacitors Yue Hu, Yang Zhao, Gewu Lu et al.

Doping graphene with a monovacancy: bonding and magnetism M Yu Arsent'ev, A V Prikhodko, A V Shmigel et al.

Fabrication and characterization of reduced graphene oxide modified nickel hydroxide electrode for energy storage applications Mohammad Faruk Hossain, Junli Yin and Jae-Yeong Park

About a permeability of graphene pores Mikhail A Bubenchikov, Alexander I Potekaev, Alexey M Bubenchikov et al.

Bubbles in graphene - a computational study Mikkel Settnes, Stephen R Power, Jun Lin et al.

# Graphene synthesized on porous silicon for active electrode material of supercapacitors

# **B B Su, X Y Chen and E Halvorsen**

Department of Micro- and Nanosystem Technology, University College of Southeast Norway, Campus Vestfold, Raveien 215, 3184 Borre, Norway E-mail: Xuyuan.Chen@hbv.no

Abstract

We present graphene synthesized by chemical vapour deposition under atmospheric pressure on both porous nanostructures and flat wafers as electrode scaffolds for supercapacitors. A 3nm thin gold layer was deposited on samples of both porous and flat silicon for exploring the catalytic influence during graphene synthesis. Micro-four-point probe resistivity measurements revealed that the resistivity of porous silicon samples was nearly 53 times smaller than of the flat silicon ones when all the samples were covered by a thin gold layer after the graphene growth. From cyclic voltammetry, the average specific capacitance of porous silicon coated with gold was estimated to  $267 \mu F/cm^2$  while that without catalyst layer was  $145 \mu F/cm^2$ . We demonstrated that porous silicon based on nanorods can play an important role in graphene synthesis and enable

### **1. Introduction**

Supercapacitors have attracted great interest for their high power density compared to batteries and high energy density compared to traditional capacitors [1-2]. Generally supercapacitors have an energy density 10 to 100 times larger than electrolytic capacitors, and less charging time than batteries, as well as longer charge- and discharge-cycle life [3-4]. Therefore, supercapacitors are broadly used in computer systems, grid power buffers, street lights, automobiles, and other power supply systems. Graphene is very popular for building carbon-based supercapacitors. It is an atomically thin two-dimensional sheet of sp2 bonded carbon atoms which gives rise to exceptional electronic, magnetic, and optical properties. Each atom has four bonds, one  $\sigma$  bond with each of its three neighbours and one  $\pi$ -bond that is oriented out of plane [5]. Chemical vapour deposition (CVD) has been extensively explored to grow high quality graphene layers of large area and allows growth of single or multiple layers of graphene directly on a substrate (usually metal) using hydrocarbon precursors. However, the graphene layer must usually be transferred to other preferred substrates for subsequent use and is easy to damage during the segregation from the growth substrate. Recently it has been reported that graphene can be grown on silicon templates thus transforming the substrates into stable electrodes for electrochemical devices while avoiding the exfoliation from the templates [6]. A major restriction of direct graphene growth on silicon-based

silicon as promising electrodes for supercapacitors.

Content from this work may be used under the terms of the Creative Commons Attribution 3.0 licence. Any further distribution (cc) of this work must maintain attribution to the author(s) and the title of the work, journal citation and DOI. Published under licence by IOP Publishing Ltd 1

substrates is that the pristine silicon is chemically inert due to the weak reaction between silicon and hydrocarbons. Hence application of surface engineering techniques for the CVD growth of graphene becomes an enabling process when silicon is used as a substrate.

## 2. Process for graphene growth

In this work, we propose to synthesize graphene on porous silicon through a CVD process with a catalysis mechanism. We apply a layer of gold as the catalyst. Gold has a high melting point of 1337.33K and a relatively low thermal expansion coefficient of 13. Therefore it can stay solid during the CVD process and introduce ignorable thermal stress within the graphene layer. In addition, gold doesn't react with oxygen so there is no worry about oxidation inside the reaction chamber even if the process gas is not entirely oxygen-free [7]. Yet a thick layer of metal catalyst will compromise the main advantage of a high surface area of porous silicon by filling voids and thereby reducing area. In our case, a gold layer catalyst thickness of 3 nm was chosen based on the dimension of the nanostructures. The layer was deposited with an AJA sputtering system.

Subsequently the samples were loaded into a CVD system and placed at the center of the tube furnace. The system provided an inert environment under temperatures ranging from 35°C to 850°C. Argon and Hydrogen were mixed and introduced in the tube to maintain atmospheric pressure with a flow rate of 1 SLM and 100 SCCM respectively. Then 10 SCCM of acetylene was added after reaching 650°C. The furnace was then heated to 750°C and 850°C internally with a holding time of 15 minutes in both temperature stages. Then acetylene was shut off and the samples were cooled off to room temperature in the presence of Argon and Hydrogen.

# 3. Results and discussion

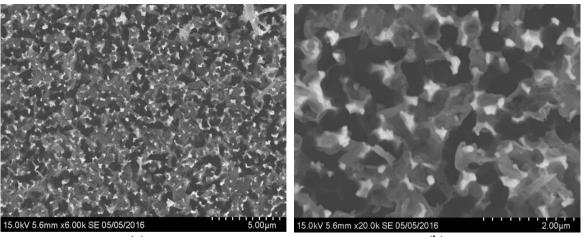

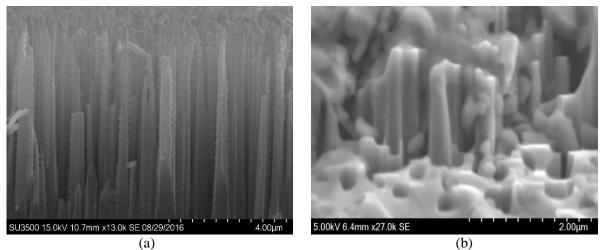

Scanning electron microscopy (SEM) was carried out using Scanning Electron Microscope SU3500 with an acceleration voltage of 5 to 15kV to identify graphene layers on porous silicon. The SEM images show the nanoscale features on porous silicon. It is clearly illustrated in figure 1(a) and figure 1(b) that there is a thin layer (bright field) on the nanorods (grey field) on porous silicon after graphene growth process. More clearly, the cross-sectional images of porous silicon of figure 2(a) and figure 2(b) show obvious difference before and after direct-graphene coated process and indicate a continuous layer covered on the nanorods although it was not as smooth as might have been expected.

(a)

(b)

Figure 1 SEM images of porous silicon showing the graphene layer coated on the nanorods, (a) in a small magnification; (b) in a large magnification.

Figure 2 SEM images of (a) cross-section of porous silicon before direct-graphene coated process, (b) cross-section of porous silicon after direct-graphene coated process indicating layers coated between the nanorods.

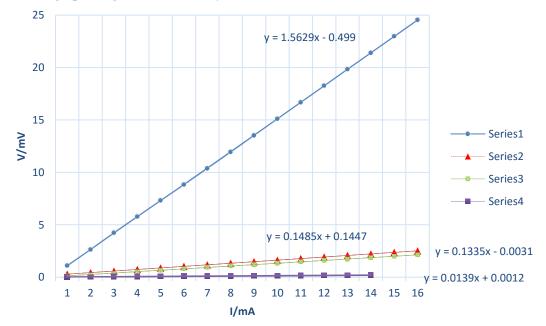

Four-point-probe measurements were conducted to provide qualitative analysis on the conductivity of direct-graphene coated and catalyst-graphene coated flat silicon and porous silicon respectively. Measurements of the resistance of the prepared samples were performed in a collinear configuration. The ratio of voltage and current, the slope in the figure 3, presents the resistance of the tested samples. Among the P-doped flat silicon substrates, the resistance is almost  $0.15\Omega$  after catalyst-graphene coating and  $1.56\Omega$  after direct-graphene coating. The results are consistent with the expectation that pure silicon is not a good substrate for graphene growth due to the low carbon solubility in silicon while the gold is a good substrate due to the adsorption of C atoms on its surface. This adsorbing behaviour further accelerates the graphene growth when acetylene was introduced [8].

Figure 3 Four-point-measurement results for tested samples of direct-graphene coated silicon (series 1), catalyst-graphene coated silicon (series 2), direct-graphene coated porous silicon (series 3) and catalyst-graphene coated porous silicon (series 4).

For the porous silicon, figure 3 shows that the direct-graphene coated porous silicon has the resistance reduced to approximately  $0.13\Omega$  compared to  $1.56\Omega$  of the direct-graphene coated flat silicon. The improvement on the conductivity largely benefited from the nanoporous structure on the surface of the porous samples. Because the nanoporous structure enlarges the surface area, carbon atoms have greater opportunity to adsorb on the surface when the reactive gases flow over the samples in the furnace. Therefore, the nanoporous structure can be seen as a pool of carbon atoms, which provided an effective path of supplying carbon source for graphene growth. In addition, for the porous silicon samples, figure 3 also shows that the catalyst-graphene coated porous silicon has resistance greatly reduced to  $0.0028\Omega$ . This significantly improved conductivity can be attributed to both the gold catalyst layer and the nanoporous structure, which allowed more C atoms to be incorporated for coating on the sample surface, thus resulting in continuous graphene film. The results reveal that porous silicon with the gold catalyst layer can be considered as an excellent functional structure base for graphene growth and can be a candidate for active electrodes of supercapacitors [9].

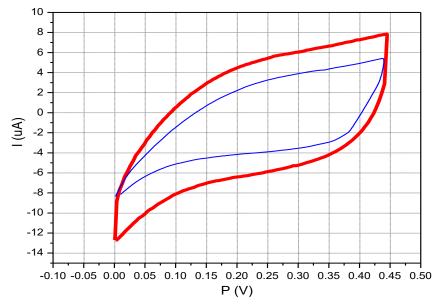

As the active electrodes for supercapacitors, the electrochemical performance, e.g., the electrochemical double layer capacitance (EDLC) of the samples was investigated by cyclic voltammetry (CV). The catalyst-graphene coated porous silicon exhibits almost double the specific capacitance of the direct-graphene coated porous silicon (figure 4). The average specific capacitance of the catalyst-graphene coated porous silicon was estimated to be  $267\mu F/cm^2$  while that of the direct-graphene coated porous silicon was estimated to be  $267\mu F/cm^2$  while that of the direct-graphene coated porous silicon was  $145\mu F/cm^2$ . Xia al. have conducted an experimental determination of EDLC capacitance of graphene to be  $21 \,\mu F/cm^2$  [10]. The results attained in this experiment indicate a substantial improvement on the electrochemical performance of both the catalyst-graphene coated and direct-graphene coated porous silicon samples, which suggests the porous silicon yields a reliable functional structure to graphene formation. An ideal CV curve of EDLC capacitor should be approximately rectangular in shape. The samples of both catalyst-graphene coated and direct-graphene coated porous silicon exhibited resistive behaviour, which makes the CV plots differ from the shape of an ideal EDLC capacitor.

Figure 4 Cyclic voltammetry plots for catalyst-graphene coated porous silicon (thicker line) and direct-graphene coated porous silicon (thinner line).

### 4. Conclusions

In summary, we have successfully managed to grow graphene on nano structured silicon samples for making active electrodes for EDLC supercapacitors. The conductivity of the direct-graphene coated porous silicon was 10 times better than that of the direct-graphene coated flat silicon, which can be explained by a high quality graphene layer because the nano structure provides large surface area, thus resulting in a large amount of carbon atoms segregating on the surface of the samples. A gold catalyst layer can further effectively promote the formation of graphene layer on the nano structure surface, which is supported by the observation of 100 times lower resistance in catalyst-graphene coated porous silicon than the one in direct-graphene coated flat silicon. Subsequently, cyclic voltammetry proved the superiority of graphene as active electrode materials for electrochemical double layer capacitors, indicating an EDL capacitance of  $145\mu F/cm^2$ .

#### Acknowledgement

Financial support from the Research Council of Norway under Grant No. 229716 is acknowledged.

#### Reference

- [1] Stoller M D, Park S J, Zhu Y W, An J H and Ruoff R S 2008 Nano Lett. 8 3498

- [2] Novoselov K S, Geim A K, Morozov S V, Jiang D, Zhang Y, Dubonos S V, Grigorieva I V and Firsov A A 2004 Science 306 666

- [3] Yoo E, Okata T, Akita T, Kohyama M, Nakamura J and Honma I 2009 Nano Lett. 9 2255

- [4] Li Y F, Zhou Z, Yu G T, Chen W and Chen Z F 2010 J. Phys. Chem. C 114 6250

- [5] Loginova E, Bartelt N C, Feibelman P J and McCarty K F 2008 New J. Phys. 10 093026

- [6] Oakes L, Westover A, Mares J W, Chatterjee S, Erwin W R, Bardhan R, 2013 Scientific Reports 3

- [7] Yazyev O Y and Katsnelson M I 2009 Phys. Rev. Lett. 100 047209

- [8] Zhang Y H, Chen Y B, Zhou K G, Liu C H, Zeng J, Zhang H L and Peng Y 2009 Nanotechnology 20 185504

- [9] Kovács Gy J, Bertóti I and Radnóczi G 2008 Thin Solid Films 516 7942

- [10] Xia J L, Chen F, Li J H, Tao N J 2009 Nanotechnology 4 101038