Faculty of Technology, Natural Sciences and Maritime Studies

Doctoral dissertation no. 84

Avisek Roy

# Local Synthesis of Carbon Nanotubes on CMOS-MEMS Microheaters for Sensing Applications

Avisek Roy

## Local Synthesis of Carbon Nanotubes on CMOS-MEMS Microheaters for Sensing Applications

A PhD dissertation in **Applied micro- and nanosystems**  © Avisek Roy, 2020

Faculty of Technology, Natural Sciences and Maritime Studies University of South-Eastern Norway Horten, 2020

### Doctoral dissertations at the University of South-Eastern Norway no. 84

ISSN: 2535-5244 (print) ISSN: 2535-5252 (online)

ISBN 978-82-7860-458-8 (print) ISBN 978-82-7860-459-5 (online)

This publication is licensed with a Creative Commons license. You may copy and redistribute the material in any medium or format. You must give appropriate credit, provide a link to the license, and indicate if changes were made. Complete license

terms at <a href="https://creativecommons.org/licenses/by-nc-sa/4.0/deed.en">https://creativecommons.org/licenses/by-nc-sa/4.0/deed.en</a>

Print: University of South-Eastern Norway

### **Preface**

This thesis is submitted in partial fulfilment of the requirements for the degree of Philosophiae Doctor (Ph.D.) from the Department of Microsystems, at the University of South-Eastern Norway (USN). This doctoral work has mainly been conducted at the Department of Microsystems (IMS), Faculty of Technology, Natural Sciences and Maritime Sciences, University of South-Eastern Norway (USN) in Borre, Norway. Experiments have also been carried out at the University of Illinois at Chicago (UIC) in Chicago, USA. The work has been done under the supervision of Professor Knut E. Aasmundtveit at USN, Associate Professor Mehdi Azadmehr at USN, and Professor Philipp D. Häfliger at University of Oslo (UiO).

The project is financially supported by the Research Council of Norway through the Norwegian Micro- and Nano-Fabrication Facility, NorFab, project number 245963/F50, and the Norwegian PhD Network on Nanotechnology for Microsystems, Nano-Network, project number 221860/F60.

### **Acknowledgements**

I am using this opportunity to express my gratitude to everyone who supported me throughout the course of my PhD research. I have thoroughly enjoyed my work in this fascinating topic. I am very grateful to my supervisors Professor Knut E. Aasmundtveit, Asc. Professor Mehdi Azadmehr and Professor Philipp D. Häfliger for guiding me throughout this journey. Your precious advice, constructive criticism and motivation have helped me to successfully achieve my goals in this project.

A special thanks to Asc. Professor Bao Q. Ta and Dr. Luca Marchetti for their support in experiments, helpful suggestions, and fruitful discussions throughout my PhD work. I would also like to thank Donatus L. Dress, Fredrik Holst and Blendian Mujaj for their support in laboratory work and for the insightful discussions we had.

For successful experimental works, support of the laboratory engineers is essential. I am thankful to Zekija Ramic, Thomas Martinsen, Dr. Muhammad Tayyib and Dr. Thai Anh Tuan Nguyen for providing that support on different stages of the research. I am also thankful to Asc. Professor Igor Paprotny, John Sabino and Tejumade Durowade for their support during my research visit at the University of Illinois at Chicago (UIC) in USA.

I would like to thank the Norwegian research council, our Department of Microsystem, and Nano-Network for providing the financial support and necessary facilities for the research work. Thanks to the PhD coordinators, Kristin Skjold Granerød and Aina Enstad for their support with the administrative works. Also, I wish to thank the members of the thesis assessment committee for taking the time to evaluate the doctoral thesis and for providing valuable comments and recommendations to further improve it.

PhD work can be very demanding. I am grateful to have an excellent group of colleagues at USN during this time. Thank you for the technical discussions, relaxing chats and the boardgame nights! Finally, my sincere gratitude goes to my closest family and my girlfriend for their unparalleled support, patience, and encouragement throughout the time of my PhD.

### **Abstract**

Research on nanomaterials is growing rapidly due to their extraordinary properties, which can significantly differ from their bulk form. The physicochemical properties of nanoscale materials are diverse and can be engineered for utilizing them in numerous applications to advance our technology. Among the nanomaterials, carbon nanotube (CNT) is a popular candidate as a sensing material, which demonstrated promising results for potential commercial applications. A monolithic CMOS-CNT integration can provide sensing features through the CNTs on the top and read-out integrated circuits (ROICs) based on CMOS transistors in the bottom.

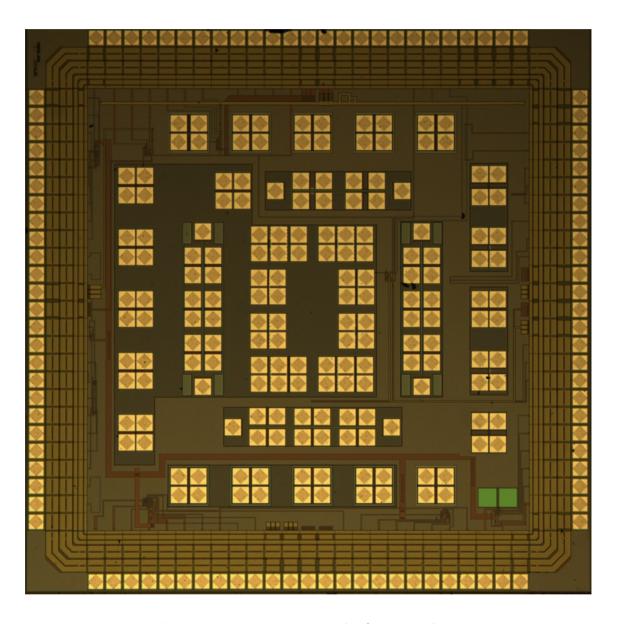

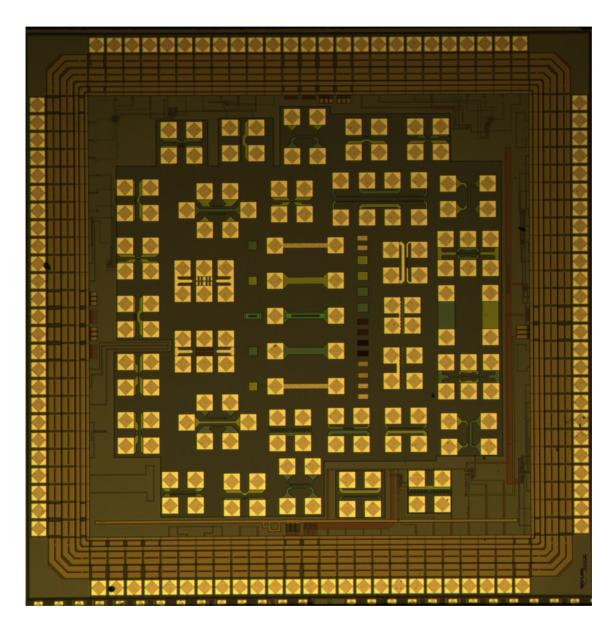

CNTs can be locally grown on custom-designed CMOS microstructures to utilize their sensing capabilities in emerging micro and nanotechnology applications. The main goal of this PhD project was to develop a CMOS-compatible CNT synthesis process on microheaters designed and fabricated in commercial CMOS chips with the vision of enabling the pathway for mass production of CNT-based sensors. Prior to designing a dedicated CMOS chip for CNT growth, thermal-mechanical simulations were performed on CMOS material layers that can generate the required CNT synthesis temperature (~650-900 °C) by joule heating. The simulated microheaters showed promising results with high thermal isolation to keep low ambient temperatures for CMOS-compatibility. Among the investigated CMOS materials, polysilicon is most suitable as heaters for high-temperature applications, while the metal options (i.e., Al, Cu) need alloying with Ni.

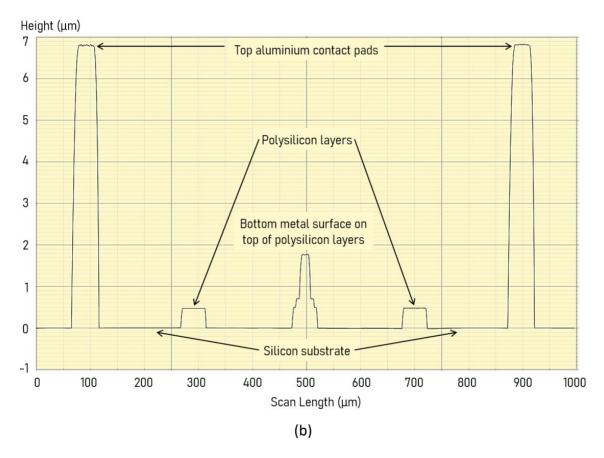

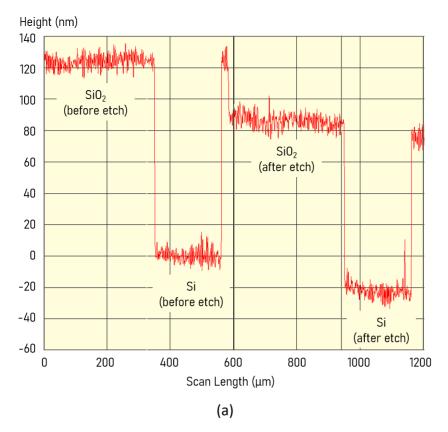

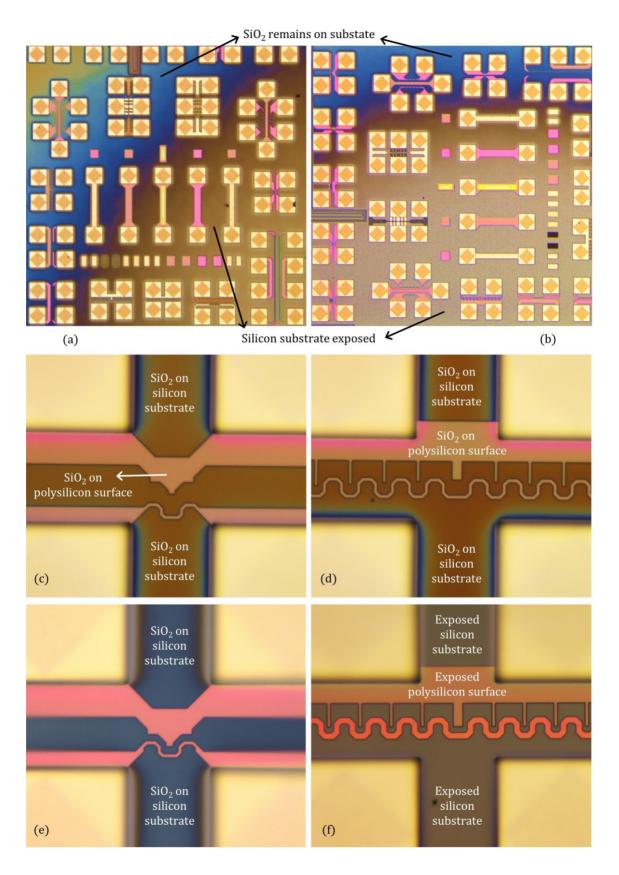

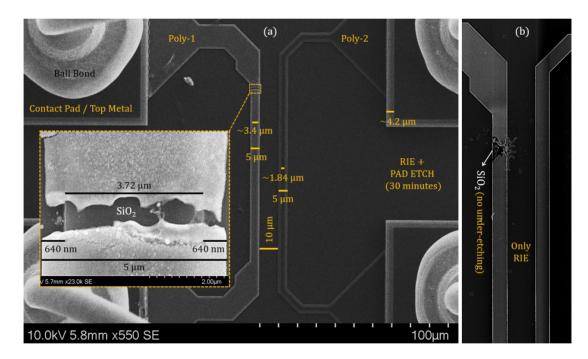

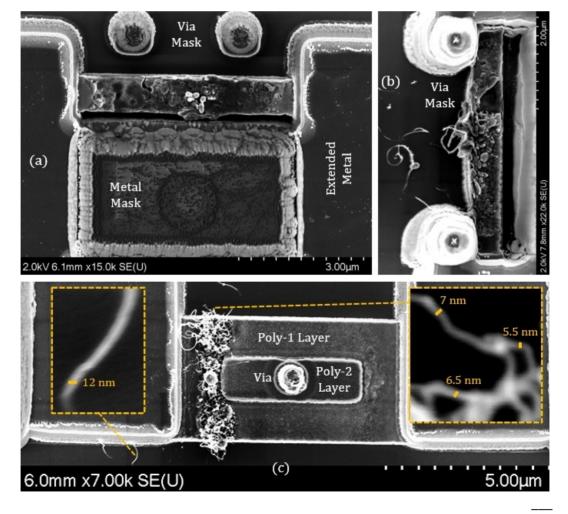

A CMOS chip with various polysilicon and aluminium microheaters was designed and fabricated in a commercial AMS 350 nm CMOS technology. Different designs also incorporate various features for realizing CMOS-MEMS heaters with varied post-processing results. A key contribution to the CMOS-CNT integration was the developed post-processing of CMOS chips for fabricating CMOS-MEMS heaters. In this post-CMOS processing, subtractive microfabrication technique was used for micromachining the heaters, where the passivation layers in CMOS were used as mask to protect the electronics. For the dielectric etching, high selectivity, uniform etching and good etch rate was required to fully expose the polysilicon layers without causing damages. It was

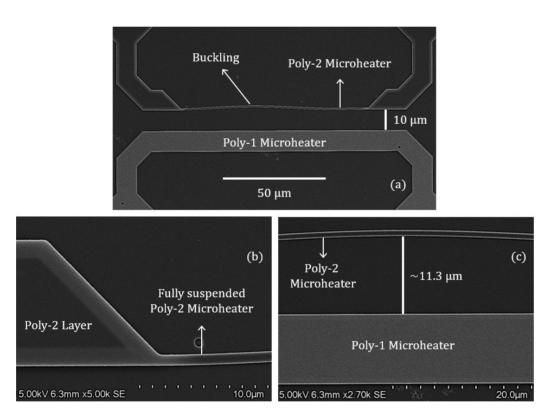

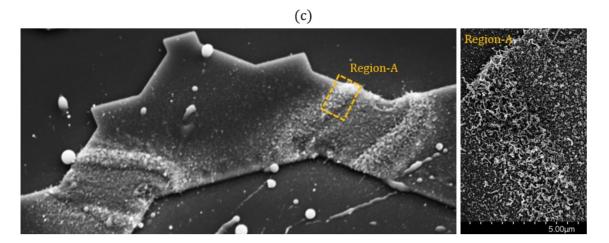

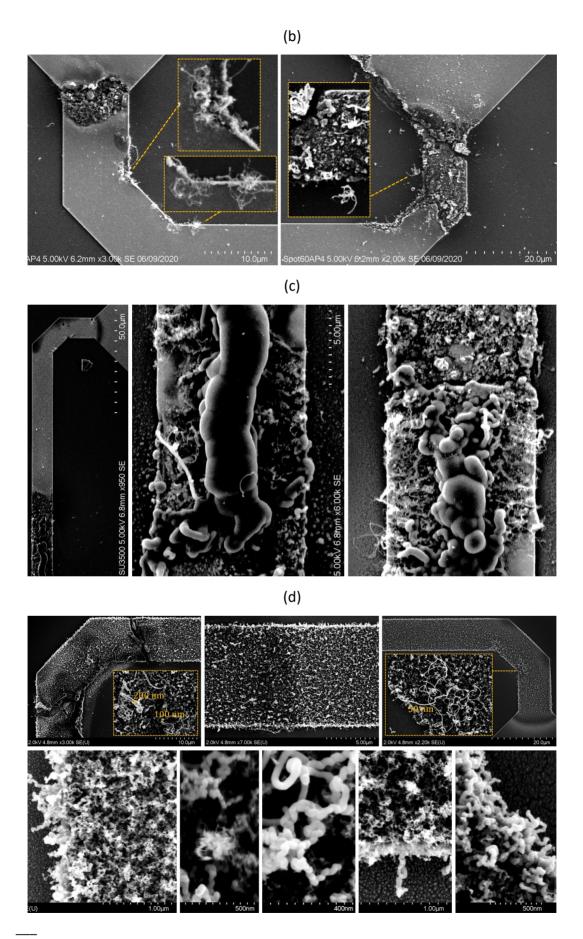

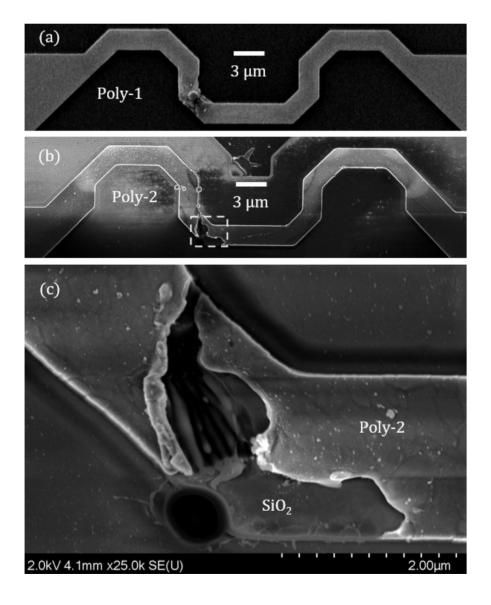

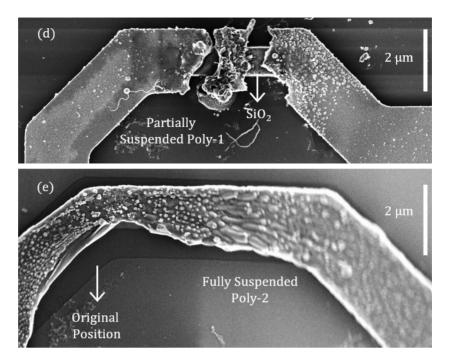

achieved by developing two-step reactive ion etching (RIE) of SiO<sub>2</sub> dielectric layer and making design improvements on a second-generation CMOS chip. Partial and fully suspended CMOS-MEMS microheaters were also fabricated by SiO<sub>2</sub> wet etching with minimum damage to the exposed aluminium layers.

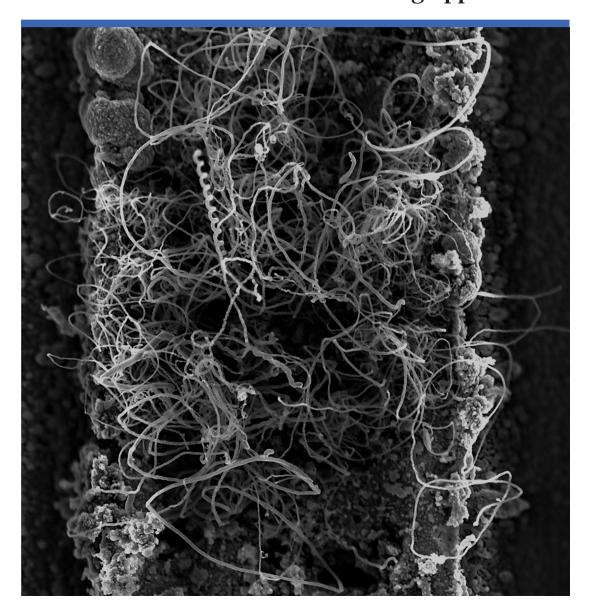

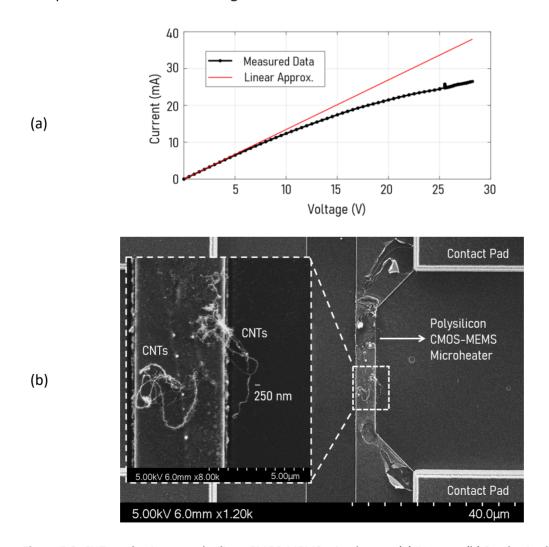

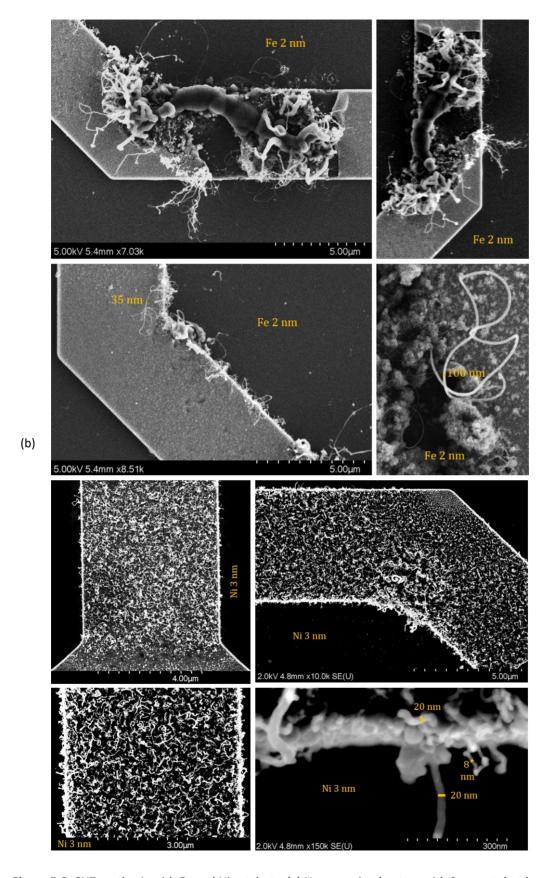

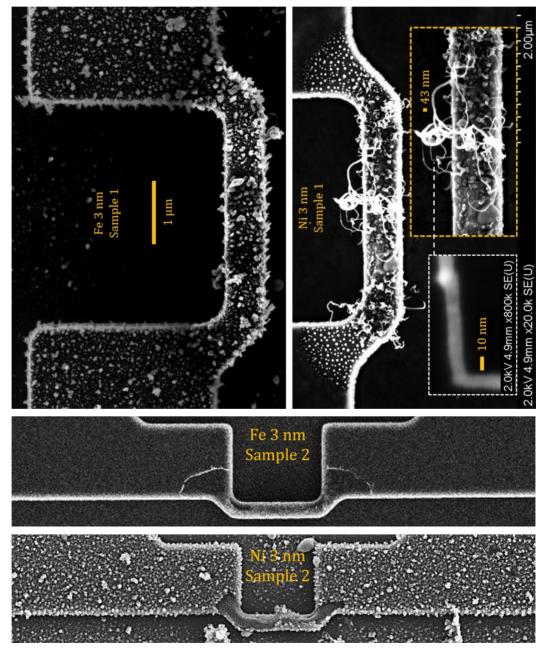

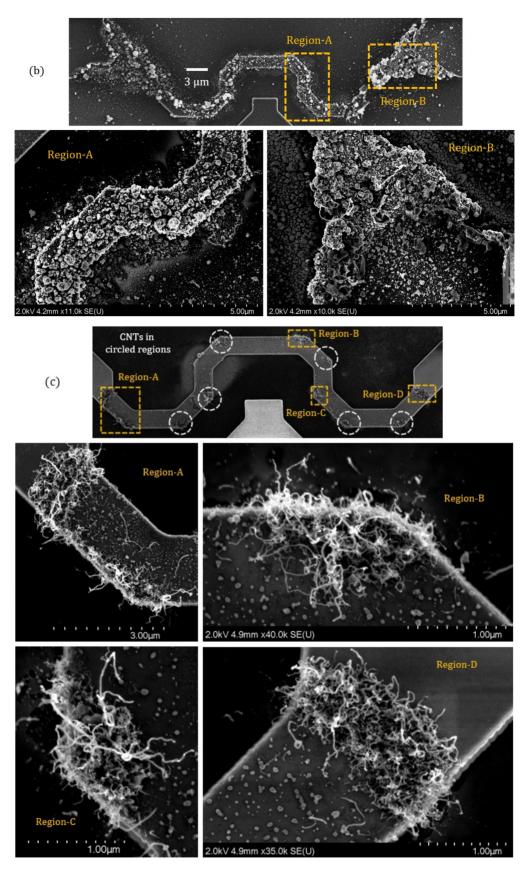

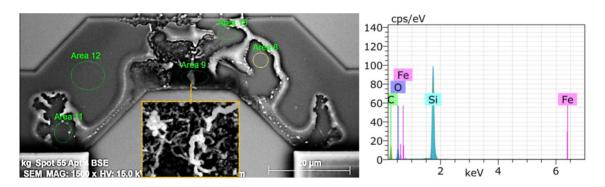

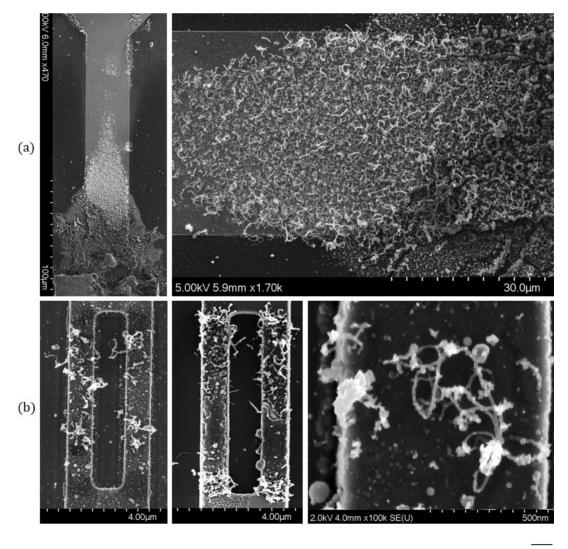

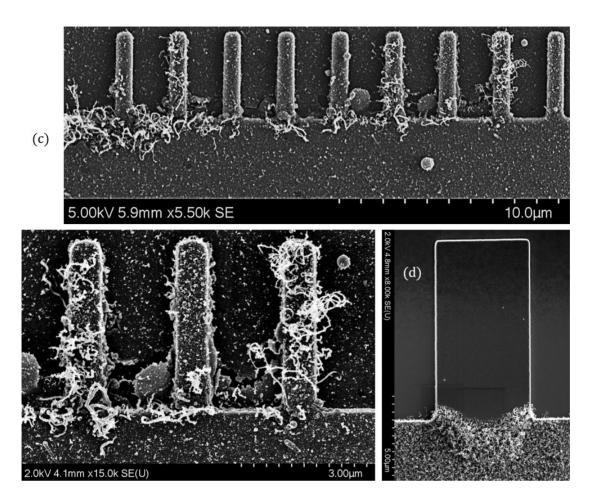

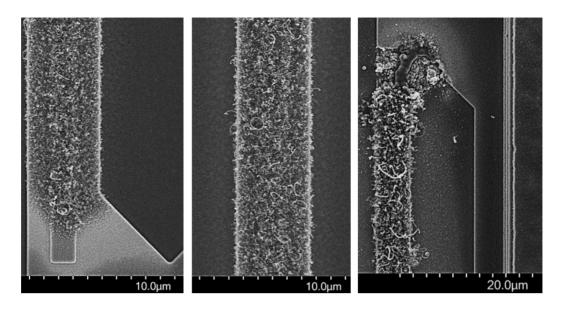

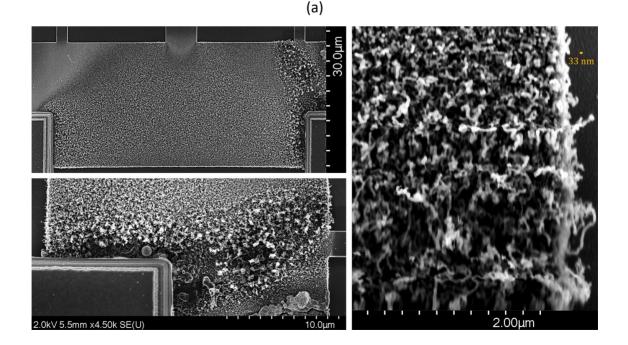

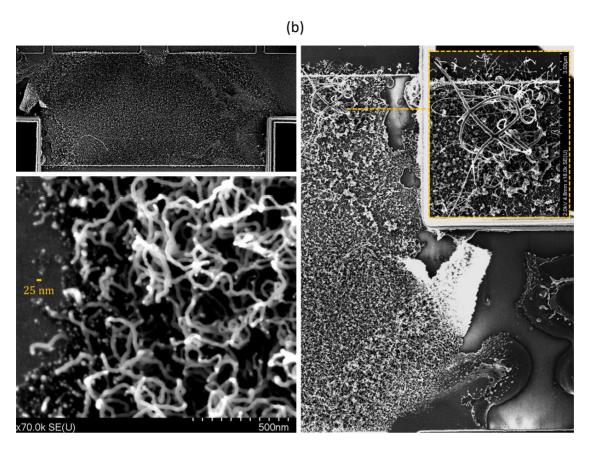

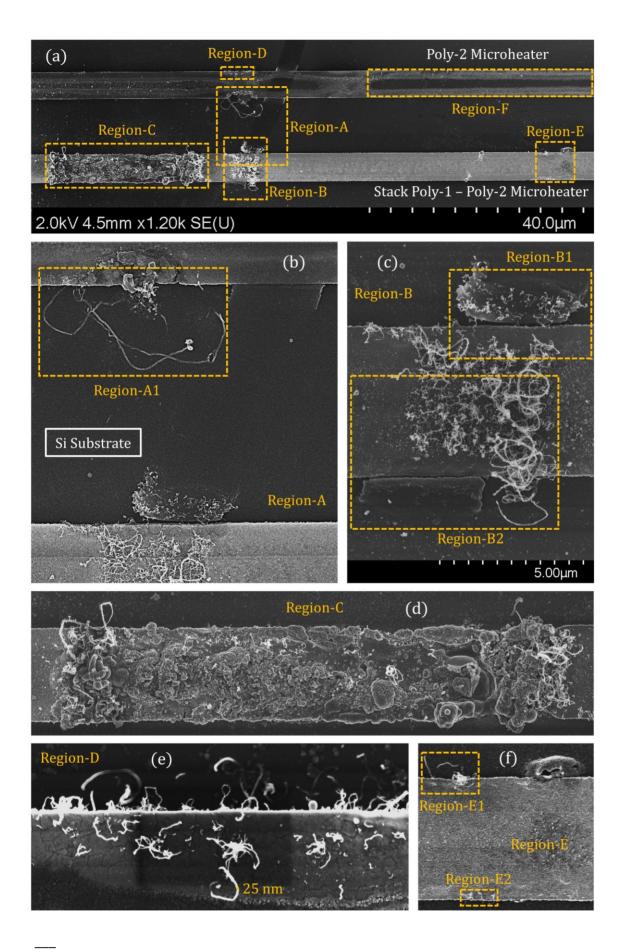

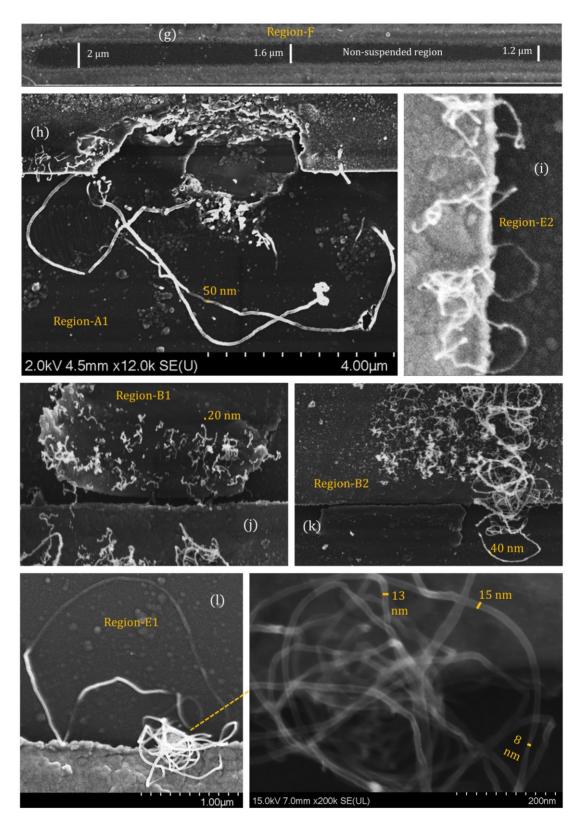

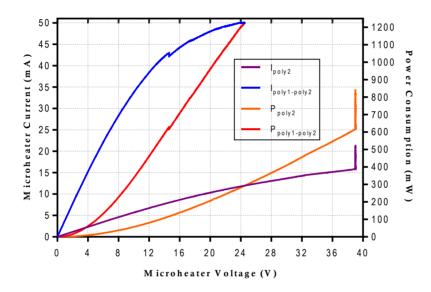

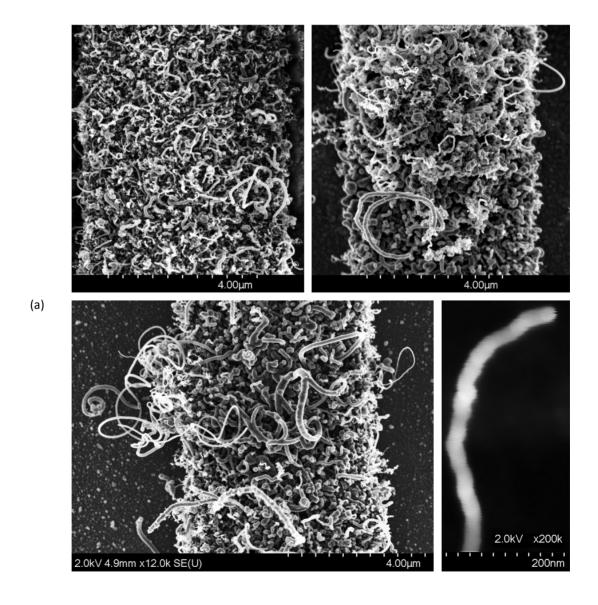

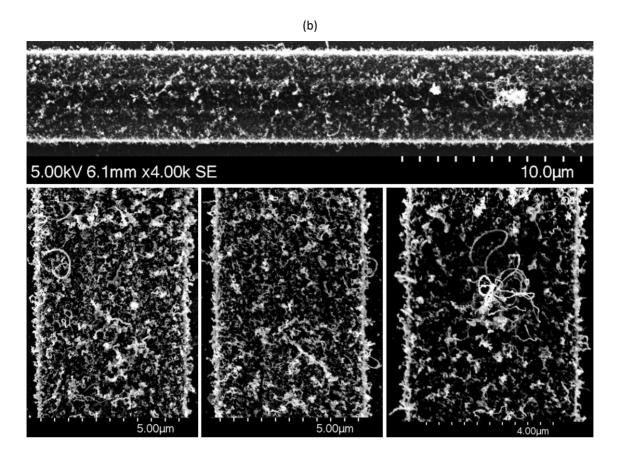

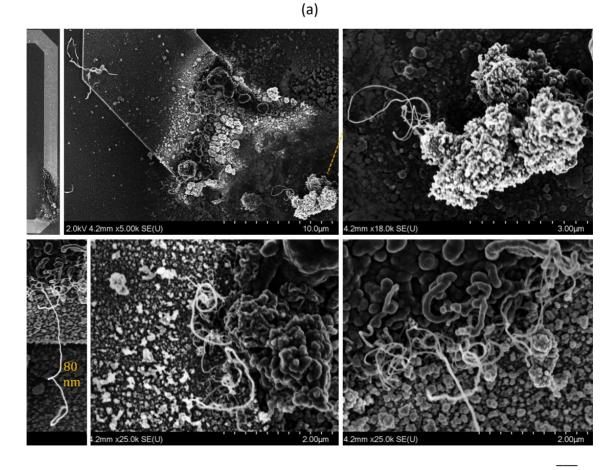

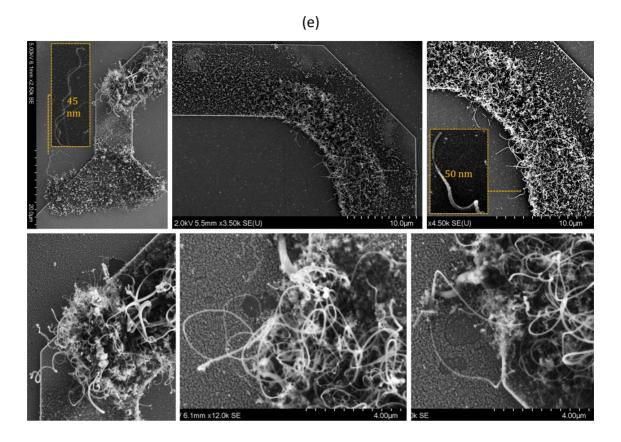

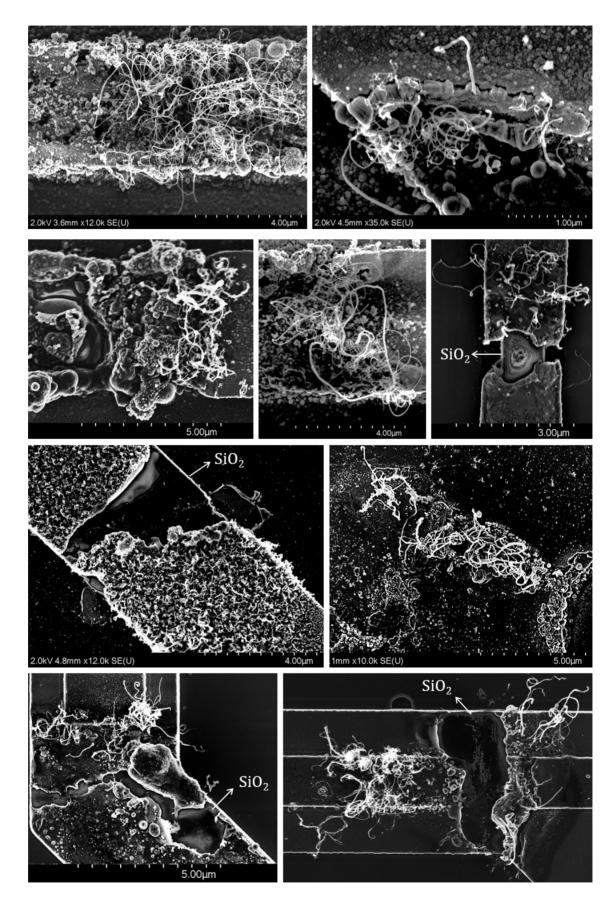

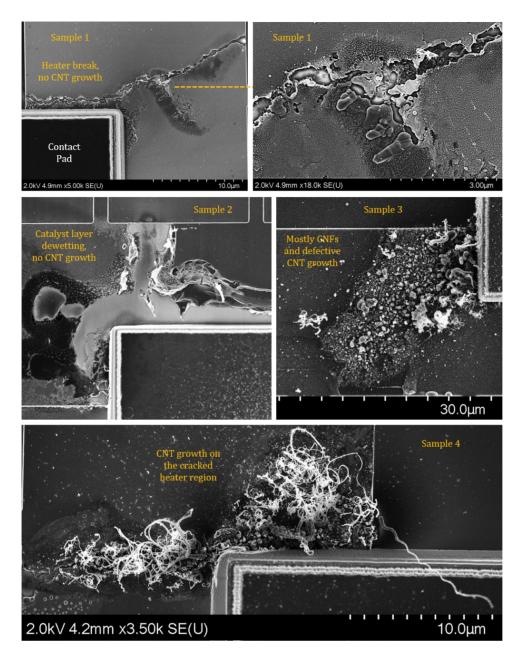

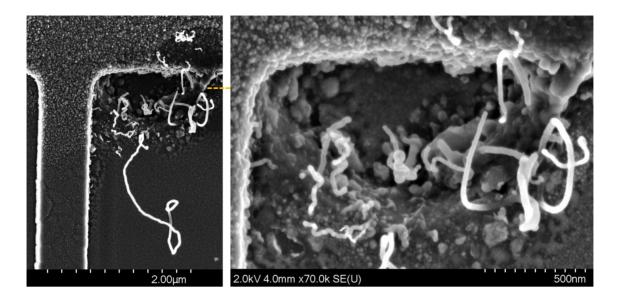

CNTs were successfully synthesized on the polysilicon CMOS-MEMS heaters in a local thermal CVD process. The heaters had low CNT growth temperatures ( $^{\sim}650-750\,^{\circ}\text{C}$ ) before a breakdown, resulting in low yield with Fe catalyst. Growth with Ni provided higher yield with relatively lower diameter ( $^{\sim}20$  nm). CNT growth was investigated on various non-suspended and suspended microheaters. Adding H $_2$  reduction gas improved growth quality. The growth process needs further development to grow longer CNTs within the obtained temperatures. Thermal instability issues of thin polysilicon layers were addressed, which made the CNT growth process challenging. Synthesized CNTs on two neighbouring heaters established a connection through the Si substrate; one of which was utilized to demonstrate gas and pressure sensing. To the author's knowledge, this is the first demonstration report for sensing applications using locally synthesized CNTs on the polysilicon layers of a commercial low-cost bulk CMOS technology.

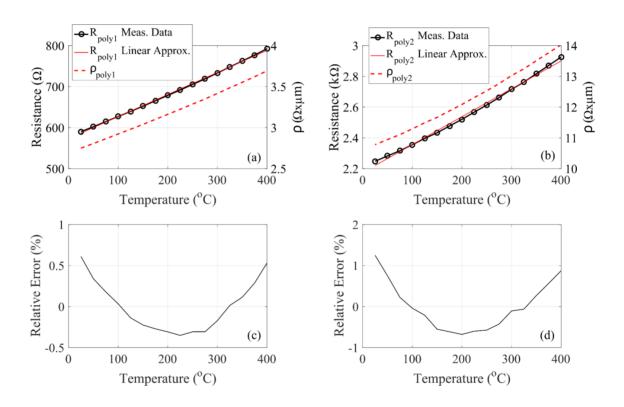

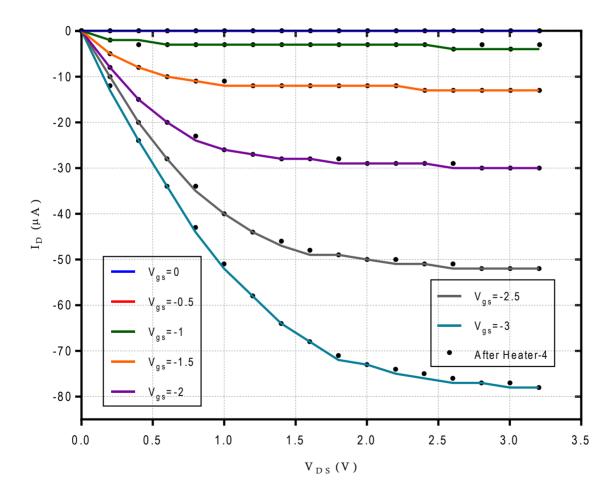

Two CMOS microstructures were calibrated for on-chip temperature sensing. Results show that chip temperature ranging from room-temperature to 200 °C can be estimated with a deviation below 2 °C between the two sensors, while the deviation increases with higher temperature. Two on-chip transistors were also characterized upon heat exposure from different polysilicon microheaters that were used for CNT synthesis. Apart from one case, behaviour of the transistors did not change. Hence, CMOS-compatibility was confirmed for majority of the non-suspended CMOS-MEMS CNT growth structures. Our developed process for heterogenous monolithic integration of CMOS-CNT shows the promise of wafer-level manufacturing of CNT-based sensors by incorporating additional steps in an already existing foundry CMOS process.

**Keywords:** carbon nanotube, local CNT synthesis, CMOS-CNT integration, CMOS microheater, polysilicon microheater, CNT growth on CMOS, CNT-based sensor, gas sensor, pressure sensor, on-chip temperature sensor, thermal analysis

### **List of Papers**

### Paper 1 & 3-7 omitted due to publisher's restrictions

#### Article 1

**A. Roy**, F. Ender, M. Azadmehr, and K. E. Aasmundtveit, "CMOS micro-heater design for direct integration of carbon nanotubes," Microelectronics Reliability, 2017.

https://doi.org/10.1016/j.microrel.2017.05.031

#### **Article 2**

**A. Roy**, M. Azadmehr, B. Q. Ta, P. Häfliger, and K. E. Aasmundtveit, "Design and Fabrication of CMOS Microstructures to Locally Synthesize Carbon Nanotubes for Gas Sensing," Sensors, 2019.

https://doi.org/10.3390/s19194340

#### **Article 3**

**A. Roy**, B. Q. Ta, M. Azadmehr, and K. E. Aasmundtveit, "Post-processing challenges and design improvements of CMOS-MEMS microheaters for local CNT synthesis," *To be submitted*.

#### Article 4

K. E. Aasmundtveit, **A. Roy**, and B. Q. Ta, "Direct Integration of Carbon Nanotubes in CMOS – Towards an Industrially Feasible Process," IEEE Transactions on Nanotechnology, 2020.

https://doi.org/10.1109/TNANO.2019.2961415

My contributions: All results and most writings in Section IV (CNT growth structures in CMOS), contributions in writing and reviewing some parts of the other sections.

#### **Article 5**

**A. Roy**, F. Ender, M. Azadmehr, B. Q. Ta, and K. E. Aasmundtveit, "Design considerations of CMOS micro-heaters to directly synthesize carbon nanotubes for gas sensing applications," IEEE-NANO conference, 2017.

https://doi.org/10.1109/NANO.2017.8117447

#### Article 6

**A. Roy**, M. Azadmehr, P. Häfliger, B. Q. Ta, and K. E. Aasmundtveit, "Direct Synthesis of Carbon Nanotubes in CMOS – Layout of Micro-heaters," IEEE-NANO conference, 2018. https://doi.org/10.1109/NANO.2018.8626363

#### **Article 7**

**A. Roy**, L. Marchetti, M. Azadmehr, P. Häfliger, B. Q. Ta, and K. E. Aasmundtveit, "Characterization of Polysilicon Microstructures to Estimate Local Temperature on CMOS Chips," IEEE-ESTC conference, 2020.

https://doi.org/10.1109/ESTC48849.2020.9229851

### Papers not enclosed in the thesis

#### **Article 8**

K. E. Aasmundtveit, **A. Roy**, & B. Q. Ta, "Carbon Nanotubes Directly Integrated in CMOS by Local Synthesis – Towards a Wafer-Level Process," IEEE-NMDC conference, 2018. https://doi.org/10.1109/NMDC.2018.8605926

#### Article 9

**A. Roy** et al., "Local Synthesis of Carbon Nanotubes on CMOS Microstructures for Gas Sensing," *In preparation*.

Further, six more articles are planned for publication based on the contents from chapter 3 to 8.

### **List of Co-supervised Projects**

- 1. Iqbol Adahamjonov, "Analysis of Test Structures for Ni-Al alloy Microheaters with Reduced Heat Transfer", *Master Thesis*, USN, 2018.

- 2. Nuk Damys, "Design and Fabrication Challenges of MEMS Resonating Gas Sensor", *Master Thesis*, USN, 2018.

- Benjamin C. Figved, Hermon A. Gebrekidan, Arthur W. Haugen and Thomas A. Gabrielsen, "Design, Simulation and Fabrication of MEMS resonating sensors", Bachelor Thesis, USN, 2019.

- 4. Bishwojit Konsam, "Fabrication of SOI Wafer and Mask for an FD-SOI Junctionless Transistor in a MEMS Cleanroom", *Master Thesis*, USN, 2019.

- 5. Arian Nowbahari, "Design of a Low-cost Single Gate Planar Junctionless Transistor", *Master Thesis*, USN, 2019.

- 6. Donatus Leonhard Dress, "Design and Fabrication of Microheaters with SOI Wafers for CNT Synthesis", *Master Thesis*, USN, 2020.

### **Table of contents**

| Pref                              | face     |                                                      |  |  |  |

|-----------------------------------|----------|------------------------------------------------------|--|--|--|

| AcknowledgementV                  |          |                                                      |  |  |  |

| AbstractVII                       |          |                                                      |  |  |  |

| List                              | of Pap   | persIX                                               |  |  |  |

| List of Co-supervised Projects XI |          |                                                      |  |  |  |

|                                   |          |                                                      |  |  |  |

| Cha                               | pter 1   |                                                      |  |  |  |

| Intr                              | oducti   | on1                                                  |  |  |  |

| 1.1                               | The w    | orld of macro, micro and nano1                       |  |  |  |

| 1.2                               | Backg    | round & motivation2                                  |  |  |  |

| 1.3                               | Carbo    | on Nanotubes5                                        |  |  |  |

|                                   | 1.3.1    | Classifications5                                     |  |  |  |

|                                   | 1.3.2    | Properties and applications6                         |  |  |  |

|                                   | 1.3.3    | Synthesis methods9                                   |  |  |  |

| 1.4                               | CNT i    | ntegration in microsystems9                          |  |  |  |

|                                   | 1.4.1    | Different integration approaches10                   |  |  |  |

|                                   | 1.4.2    | Local CNT synthesis on microstructures               |  |  |  |

|                                   | 1.4.3    | Challenges of direct CNT growth on CMOS14            |  |  |  |

|                                   | 1.4.4    | CMOS-MEMS micromachined systems                      |  |  |  |

|                                   | 1.4.5    | Direct CMOS-CNT integration for sensing applications |  |  |  |

|                                   | 1.4.6    | Towards CNT-based commercial sensors                 |  |  |  |

| 1.5                               | Resea    | arch objectives and dissertation outline22           |  |  |  |

|                                   |          |                                                      |  |  |  |

| Cha                               | pter 2   |                                                      |  |  |  |

| Fea                               | sibility | Analysis for CNT Growth on CMOS27                    |  |  |  |

| 2.1                               | Introd   | duction27                                            |  |  |  |

| 2.2                               | CMOS     | S materials for microheater design27                 |  |  |  |

| 2.3 | Microheater design considerations32 |                                                |    |

|-----|-------------------------------------|------------------------------------------------|----|

| 2.4 | Thern                               | no-mechanical analysis of microheaters         | 35 |

|     | 2.4.1                               | Polysilicon microheaters                       | 36 |

|     | 2.4.2                               | Poly-1 & Poly-2 stacked microheaters           | 40 |

|     | 2.4.3                               | Al–Ni microheaters                             | 41 |

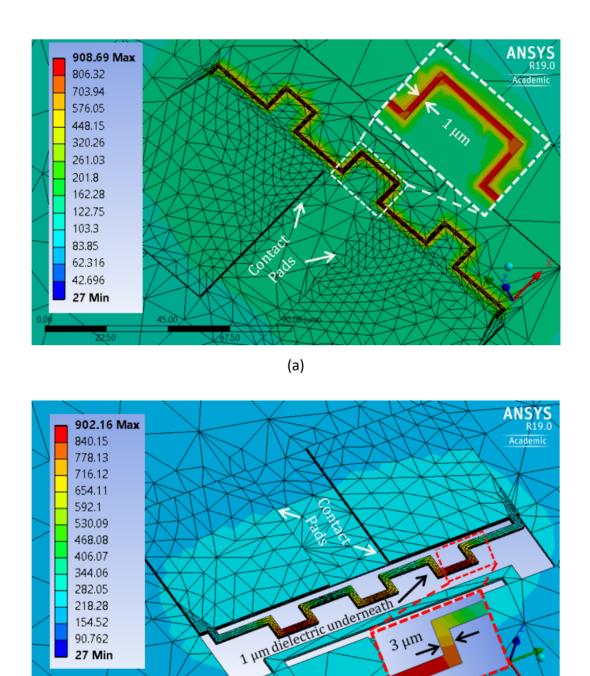

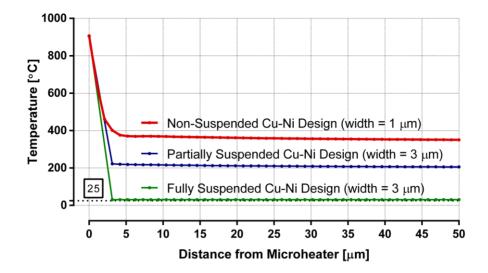

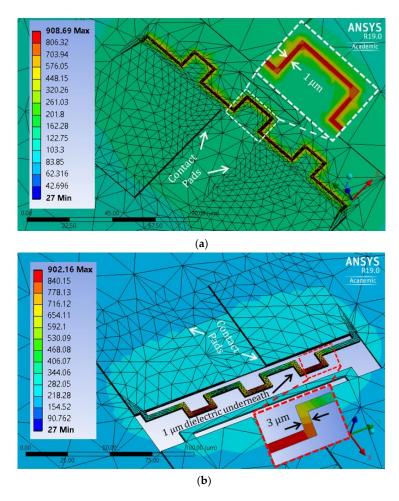

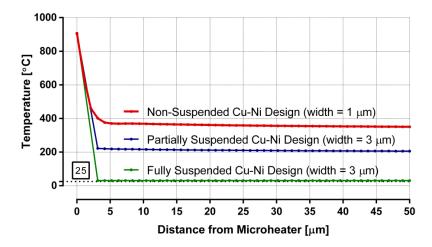

|     | 2.4.4                               | Cu–Ni microheaters                             | 44 |

| 2.5 | Concl                               | usion                                          | 45 |

|     |                                     |                                                |    |

| Cha | pter 3                              |                                                |    |

| CM  | OS Chi                              | p Design                                       | 47 |

| 3.1 | Introd                              | luction4                                       | 47 |

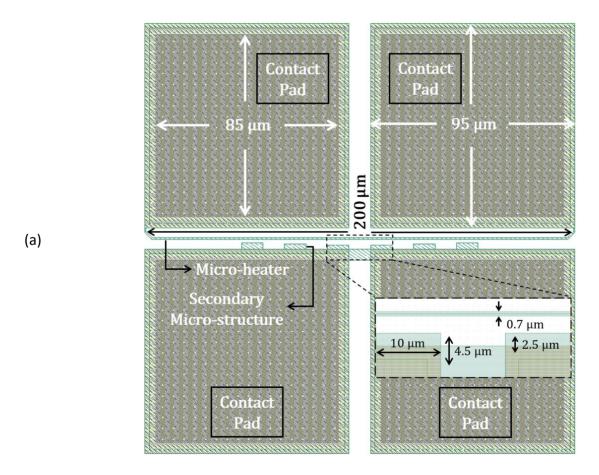

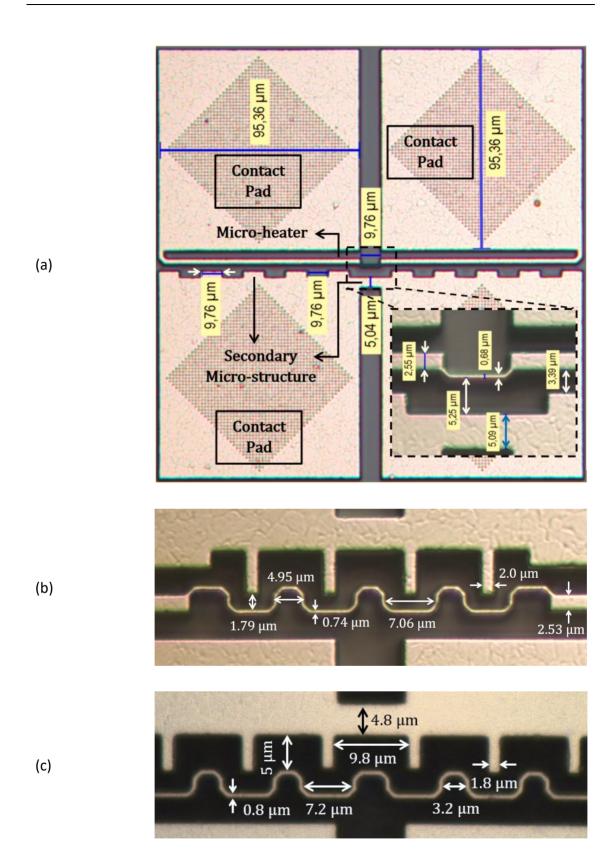

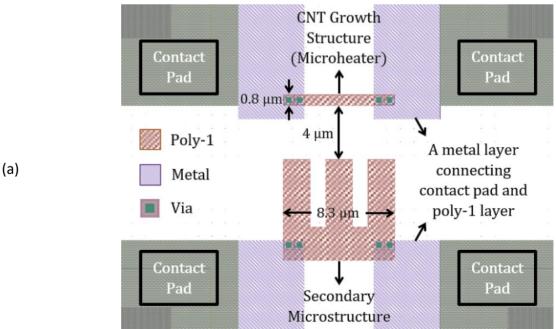

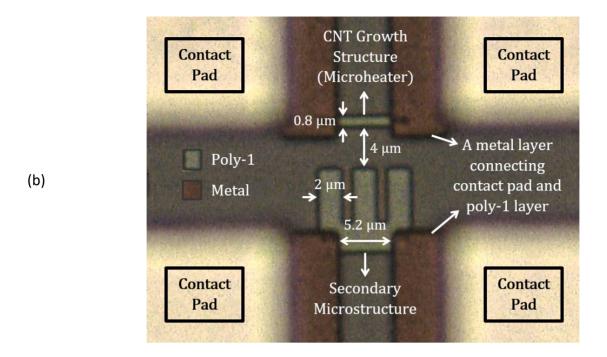

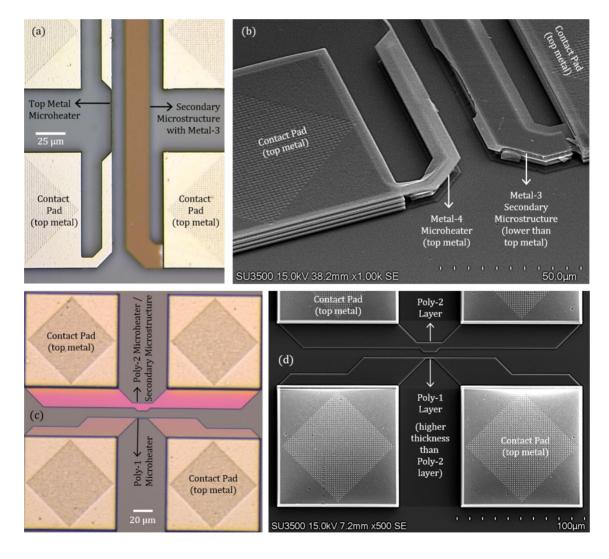

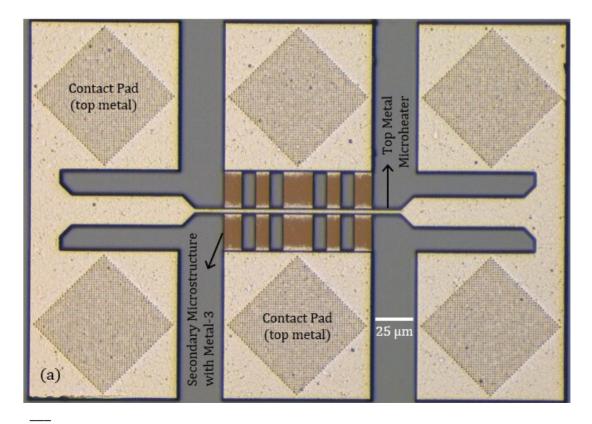

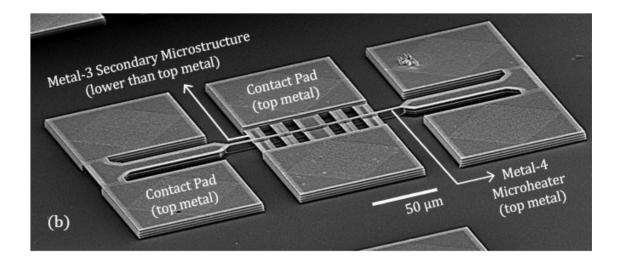

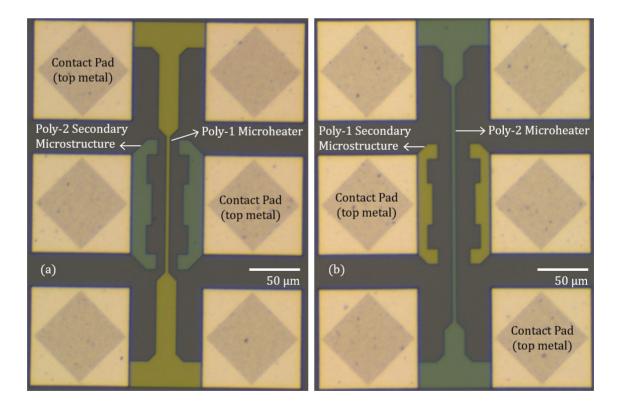

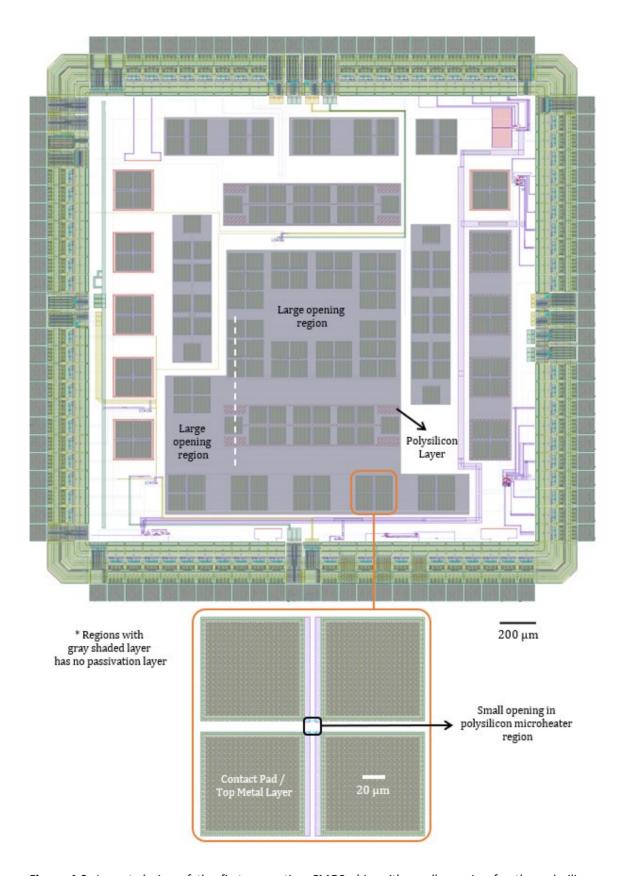

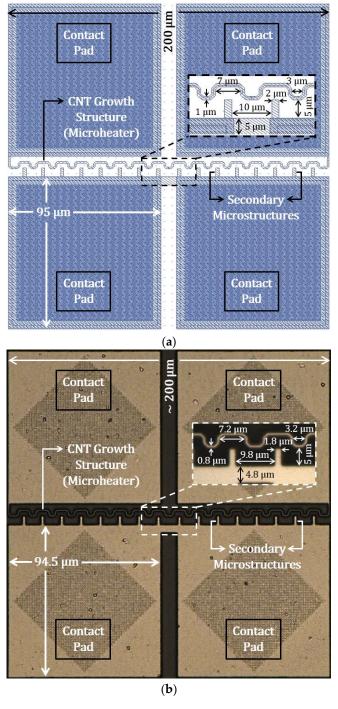

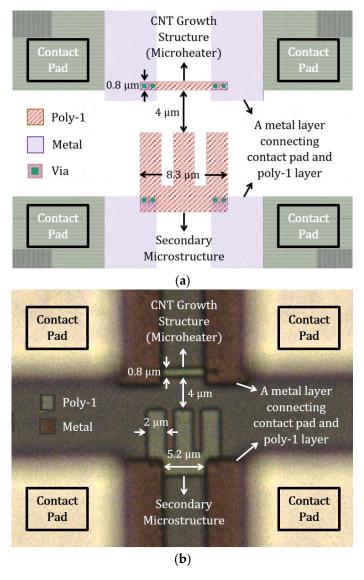

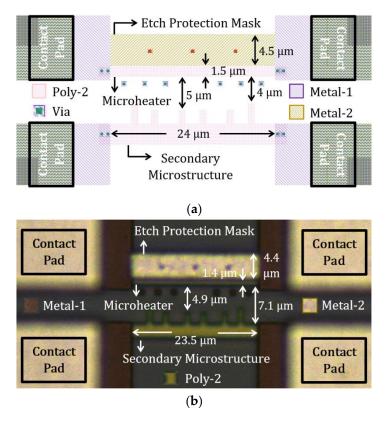

| 3.2 | Layou                               | ts and micrographs4                            | 48 |

|     | 3.2.1                               | Aluminium designs                              | 48 |

|     | 3.2.2                               | Polysilicon designs                            | 51 |

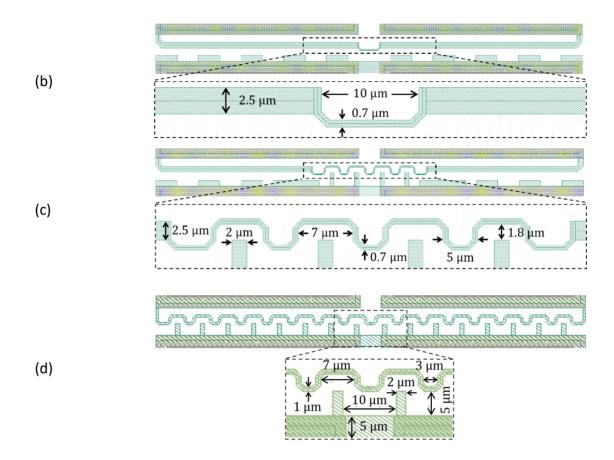

| 3.3 | Vario                               | us microheater features                        | 53 |

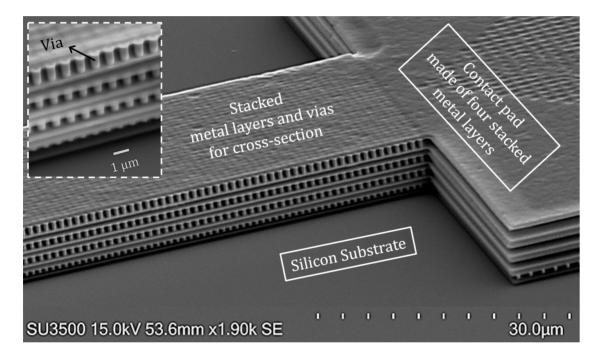

|     | 3.3.1                               | Metal layer as etching mask                    | 54 |

|     | 3.3.2                               | Via as etching mask                            | 56 |

|     | 3.3.3                               | Microheaters with etching holes                | 58 |

|     | 3.3.4                               | Microheaters covered with passivation layers   | 58 |

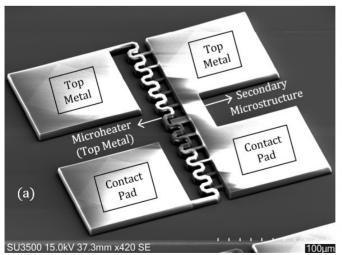

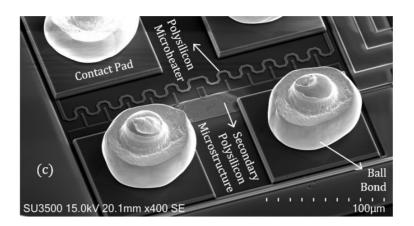

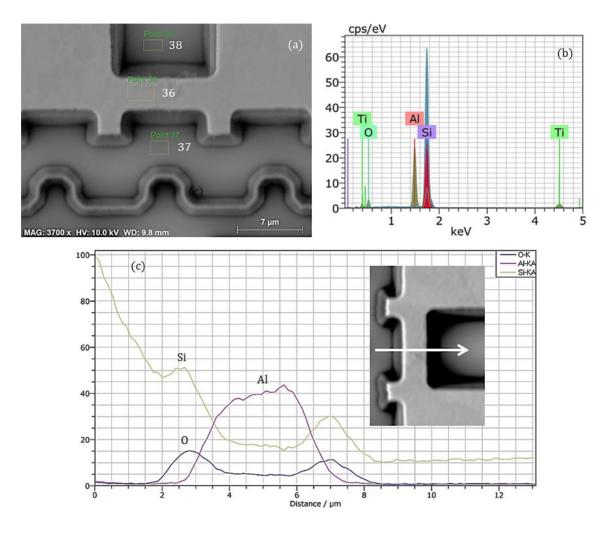

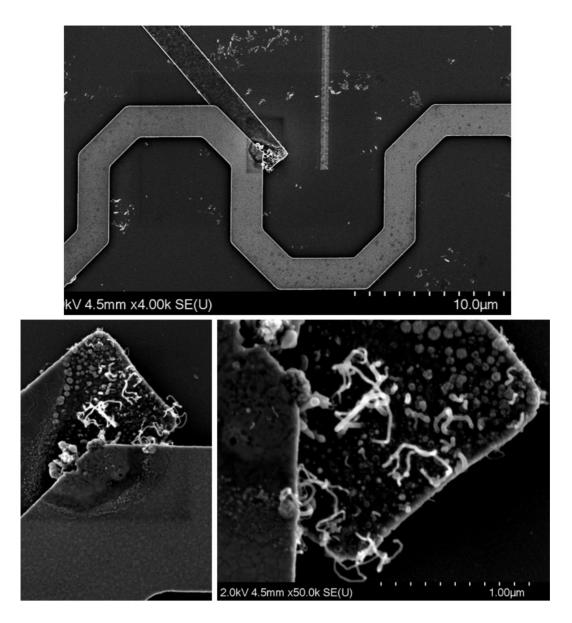

|     | 3.3.5                               | Wave-shaped microheaters                       | 60 |

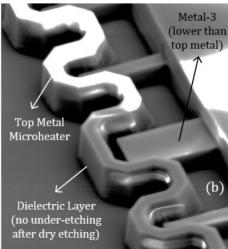

|     | 3.3.6                               | Microheaters with height variation             | 62 |

|     | 3.3.7                               | Microheaters with four terminals               | 64 |

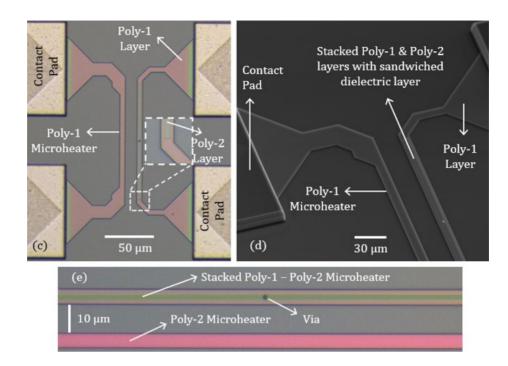

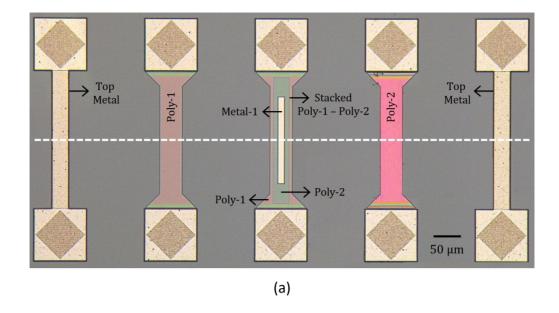

|     | 3.3.8                               | Microheaters with stacked polysilicon layers   | 64 |

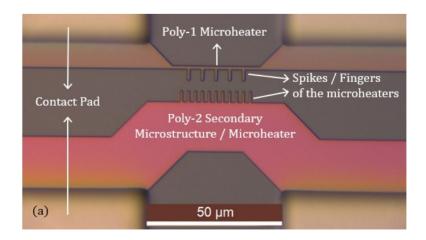

|     | 3.3.9                               | Microheaters with spikes                       | 65 |

|     | 3.3.10                              | Three-microheater configuration                | 67 |

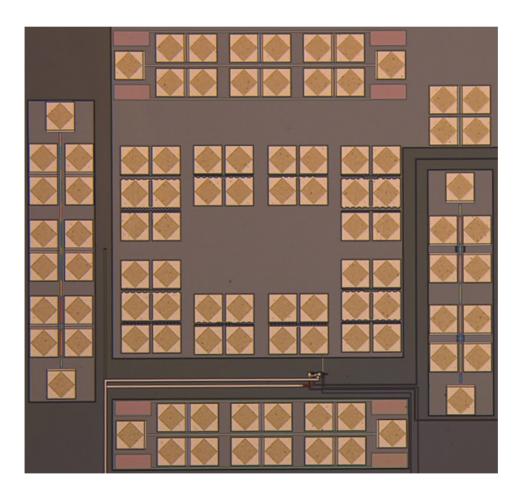

|     | 3.3.11                              | . Rectangular arrangement of microheaters      | 67 |

|     | 3.3.12                              | Microheaters with small and large surface area | 68 |

| 3.4 | Micro                               | heater characterizations                       | 69 |

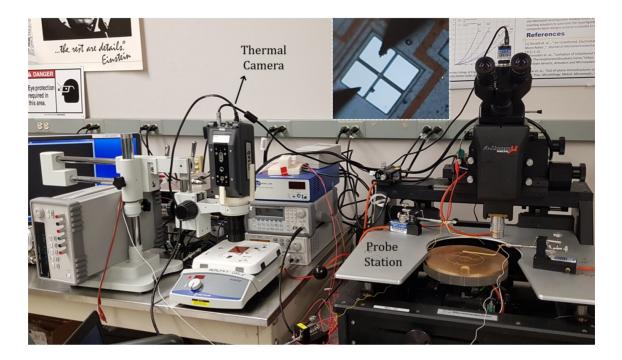

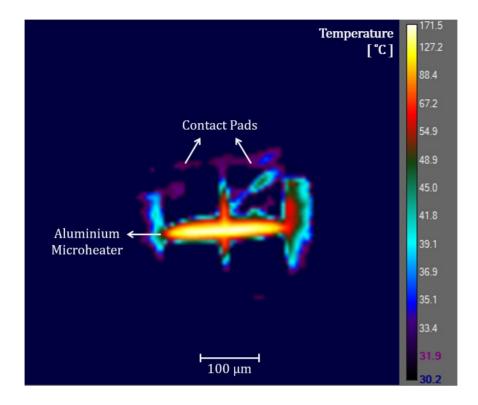

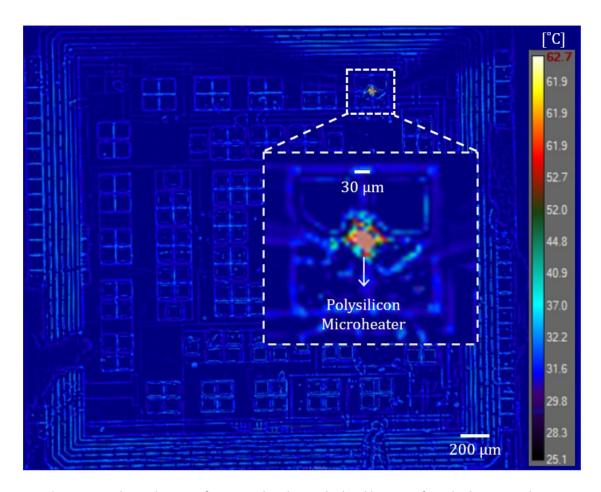

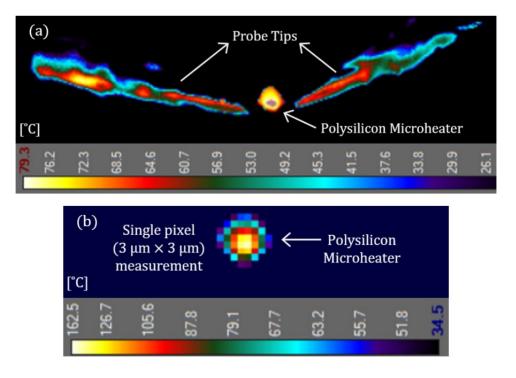

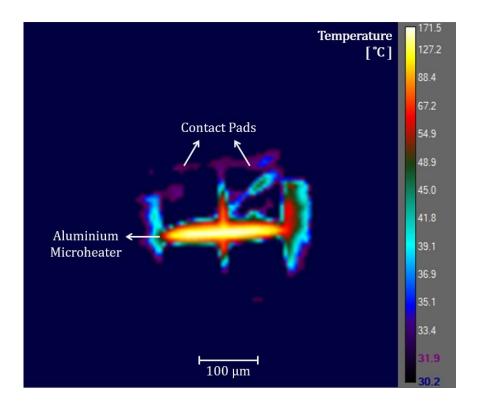

| 3.5 | IR microscopy72                     |                                                |    |

| 3.6 | Concl                               | usion                                          | 76 |

### **Chapter 4**

| Pos | t-processing of CMOS-MEMS Microheaters                   | 77  |

|-----|----------------------------------------------------------|-----|

| 4.1 | Introduction                                             | 77  |

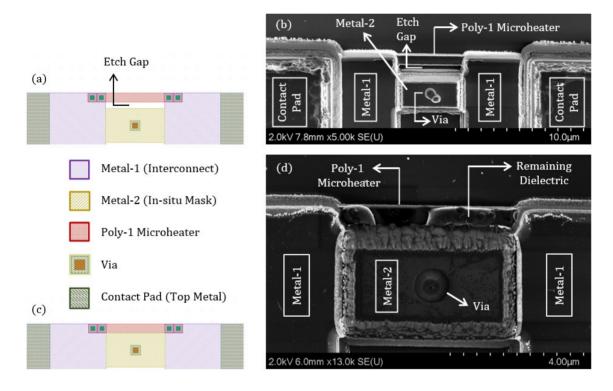

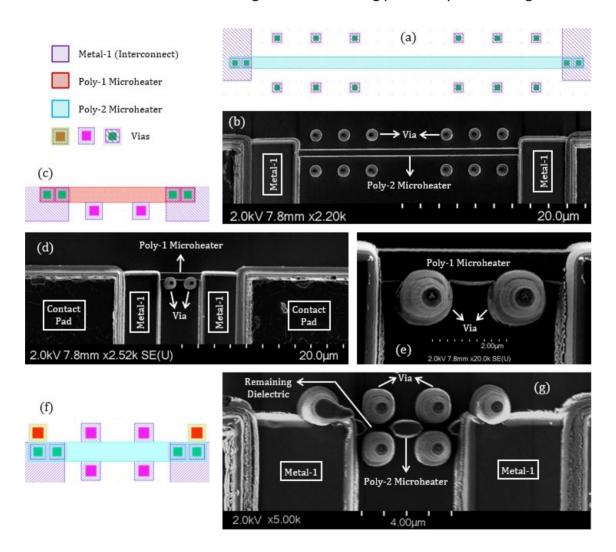

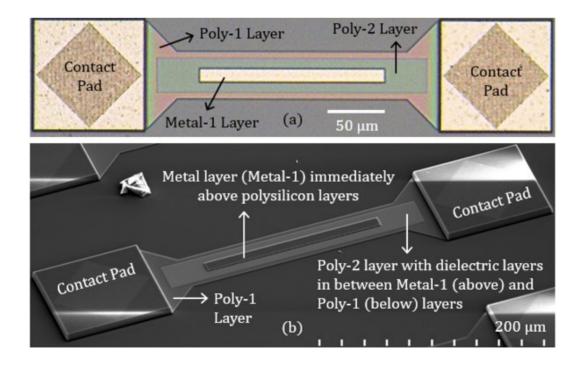

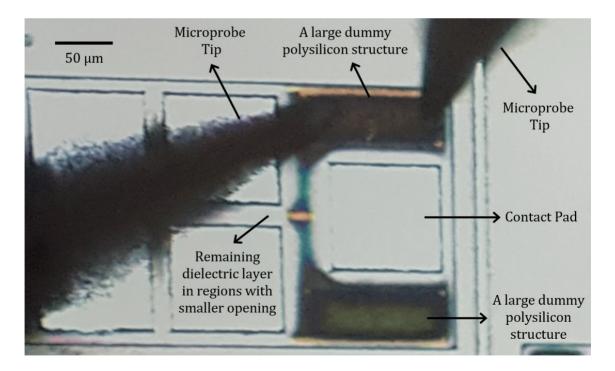

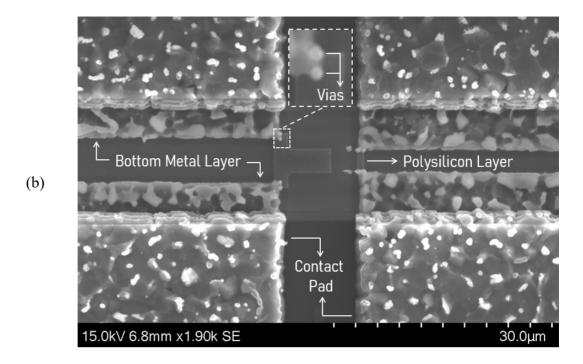

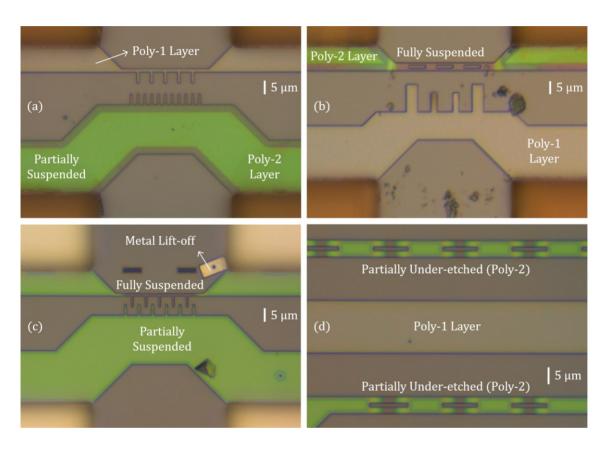

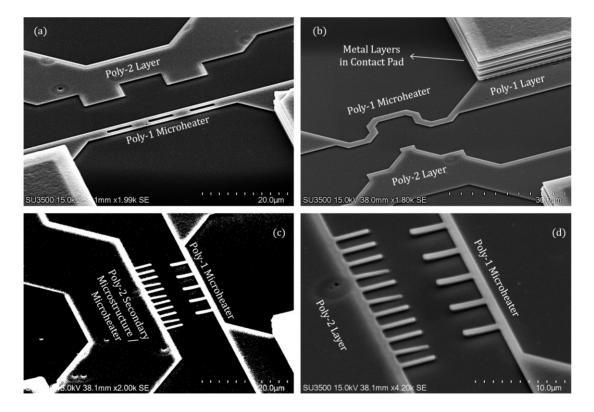

| 4.2 | Polysilicon microheater design layers                    | 77  |

| 4.3 | Fabrication process of CMOS-MEMS heaters                 | 80  |

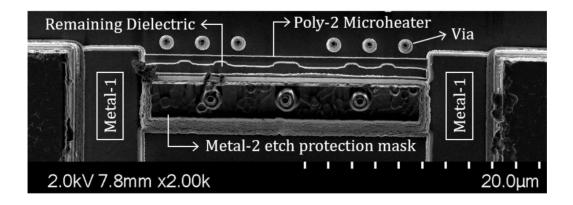

| 4.4 | Post-processing challenges and heater design limitations | 82  |

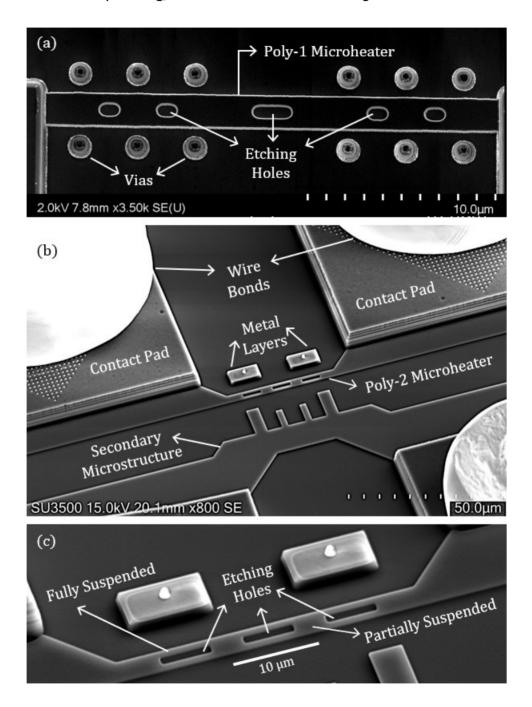

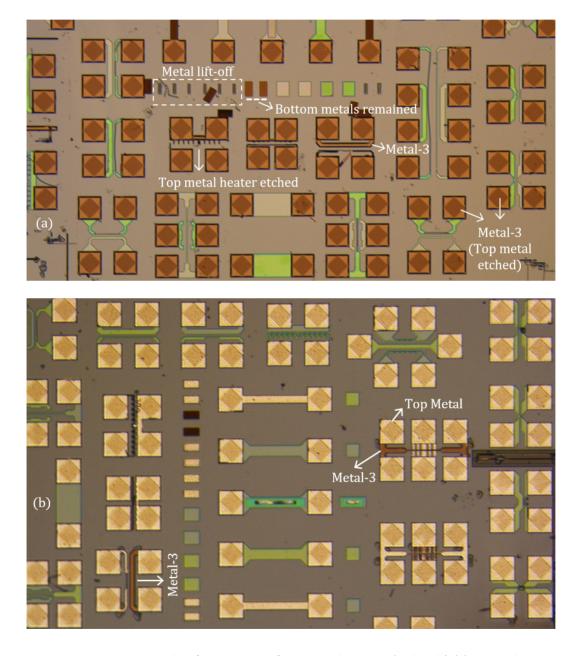

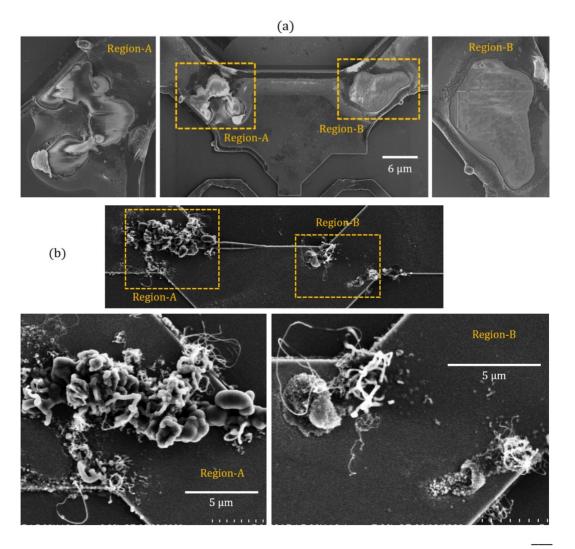

| 4.5 | Improved designs and post-processing                     | 88  |

| 4.6 | RIE recipe development                                   | 93  |

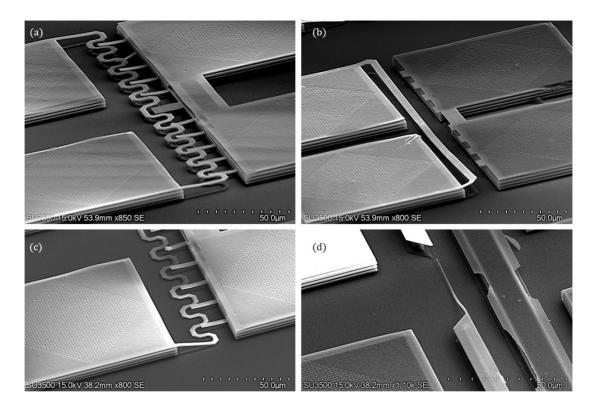

| 4.7 | Microheater suspension                                   | 98  |

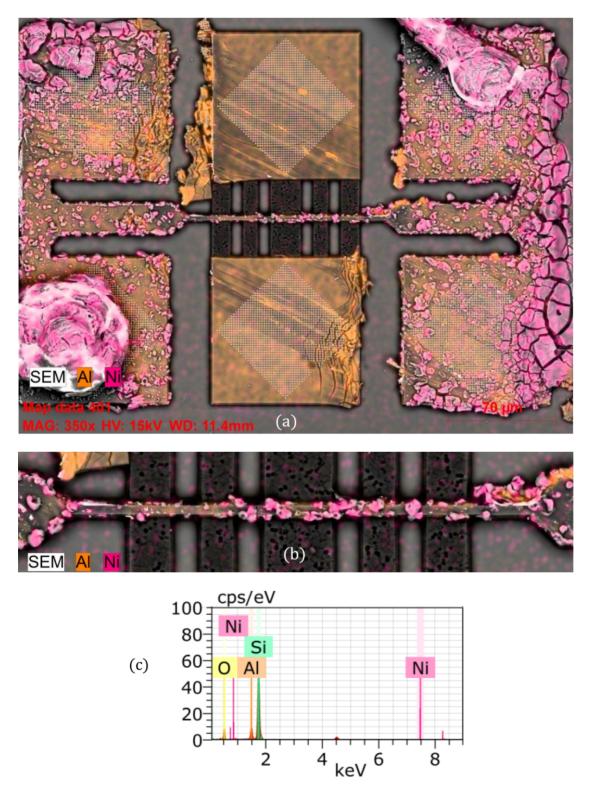

| 4.8 | Nickel electroplating on metal heaters                   | 107 |

| 4.9 | Conclusion                                               | 109 |

|     |                                                          |     |

| Cha | pter 5                                                   |     |

| CNT | Γ Synthesis on CMOS                                      | 111 |

| 5.1 | Introduction                                             | 111 |

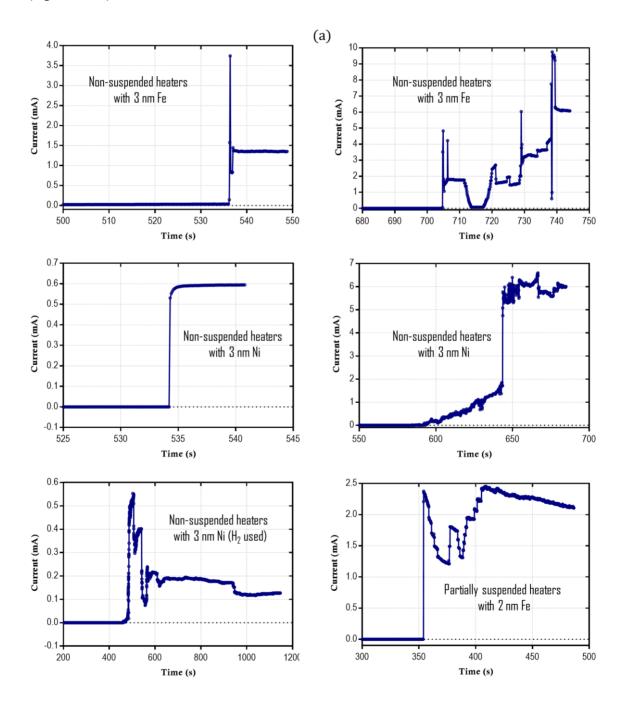

| 5.2 | CNT growth process                                       | 111 |

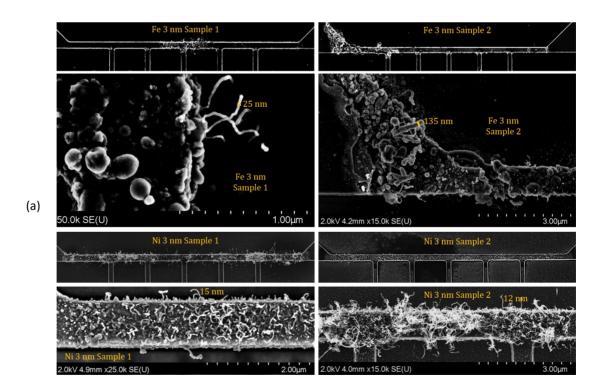

| 5.3 | Effect of catalysts                                      | 115 |

| 5.4 | Growth on different polysilicon microheaters             | 127 |

| 5.5 | Growth on suspended microheaters                         | 133 |

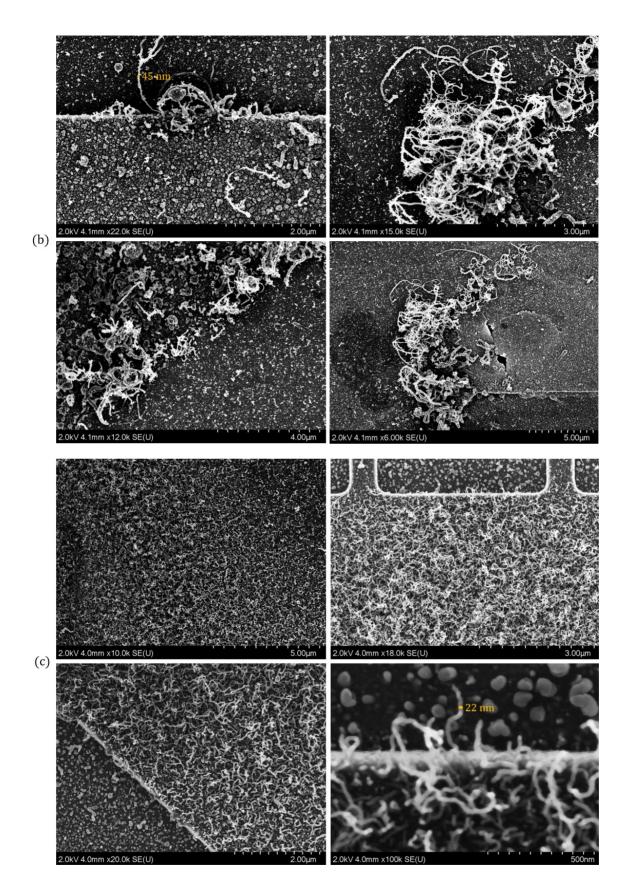

| 5.6 | Effect of H <sub>2</sub> in CNT synthesis                | 138 |

| 5.7 | Resultant CNTs and defects                               | 143 |

| 5.8 | Conclusion                                               | 150 |

| Cha | opter 6                                                  |     |

| Sen | sing Applications                                        | 151 |

|     | Introduction                                             |     |

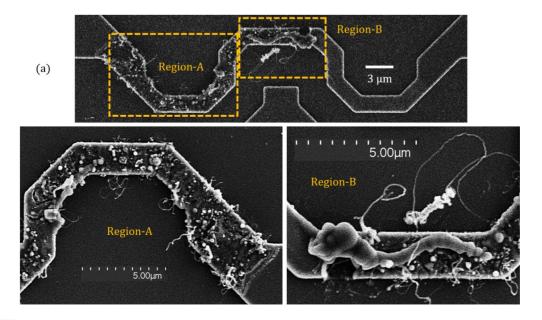

| 6.2 | CNT growth towards adjacent heater                       | 151 |

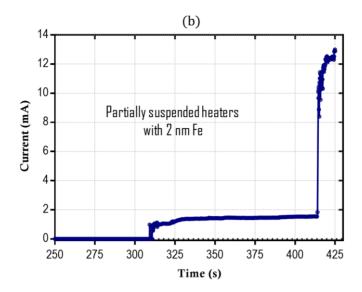

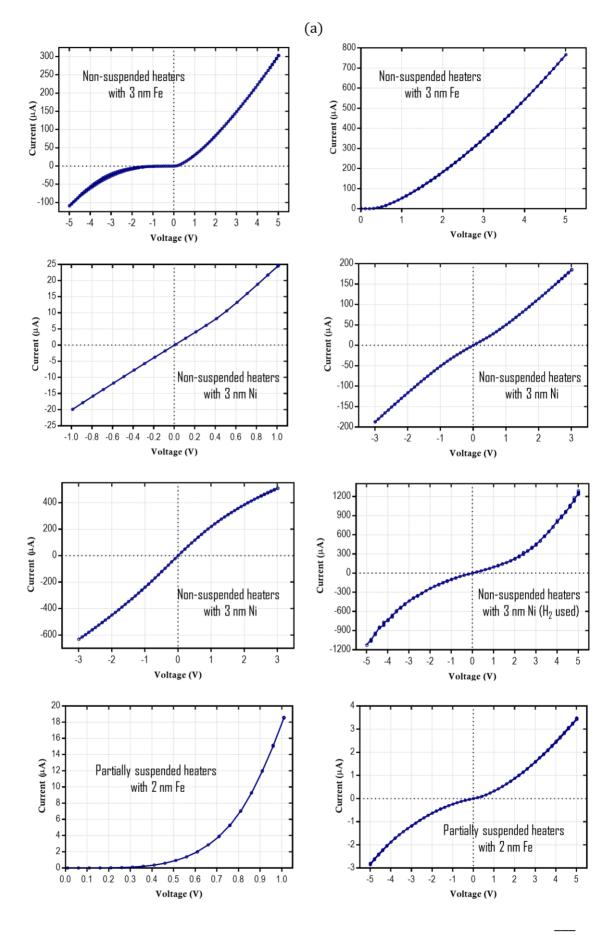

| 6.3 | CNT connections and I-V curves                           | 154 |

| 6.4 | Gas sensing                                              | 158 |

| 6.5                                                         | Pressure response                                        | 53                               |

|-------------------------------------------------------------|----------------------------------------------------------|----------------------------------|

| 6.6                                                         | Conclusion                                               | 55                               |

|                                                             |                                                          |                                  |

| Cha                                                         | oter 7                                                   |                                  |

| CM                                                          | OS Microheater Challenges and Wafer-level Scaling 16     | <b>57</b>                        |

| 7.1                                                         | Introduction                                             | 57                               |

| 7.2                                                         | Electrical control and temperature limitations16         | 57                               |

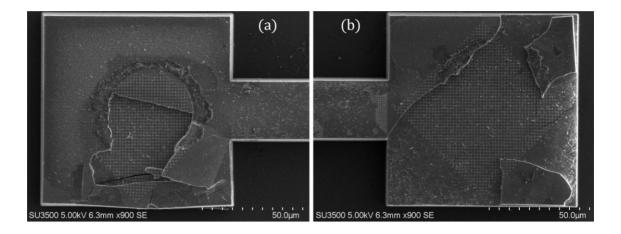

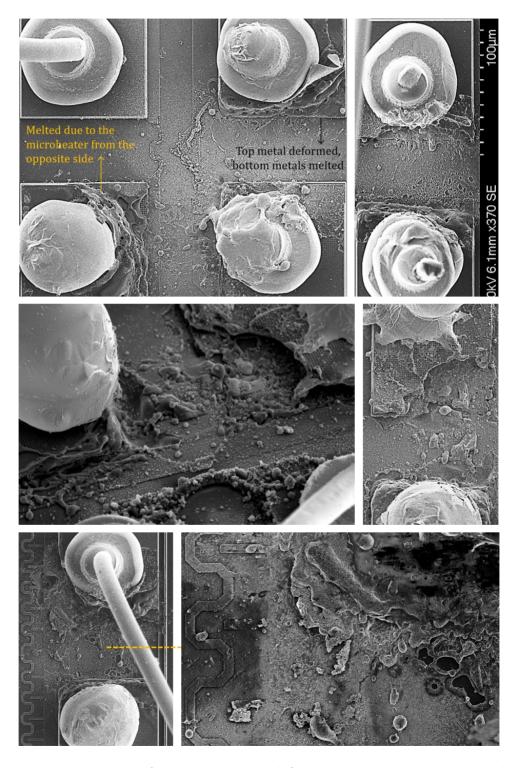

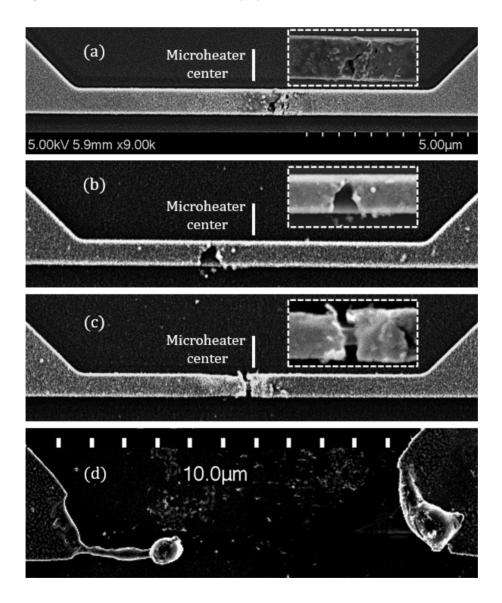

| 7.3                                                         | Heater damages                                           | 72                               |

| 7.4                                                         | CNT growth development18                                 | 30                               |

| 7.5                                                         | Towards wafer-level process for mass production          | 32                               |

| 7.6                                                         | Conclusion                                               | 35                               |

|                                                             |                                                          |                                  |

| Cha                                                         | oter 8                                                   |                                  |

|                                                             | uler o                                                   |                                  |

|                                                             |                                                          |                                  |

|                                                             | chip Temperature Sensing and Transistor Characterization | 37                               |

| On-                                                         |                                                          |                                  |

| <b>On-</b><br>8.1                                           | chip Temperature Sensing and Transistor Characterization | 37                               |

| <b>On-</b><br>8.1<br>8.2                                    | Chip Temperature Sensing and Transistor Characterization | 37<br>38                         |

| On-<br>8.1<br>8.2<br>8.3                                    | Chip Temperature Sensing and Transistor Characterization | 37<br>38<br>90                   |

| On-<br>8.1<br>8.2<br>8.3<br>8.4                             | Chip Temperature Sensing and Transistor Characterization | 37<br>38<br>90<br>96             |

| On-<br>8.1<br>8.2<br>8.3<br>8.4<br>8.5                      | Chip Temperature Sensing and Transistor Characterization | 37<br>38<br>90<br>96             |

| On-<br>8.1<br>8.2<br>8.3<br>8.4<br>8.5<br>8.6               | Chip Temperature Sensing and Transistor Characterization | 37<br>38<br>90<br>96<br>98       |

| On-<br>8.1<br>8.2<br>8.3<br>8.4<br>8.5<br>8.6               | Chip Temperature Sensing and Transistor Characterization | 37<br>38<br>90<br>96<br>98       |

| On-<br>8.1<br>8.2<br>8.3<br>8.4<br>8.5<br>8.6<br>8.7        | Chip Temperature Sensing and Transistor Characterization | 37<br>38<br>90<br>96<br>98       |

| On-<br>8.1<br>8.2<br>8.3<br>8.4<br>8.5<br>8.6<br>8.7        | Chip Temperature Sensing and Transistor Characterization | 37<br>38<br>90<br>96<br>98<br>93 |

| On-<br>8.1<br>8.2<br>8.3<br>8.4<br>8.5<br>8.6<br>8.7<br>Cha | Chip Temperature Sensing and Transistor Characterization | 37<br>38<br>90<br>96<br>98<br>93 |

| Appendix   | 209 |

|------------|-----|

| References | 215 |

| Article 1  | 237 |

| Article 2  | 249 |

| Article 3  | 273 |

| Article 4  | 293 |

| Article 5  | 305 |

| Article 6  | 313 |

| Article 7  | 319 |

### **Chapter 1**

### Introduction

### 1.1 The world of macro, micro and nano

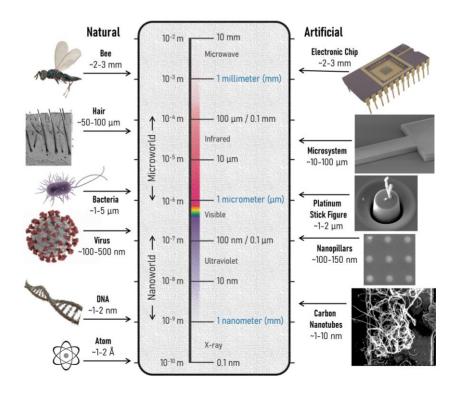

We measure the size of objects and distances based on a standard reference size defined by us. In the International System of Units (SI), we defined the unit of length as 'metre' through the fundamental constant of the speed of light and another fixed value, natural resonance frequency of the Caesium atom. Conveniently, this standard reference size is very much comparable to an average human size. We can then scale up or down, preferably in the order of thousands, to express the distance or size of something. However, it is easy to lose the grasp over the size of a thing as it starts to get smaller or larger relative to the world around us. We can certainly express the size of something in numbers, but it often becomes difficult to comprehend such values with our human senses. The illustration in *Figure 1.1* is an attempt to comprehend the relative sizes of different natural and artificial things at various scales.

Figure 1.1: Relative sizes of various natural and artificial things in macro, micro and nanoscale.

Macroworld can be defined in terms of the sizes in human scale, where we can see the things with the naked eye and handle them with ease. Through our regular interaction with the macroworld, the immensity of space around us at the large scale is apparent, whereas the abundance of space at the small scale is not often perceived due to the relative nature of size. To express the vastness of space in small scale, German physicist Emil Wiechert mentioned in 1897 that the universe can be infinite in all directions, not only above us in the large but also below us in the small, as quoted by physicist Freeman Dyson in his book "Infinite in All Directions" [1].

How large is the world of micro? If we see from the perspective of nanostructures, it is as large as kilometres to us. With the envision of utilizing the space at the molecular level to manufacture nanoscale machines, a renowned physicist once stated:

"There is plenty of room at the bottom."

- Richard Feynman, 1959

Shrinking in size can provide us a lot of room to build micro or nanomachines apart from other advantages, but we also need to make a link with our macroworld to interact with the system. Therefore, we aim to establish our connection from the world of macro to nano through the world of micro.

### 1.2 Background and motivation

Miniaturized systems such as microdevices bring numerous benefits over its macro counterpart, being small and lightweight is only a part of it. The microdevices have high resistance to shock and vibration [2,3], thus ensure high robustness and reliability. Moreover, a large array of microdevices can be fabricated parallelly in batch by photolithography, which corresponds to low manufacturing cost. A microsystem can become even more interesting with the inclusion of nanomaterials.

Nanomaterials are simply materials sized in nanoscale, where at least one dimension of the material is typically considered less than 100 nm. Material at the small scale behaves differently than they do at the macroscopic level as many negligible effects at the macroscale become prominent at the micro and nanoscale, for example, surface tension

becomes a more dominant force than gravity [4–7]. Although properties of materials at microscale resembles macroscale, changes in material properties start to appear at nanoscale due to the domination of surface effects [4,8], making nanoworlds fundamentally different than the world at larger scale.

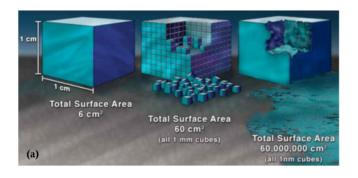

The unique and remarkable physical [9], electronic [10], thermal [11], optical [12], mechanical [13], chemical [14] properties of nanomaterials can be harnessed in numerous innovative applications [15–21]. The nanomaterials can also be engineered for modifying their physicochemical properties to enhance performance in desired utilization [22–26]. Nanomaterials with their reduced size have huge surface area relative to their volume (*Figure 1.2a*). As the particle size of a material reduces, the surface area of the nanoparticle increases exponentially with respect to its volume; below a certain particle size, the number of atoms at the surface of the nanoparticle exceeds the amount inside it (*Figure 1.2b*). Surface effects of a nanoparticle starts to dominate with the increase in surface-to-volume ratio, influencing drastic changes in its material properties [15,16,27–29], which in turn facilitates nanotechnology.

**Figure 1.2:** Effect of miniaturization. (a) Increase in surface area with decrease in cube size [30], (b) Variation in surface and bulk atom ratio with nanoparticle size [15,28].

Based on the composition, nanomaterials can be organic (e.g., carbon-based, dendrimers, polymers), inorganic (e.g., metals, metal oxides, quantum dots) and composites (e.g., organic-inorganic, organic-organic, inorganic-inorganic) [15,25,31]. Among them, carbon-based nanomaterials such as fullerenes, carbon nanotubes, graphene, and carbon quantum dots are very attractive in fundamental research due to their exceptional material properties and scope for various potential applications in

different technological fields [32–43]. One-dimensional (1D) carbon nanomaterial, carbon nanotubes (CNTs) have been in limelight of extensive research [44–46] due to their impressive material and structural properties, which can be exploited in various manner including smart sensing applications as detailed in *section 1.3*. With their sensing potentials in mind, CNTs became the choice of nanomaterial in our research.

CNTs need to be integrated in a microsystem for utilizing their sensing capabilities. Apart from being a platform for the CNTs and a bridge to the macroscopic world, a microsystem can contribute by providing electrical signal across the CNTs and process the acquired signal variations from these sensing nanomaterials to realize a smart system integration. A microelectromechanical system (MEMS) is a typical choice for micro and nanoscale integration due to its flexible fabrication process and material choice. However, a low-cost compact system with integrated circuits (ICs) for on-chip signal processing is important to commercially manufacture CNT-based sensors [47–49]. Such a microsystem platform can be provided by complementary metal—oxide—semiconductor (CMOS) technology, where the sensors will also benefit from short interconnects, less parasitic elements, low power consumption and better signal to noise ratio (SNR) with the built-in electronics [49–51]. Therefore, an attractive but challenging approach is directly integrating CNTs into CMOS. Potential integration methods and involved challenges are discussed in section 1.4.

There has been substantial amount of work on CNTs to explore its potential as a sensing material, but commercial CNT-based sensors are still not available [52]. It is mainly due to the absence of a standard process for integrating CNTs in a low-cost industrial CMOS technology with minimum modifications to the foundry fabrication process. Different literatures demonstrated CMOS-compatible integration process through MEMS implementations or extensive CMOS post-processing, which are not easily transferrable to current inexpensive CMOS technologies. Economical sensors with low-power and portability have many commercial applications, especially in this era of networked technologies that induces an increasing demand of sensors for the internet of things (IoT) [53]. This work aims to pave the way for realizing CNT-based commercial sensors.

### 1.3 Carbon Nanotubes

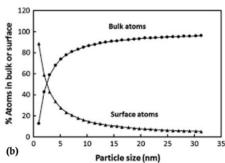

Carbon nanotubes are an allotrope of carbon, similar to the other carbon forms such as diamond, graphite, amorphous carbon and fullerenes. Based on the bonding formation of the atoms in carbon lattices, properties of these allotropes vary. For example, diamond is a very hard, electrically non-conductive, brittle material with the ability of light dispersion, which makes it useful in industrial applications such as cutting and drilling, while also commonly being used as jewellery mostly owing to its latter property. In contrast, graphite is soft and conductive (both electrically & thermally), thus utilized as pencil leads and electrodes due to the respective properties. A single atomic layer of graphite is known as graphene, properties of which [54–56] vastly varies from its bulk form. CNTs can be visualized as a two-dimensional (2D) rolled-up graphene sheet into a 1D cylindrical or tube shape as illustrated in *Figure 1.3*.

Figure 1.3: Schematics of graphene sheet, SWCNT and MWCNT. Adapted from [57].

#### 1.3.1 Classifications

CNTs with one graphene sheet or wall is called single-walled carbon nanotube (SWCNT), while CNTs consisting multiple concentric layers of graphene sheets or walls are referred as multi-walled carbon nanotube (SWCNT). Sumio lijima discovered MWCNTs in 1991 [58] and SWCNTs in 1993 [59]. MWCNTs can be as thin as 4-5 nm [60] and as long as 65 cm [61], resulting in extremely high aspect ratio. Each layer of MWCNTs can be considered as a SWCNT. MWCNTs will show metallic behaviour if one of its layers is

metallic [62–64]. In majority of the cases, MWCNTs show metallic characteristics [65,66], even if the individual SWCNT layers of a double-walled CNTs (DWCNTs) are semiconducting [66–68]. It has also been reported that metallic MWCNTs can be converted to semiconducting MWCNTs [69]. Rolling up a graphene sheet in a certain angles and curvatures is known as chirality of the CNTs, which has a significant impact on the properties of this nanomaterial [70–73]. SWCNTs can have either semiconducting or metallic behaviour based on their chirality [74–76].

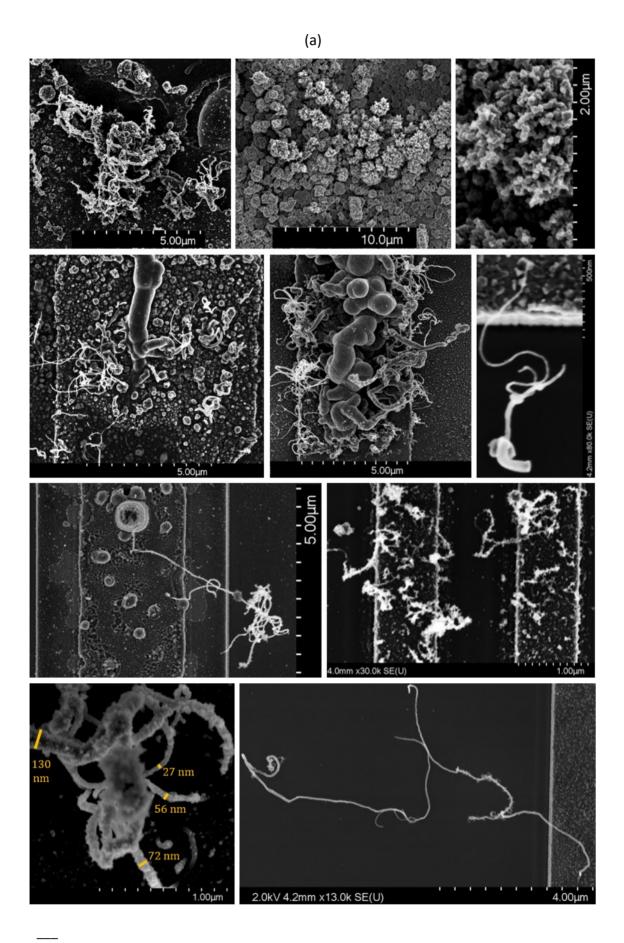

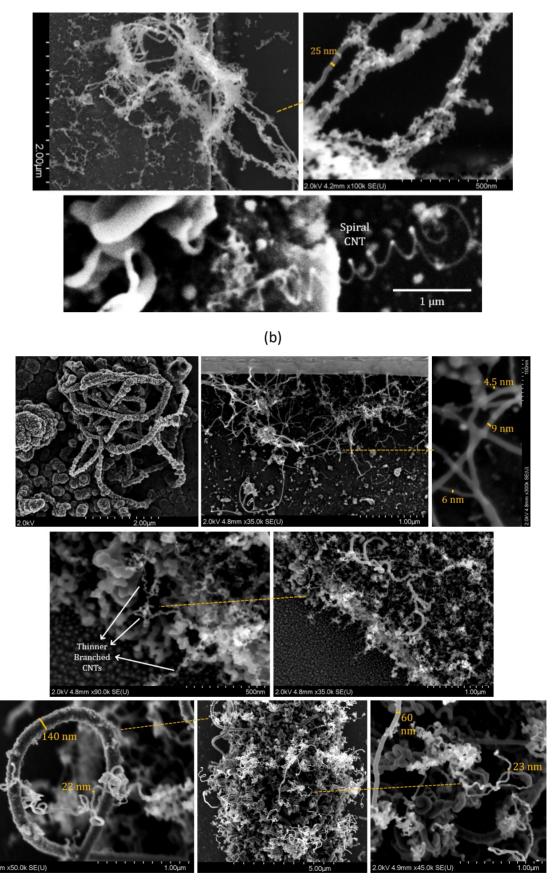

CNTs often have structural disorders and form various types of defects such as voids, branching, bamboo-like structures, flakes [77–79]. These defects can influence the properties of the CNTs [78–83], which may also be useful in some applications [84–87]. Carbon nanofibers are another form of defective structures, which are often larger in diameter and unlike CNTs, their graphene layers are not concentric [88]. CNTs have improved structural orders with less defects at high temperatures [89–91]. Quality of the CNTs can be relatively determined through transmission electron microscopy (TEM) and Raman spectroscopy [90,91]. Since our process does not rely on a specific structure or chirality of the CNTs, these analyses were not considered for characterization.

### 1.3.2 Properties and applications

CNTs have earned their place as one of most researched nanomaterials [7,44–46,92] due to their extraordinary structural [93], electrical [94], electronic [95], optical [96], chemical [97], thermal [98], and mechanical [99] properties which can be exploited through a numerous range of applications in various fields of nanotechnology. CNTs can be 50,000 times thinner than average human hair, while being more than 100 times stronger than steel. One-dimensional structure of the CNTs enable them to have high aspect ratio. CNTs with their large surface area in proportion to the volume ensures enhanced chemical reactivity to certain gases while having good thermodynamic stability [100–102], which makes them an excellent sensing material. Metallic CNTs can withstand very high current density (> 10<sup>9</sup> A/cm²) [103,104] which is ~3 orders of magnitude higher than the capacity of copper, while their room temperature thermal conductivity of 3500 W/m-K [105] is near 10 times higher than that of copper. Thus,

CNTs are a potential candidate to replace current interconnecting metals and vias in future IC technology [106]. Semiconducting CNTs with their higher mobility than any known semiconductors [107] hold the promise of succeeding silicon as the transistor channel [108]. CNTs are also ideal absorbers of infrared (IR) radiation and show enhanced photoresponse in the electrical conductivity of suspended SWCNTs, which is fitting characteristics for a sensitive material in bolometers [109,110].

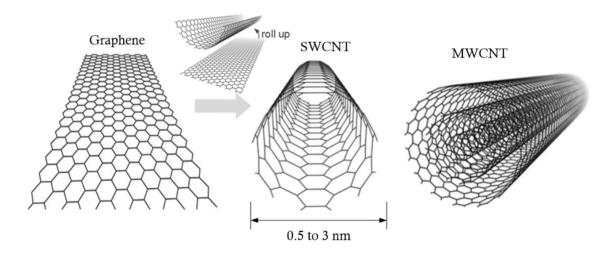

CNTs have been attracting significant interests in different research fields including biomedical [35,111,112], chemical [97,113,114], electronics [53,115,116] and many other innovative technologies [45,52,117,118]. For biomedical applications, CNTs are mainly used in biosensors [119], targeted drug delivery systems [120], cancer diagnosis and therapy [121]. Most typical utilization of CNTs are in chemical fields that includes enormous amount of diverse sensing applications [122–133]. In microelectronics, recent developments of CNT field effect transistors (CNTFETs) [108,134–136] show promise to realize beyond-silicon integrated circuits. Among the other emerging CNT-based applications, water treatment [137] and energy conversion & storage [138] are notable. A few prominent CNT-based applications are presented in *Figure 1.4*.

The inherited properties of CNTs are effectively utilized in gas sensing applications [139–141]. Their large surface-to-volume ratio plays an important role in such applications as more gas molecules can come in contact with the surface of the CNTs, resulting in enhanced reactivity [142]. Moreover, CNTs offer room-temperature operation and the option for functionalization with metal or metal oxide nanoparticles to deliver enhanced sensitivity, selectivity, chemical stability, fast response [143–145] along with the promises of a wireless, low-cost, power efficient system upon CMOS integration [47–49]. There is a high demand for gas sensors of such qualities to utilize them in various domestic and industrial applications such as monitoring air quality of indoor (e.g., CO<sub>2</sub>, H<sub>2</sub>, odor) [146] and outdoor (SO<sub>2</sub>, NO<sub>2</sub>, CO<sub>2</sub>) [147] for health and environmental concerns, detecting quality of perishable food [148], breath analysis through volatile organic compounds for medical diagnosis [149], and detecting pesticides and pathogens in agricultural production [97].

**Figure 1.4:** An overview of CNT-based applications. (a) A 46 g light-emitting diode lit and suspended by two 24 μm-thick CNT fibers [150]. (b) CNTFET schematic with source/drain contacts and SiO<sub>2</sub> dielectric [151]. (c) Conceptual illustration of a CNT-based gas sensor implanted directly into a MEMS/CMOS chip with RF circuitry [152]. (d) Diagram of a SWCNT network suspended between two electrodes in an IR bolometric detector [110]. (e) Current mapping for the pressure sensing word "CNT" made by PDMS [153]. (f) Visual representation of a DNA detection scheme with CNT network [97]. (g) Illustration of folic acid-targeted cytosensing strategy for an enhanced electrochemical detection of cancer cells [119].

### 1.3.3 Synthesis methods

Arc-discharge [154], laser ablation [155] and chemical vapor deposition (CVD) [156] are the primary synthesis methods for CNTs. Among others, spray pyrolysis (modified CVD) [157] and gas-phase flame synthesis [158] methods are notable. CNTs were discovered by arc-discharge method. This method as well as laser ablation method need high temperatures, extensive processing for purification and sorting, which makes this low-throughput method very expensive for mass production. Moreover, these methods lack control over CNT characteristics and growth location. CVD method is the most preferred CNT synthesis method for high volume production as it does not have the limitations of the previous methods. CVD is also compatible with microfabrication process as it allows direct CNT growth on preferred substrates with certain control over the characteristics (e.g., structure, diameter, orientation) of the CNTs at relatively lower temperatures.

Thermal CVD is the most conventional CVD method, where CNTs are typically synthesized by thermal decomposition of a hydrocarbon gas on catalyst nanoparticles at 650-900 °C in a wide range of pressures, varying from a few millibars (mbar) to atmospheric pressure. CNTs are also grown at lower temperatures [159] with low pressure CVD (LPCVD), where the process is generally operated below 1 mbar. Another approach to lower the synthesis temperature is by using plasma enhanced CVD (PECVD), where the generated plasma facilitates gas decomposition, however, the incoming energetic ions also damage the synthesized CNTs during the process [160]. Also, overall quality of the resultant CNTs are compromised when they are grown at lower temperatures [161].

### 1.4 CNT integration in microsystems

CNTs require integration with a microsystem to utilize their potential as a sensing material in small and low-cost sensors. To demonstrate a sensing concept or for the performance development of a sensor, CNTs are often integrated in MEMS. However, a commercial smart sensor also demands on-chip integrated circuits for signal processing, which can be fulfilled by the matured and low-cost Si technology, CMOS. Therefore, a standard process for monolithic integration of CNTs and CMOS becomes important.

### 1.4.1 Different integration approaches

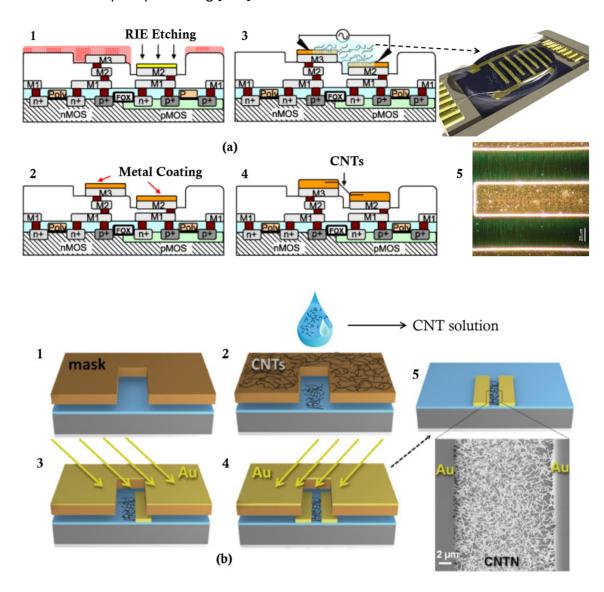

There are various approaches of integrating CNTs in a microsystem. Different methods of integration have their own benefits and challenges. Certain methods can be more suitable than others for specific applications. Therefore, the choice of integration method can depend on the intended application. For microsystem integration, CNTs can be grown separately at high temperatures and then transferred and assembled. The advantage of the post-growth processes is desired chemical modifications of the CNTs before deposition on CMOS at low temperatures. The typical method of transferring CNTs is based on wet process, where the two most used techniques are dielectrophoresis (DEP) [162–165] and solution-based deposition [108,166–168]. Process flow of these techniques are shown in *Figure 1.5*.

Deposited CNTs in these liquid suspension techniques often have poor bonding with the electrodes in addition to the risk of contamination during the extended process steps [169]. They also often suffer from issues related to non-uniform CNT assembly and misalignment [164,170]. Another challenge is to ensure uniform CNT dispersion in the solvent since CNTs tend to bundle together in the solution due strong interaction between them, formed due to van der Waals forces [52], which results in aggregation of the deposited CNTs that may cause system failure [108,171]. In addition, solution-based CNT deposition may require purchasing CNTs, which can be very expensive [172].

In a recent breakthrough on CNTFETs, Hills et al. [108] proposed a manufacturing methodology for CNTs which combines processing and circuit design techniques to overcome the major challenges related to liquid deposition methods for CNT integration in CMOS. However, the complex nature of this work on CNFET-based digital circuits requires defining a dedicated CMOS fabrication process involving materials such as Pt for metal contacts and  $HfO_x$  for passivation layers [108], which are not common in standard low-cost bulk CMOS processes. In the case of the DEP process, it provides better alignment and uniformity, but usually has low throughput and requires complex metallization processes to establish good contact between the CNTs and the electrodes [49]. Seichepine et al. [164] developed CNT integration in CMOS by DEP method with

high yield, where 80% of the electrode pairs in the 1024 array of devices only have 1–5 CNT connections per electrode pair; however, these CMOS chips still required extensive metallization post-processing [173].

**Figure 1.5:** Liquid deposition methods. (a) A typical dielectrophoresis (DEP) process: (1) RIE etching to remove passivation layer on CMOS die, (2) electroless zincation process to remove aluminium oxide and to form a thin metal layer on top of the electrodes, (3) dielectrophoretic assembly to incorporate SWNTs onto CMOS circuitry, (4) the second electroless zincation process to improve the contacts between the CNTs and the metal electrodes, (5) deposited CNTs in between electrodes. Adapted from [165,174,175]. (b) A solution-based CNT deposition process: (1) application of a single shadow mask, (2) deposition by immersion in a solution containing dispersed CNTs, (3) & (4) defining source and drain electrodes by adjusting the metal deposition angle, (5) fabricated bottom-gate of CNT transistor and scanning electron micrograph of the CNT channel. Adapted from [169].

Another approach for CNT integration in a microsystem is by local CNT synthesis on desired microstructures. In this method, CNTs are grown by CVD process where only the growth region is heated. This process does not have the limitations of the wet deposition methods and ensures good structural quality of the synthesized CNTs, but the high growth temperature is the main restriction to obtain CMOS-compatibility in this process. And that is what we aim to solve in our approach of CMOS-CNT integration.

#### 1.4.2 Local CNT synthesis on microstructures

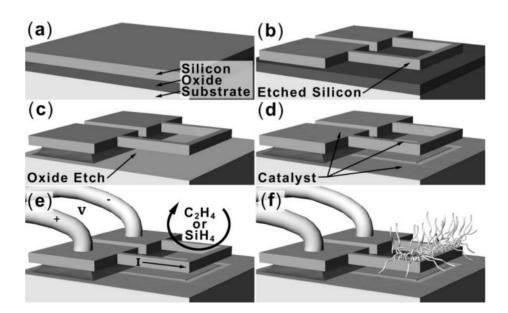

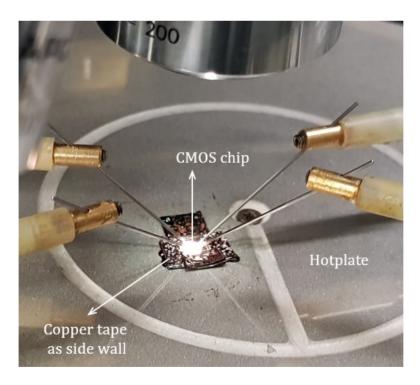

CVD is the best approach for local CNT growth on microstructures, where only the microstructure is heated while the CVD chamber remains at room temperature. CNTs were directly synthesized on MEMS structures back in 2003 [176]. A process flow for locally growing CNTs on microstructures is presented in *Figure 1.6*. In this process, the fabricated microstructure (or microheater) is locally heated by joule heating to generate temperatures in the region of 650-900 °C. A pre-deposited thin catalyst layer (such as Fe, Ni, Co) on the microheater breaks into nanoparticles at such high temperatures, while a carbon-containing precursor gas enters the CVD chamber. CNTs start to grow on the microheater when the precursor gas interacts with the catalyst nanoparticles.

**Figure 1.6:** Process flow for CNT growth on MEMS. (a) Layers of wafer, (b) microstructure layer patterning and etching, (c) sacrificial oxide layer etching, (d) maskless catalyst deposition, (e) wire bonding on contact pads and joule heating in relevant gaseous ambient, (f) resulting carbon nanotubes. Adapted from [176].

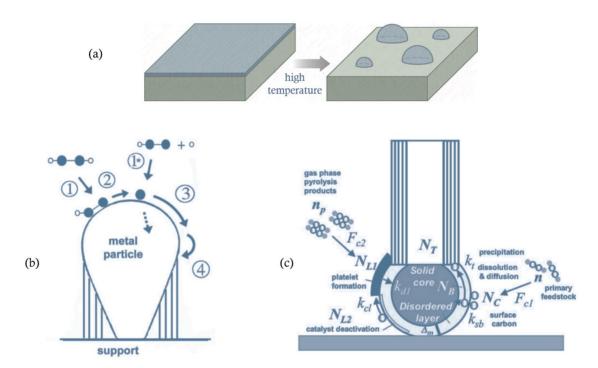

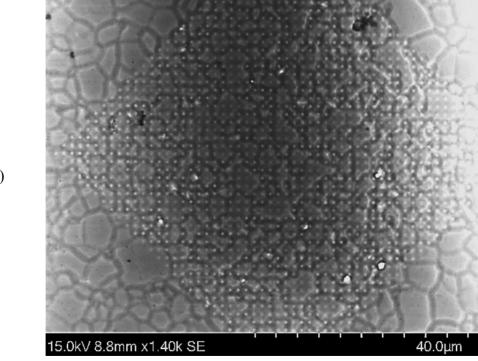

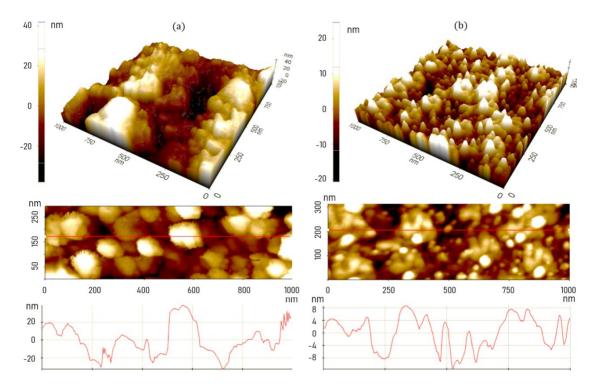

In the CVD growth process, a catalyst is essential as CNT growth takes place on catalyst nanoparticles, the size of which mostly defines the diameter of the synthesized CNTs [177,178]. The catalyst can be deposited as a thin film, which breaks into nanoparticles on top of the microheater when local heat is applied. The deposited thin films are metastable and will spontaneously dewet (or agglomerate) to form small islands when heated at certain high temperatures (*Figure 1.7a*) due to surface energy minimization [179]. As the thickness of the film decreases, lower temperature is need for dewetting due to the acceleration in dewetting rate with reduction in film thickness [179], hence catalyst layer thickness can also impact diameter of the CNTs. Preformed catalyst nanoparticles can also be deposited to grow CNTs [180], but the process can be costly.

Figure 1.7: Dewetting of catalyst layer and CNT growth mechanisms. (a) Small island formation due to dewetting of thin film at high temperatures [179]. (b) Schematic of CNT tip-growth process: (1) adsorption of the gas precursor molecule on the catalyst surface, (2) dissociation of the precursor molecule, (3) diffusion of the carbon atoms in or on the catalyst particle, and (4) nucleation and incorporation of carbon into the growing structure [181]. (c) Schematic of a more complex mechanism of CNT base-growth process, explained in [182].

Apart from transforming catalyst thin film to nanoparticles, high temperature on the microheaters is required to provide essential thermal energy for the dissociation of

hydrocarbon gas molecules and the nucleation & growth of CNTs. Acetylene ( $C_2H_2$ ) and ethylene ( $C_2H_4$ ) are the most common carbon-containing precursor gas used for CNT synthesis in thermal CVD. The synthesis process starts with thermal decomposition of the precursor gas when the catalyst nanoparticles adsorb the gas molecules. The catalyst nanoparticles are the nucleation sites where carbon atoms diffuse and CNTs begin to grow with the thermal energy locally provided by the microheater. Typical activation energy for CNT nucleation in thermal CVD with  $C_2H_2$  as precursor gas is 1.2–1.5 eV, although a significantly lower value of 0.9 eV is recently reported [183]. CNTs can nucleate and grow either from below (tip-growth) or above (base-growth) the catalyst nanoparticles depending on the interaction between the catalyst and the support layer [184]. Both CNT growth mechanisms are illustrated in *Figure 1.7b* and *1.7c*.

The growth process can be improved with inclusion of supporting gases such as Ar and H<sub>2</sub>. There are numerous parameters that can affect the CNT synthesis process, which contributes to the fact that the underlying mechanisms of CNT growth are extremely complex and still not completely understood [184,185]. Catalyst material, support layer material, precursor gas, supporting gas, etching gas, concentration or mixing ratio of the gases, flow rates, temperature of growth location, thermal profile, annealing, pretreatment of the catalyst layer, reactor type, process duration are the notable parameters that influence the CNT diameter, chirality, properties, quality, *etc*. Further details on some of these parameters are discussed in *chapter 5*.

### 1.4.3 Challenges of direct CNT growth on CMOS

Monolithic integration can be achieved if CNTs are directly synthesized on CMOS chips. However, a CMOS-compatible CNT synthesis process is very challenging. The major obstacles are limited material options, temperature restrictions, and microfabrication inflexibility in a standard CMOS process. In an industrial low-cost CMOS process, the material choices are often limited to silicon, silicon dioxide, silicon nitride, polysilicon, and metal interconnect layers such as Al or Cu; the conductive layer needed for localized heating is only provided by polysilicon and the metallization layers apart from the bulk silicon substrate. Thickness of these layers are also fixed for a certain CMOS technology;

hence, the sheet resistance of the polysilicon layers is already defined by the doping levels used in that process. Temperature limitations in CMOS is a major issue for directly growing CNTs, where the electronics cannot sustain temperatures above 300-400 °C for prolonged duration [186–188]. High temperature exposure may result in dopant rediffusion in the active transistor regions and can cause electromigration in aluminium interconnects [189], triggering reliability issues and possible failure in the CMOS device. Growing CNTs (or nanomaterials in general) on chip at 650-900 °C, while keeping post-processing CMOS temperatures below 300 °C is very challenging [47,48,190]. In a dedicated MEMS process, microheaters can be thermally isolated by fabricating fully suspended heaters. However, fabrication processes in CMOS are stricter, where the process steps should not include any harsh chemicals or environment to keep the electronic interface safe. The challenges are further highlighted in [47,48,190].

CNTs have also been synthesized at low temperatures, mostly using PECVD and LPCVD methods [159,161,191]. However, reduction in temperature also lowers the CNT quality, growth rate and yield [161,190,191]. SWCNT growth is more challenging than MWCNTs at reduced temperatures [161]. A process development to overcome the limitations for low-temperature CNT growth is certainly an option for CMOS integration. For high temperature CNT synthesis, the local resistive heating method discussed in *section 1.4.2* is an excellent option, which is more suited for MEMS structures. Therefore, in our approach of monolithic CMOS-CNT integration, we aim to adapt the MEMS techniques by fabricating CMOS-MEMS microheaters, where CNT synthesis temperatures can be isolated to the local growth region.

### 1.4.4 CMOS-MEMS micromachined systems

There are numerous approaches of integrating MEMS and CMOS, which can mainly be classified into hybrid multi-chip and system-on-chip (SoC) integration solutions [192]. Hybrid multi-chip integration approach such as system-in-package (SiP) refers to the process where MEMS & CMOS chips are manufactured separately in their dedicated processes before the heterogeneous integration. In SiP, CNTs can be synthesized on MEMS chips and vertically stack them on chips containing ASICs to avoid direct CNT

growth on CMOS. However, additional time and cost for independent manufacturing of MEMS and CMOS chips together with their separate testing and hybrid packaging will cause hindrance for the commercial production of economically viable sensors. MEMS and CMOS structures are fabricated on the same substrate in SoC integration processes. SoC solutions are compact in size, cost-effective due to possible wafer-level packaging with low testing costs and provide high integration densities; however, the fabrication processes of these techniques can be challenging because of high complexity and low flexibility [192]. Considering the mentioned benefits and drawbacks of the integration approaches, SoC solution was preferred over SiP for our application.

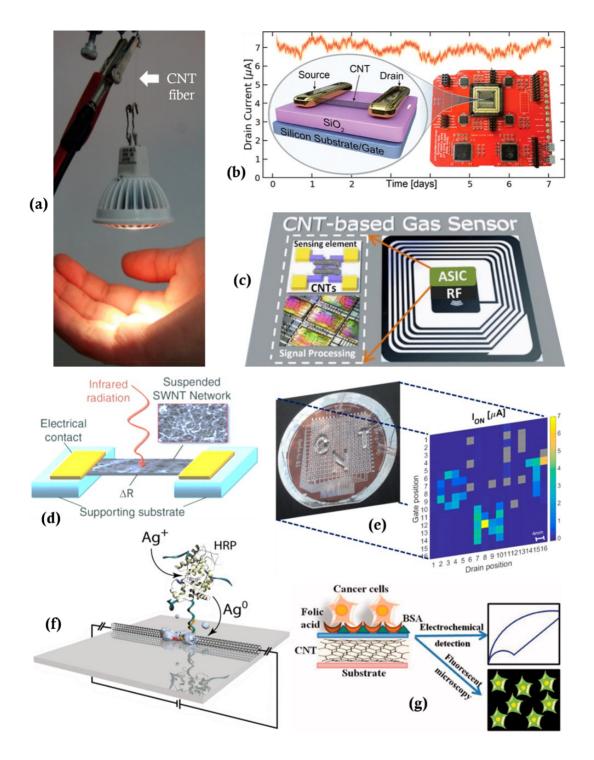

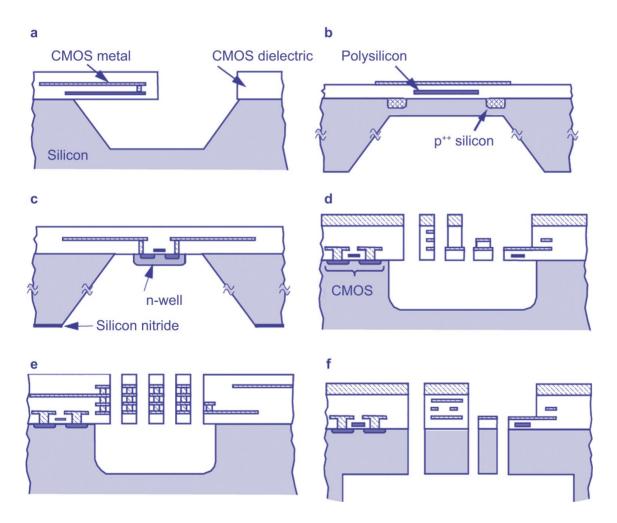

**Figure 1.8:** Various approaches of realizing CMOS-MEMS micromachined systems. (a) Frontside wet etching, (b) backside wet etching, (c) backside wet etching using an electrochemical etch stop, (d) frontside dry etching using a metal hard CMOS mask, (e) frontside dry etching using a photoresist mask, (f) front-and backside anisotropic deep-reactive ion etching (DRIE) [192].

Among the SoC solutions, monolithic integration of CMOS MEMS can be classified into pre-CMOS, intra-CMOS and post-CMOS approaches based on the formation order of the MEMS structures [193]. The latter approach is also known as CMOS-MEMS and has advantages over the other two approaches based on CMOS-compatibility, manufacturing costs and flexibility in design due to the convenience of choosing appropriate CMOS technology and foundry [192,193]. Therefore, we selected the CMOS-MEMS technique to fabricate microheaters in industrially manufactured CMOS chips for local CNT synthesis.

CMOS-MEMS structures are realized by bulk micromachining of an already fabricated IC substrate. Various approaches are used for necessary post-processing of the CMOS as illustrated in *Figure 1.8*. The CMOS-MEMS monolithic integration approaches allow compact chip design with high integration density and improved performance at a low cost. Another important benefit of this technique is that the devices can be implemented by the existing infrastructure of CMOS foundries with the current IC design tools. With the developments of IC and microfabrication technologies, CMOS-MEMS micromachined systems are gaining attention for developing various devices for numerous applications including commercial implementations [194–209]. A range of other recent works with this integration approach have been compiled in [210].

Many challenges can arise during the post-processing of the CMOS chips in the selected SoC CMOS-MEMS integration method, the challenges in our process development have been detailed in *chapter 4*. This integration solution has several mentioned benefits, but the process development takes longer time due to the involved complexity and low flexibility [192]. Although it is common to use bulk etching in this approach (*Figure 1.8*), we avoided that in our process to facilitate a simpler and cost-effective integration with minimum modification of an already operational CMOS foundry process flow.

### 1.4.5 Direct CMOS-CNT integration for sensing applications

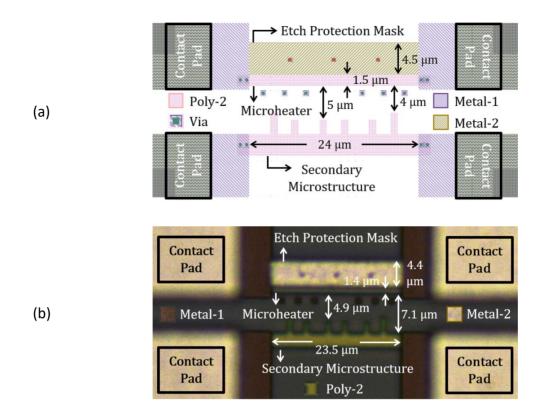

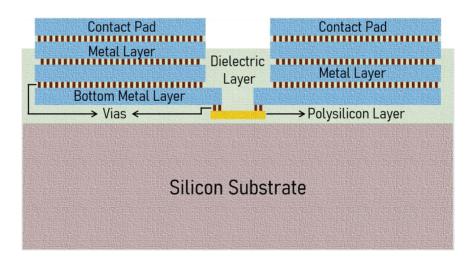

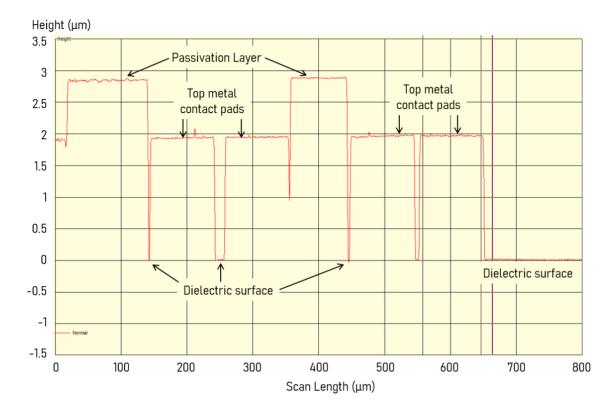

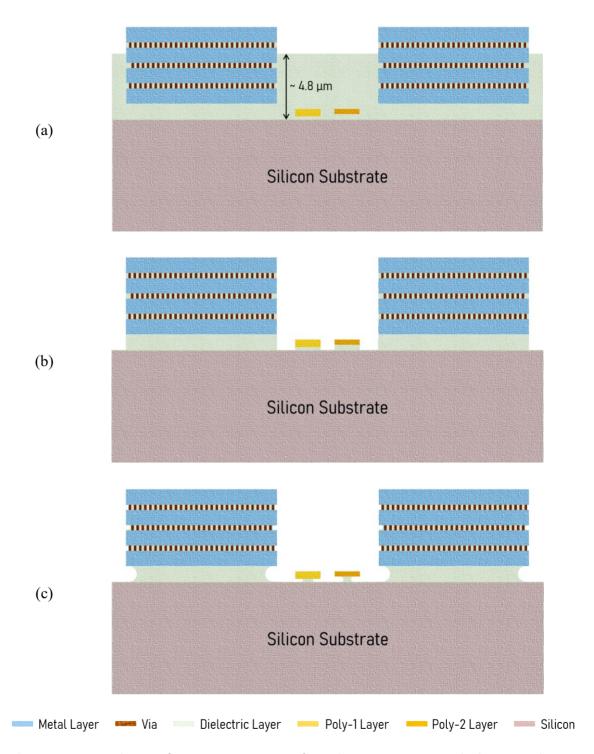

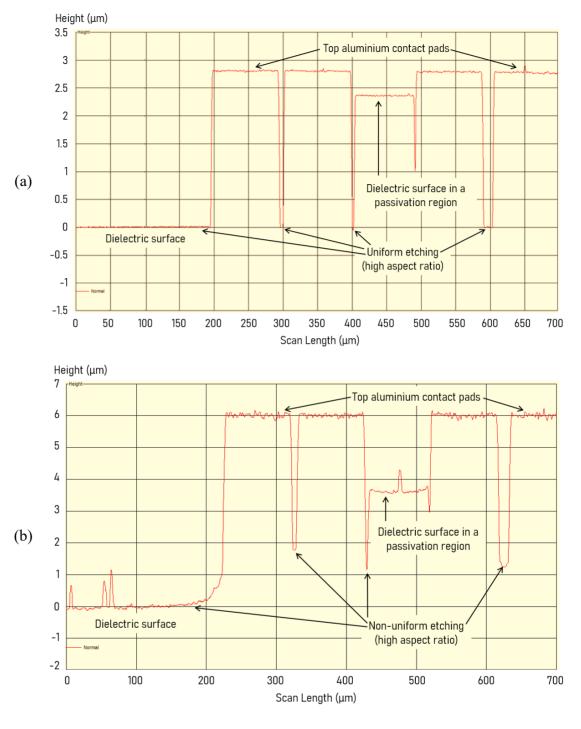

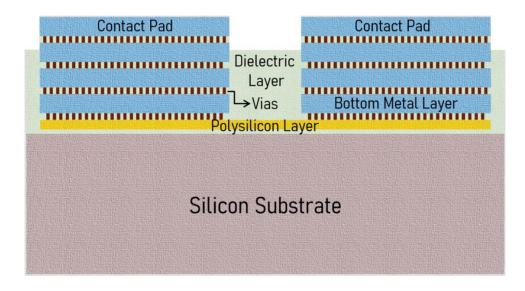

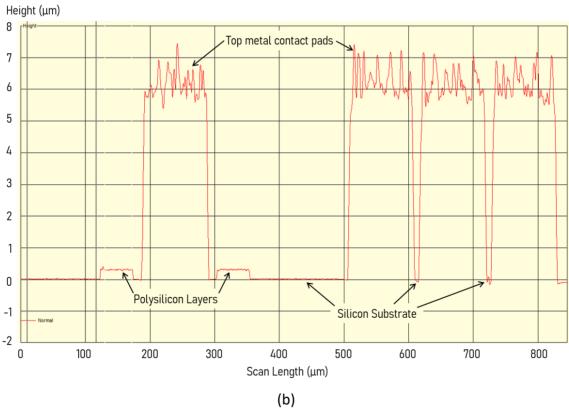

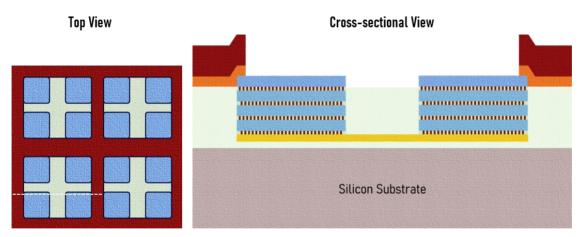

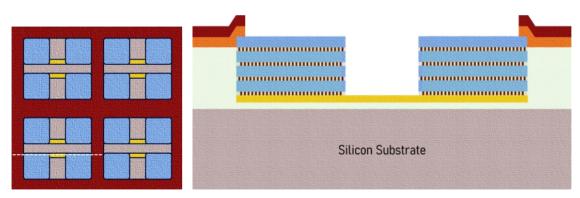

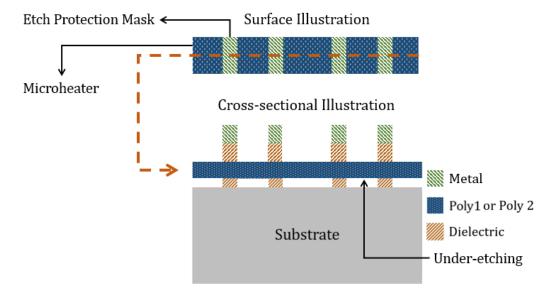

A standard CMOS chip has polysilicon layers for constructing gates of the transistors and metal layers for routing electrical signals. Both of these layers can be used as heaters. However, based on the material properties suitable for efficient resistive heating along

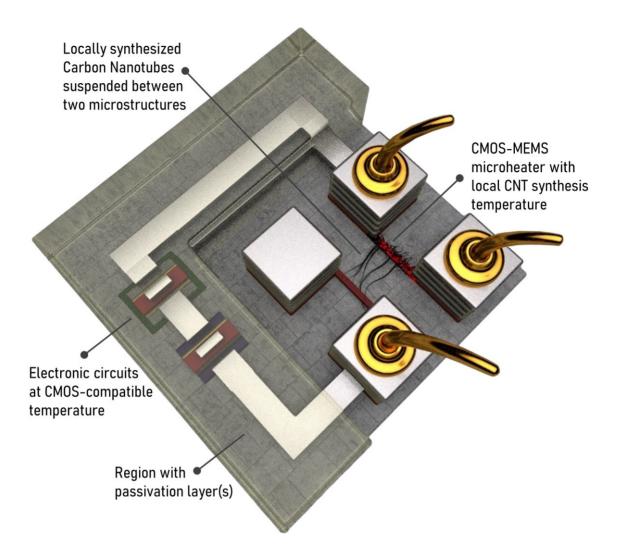

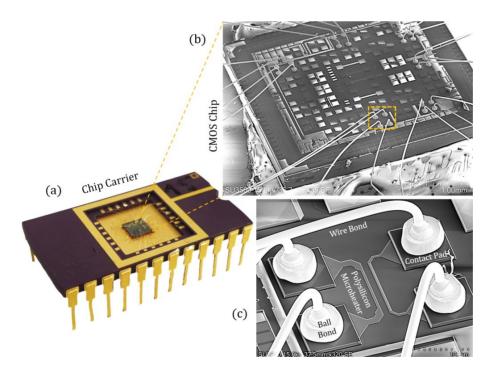

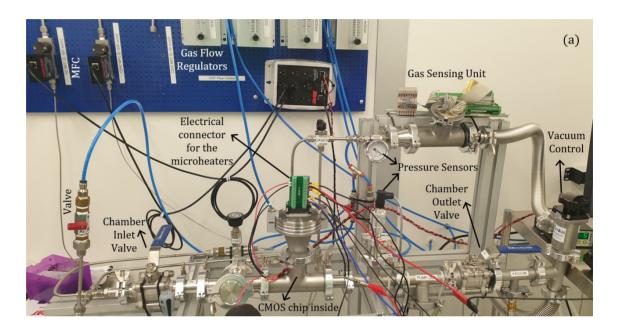

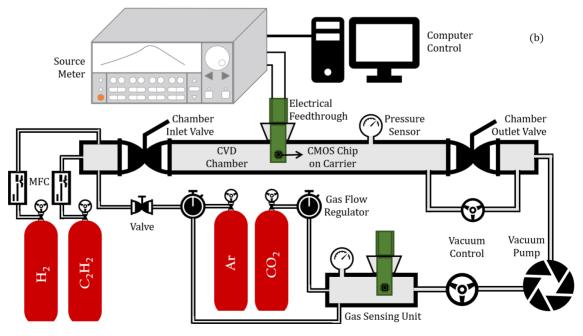

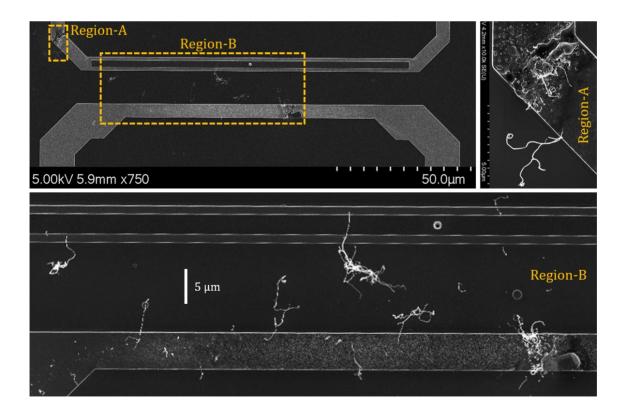

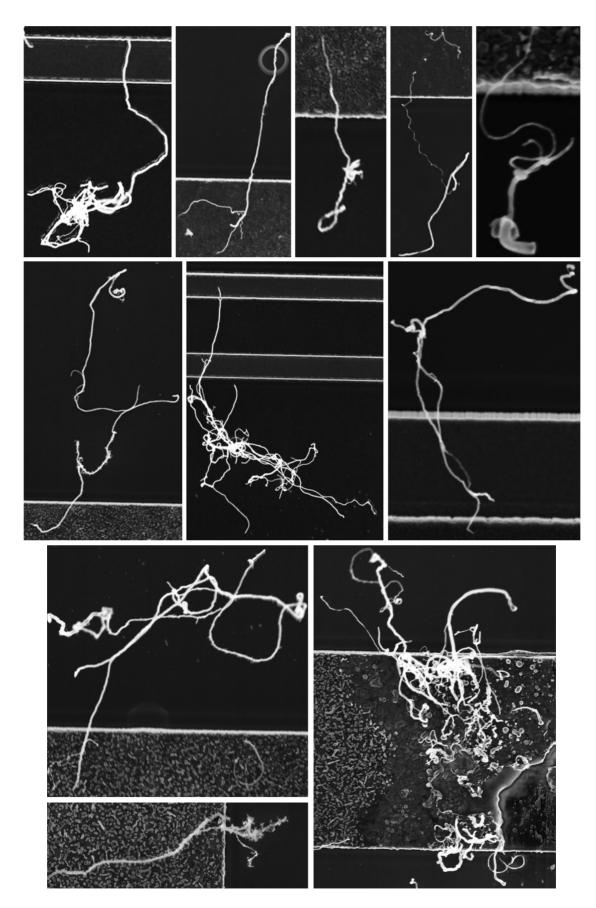

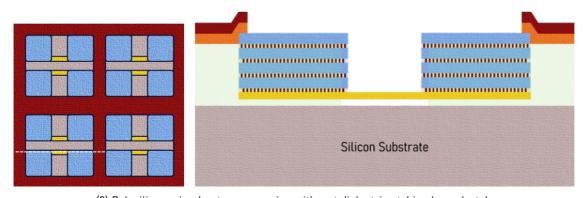

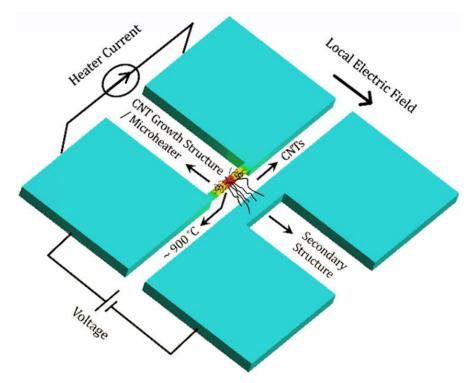

with the temperature requirements in CNT synthesis, polysilicon is the better material option for the CMOS-MEMS microheater as detailed in *section 2.2*. The polysilicon layers in CMOS are covered with dielectric and passivation layers, which need to be selectively removed by the subtractive CMOS-MEMS microfabrication approach to make the polysilicon microheaters accessible for growing CNTs over them. The polysilicon CMOS-MEMS heaters may be fully or partially released by under-etching the dielectric layer beneath them. By generating the required high CNT synthesis temperature only at the growth location, low ambient temperature can be achieved. The concept is illustrated in *Figure 1.9*, where the exposed polysilicon microheater is heated through the wire bonded contact pads, while the CMOS circuits stay in a CMOS-compatible region.

CNTs can be locally synthesized on CMOS-MEMS microheater by thermal chemical vapor deposition (CVD) process, where the chamber remains at room temperature. During the CNT growth process, a local electric field can be generated between the growth structure and an adjacent microstructure to guide some synthesized CNTs towards that second microstructure for establishing connections [211]. A statistical analysis shows CNTs with small diameter (< 10 nm) are influenced more by the electric field [212]. Therefore, higher electric field between the microheater and the secondary electrode can influence the horizontal CNT growth to obtain more CNT connections between the electrodes (Figure 1.9). Once the CNTs are connected between the microstructures (or electrodes), a polysilicon-CNT-polysilicon network is formed, thus implementing a monolithic CMOS-CNT integration. The resistance of the connected CNTs can be monitored through the already bonded electrical wires on the contact pads of the electrodes. This configuration can be used for gas sensing due to their change in resistivity upon exposure to various gases. The synthesized CNTs can be functionalized to improve sensitivity and selectivity for target gases, where surface chemistry of the CNTs are influenced by coating them with nanoparticles [143–145]. Different metal (e.g., Pd, Pt, Sn) [213] and metal oxide (e.g., ZnO, TiO<sub>2</sub>, Co<sub>3</sub>O<sub>4</sub>) [214] nanoparticles are the most common functionalization materials, which are typically deposited by thermal evaporation [215] and atomic layer deposition (ALD) [214] for locally grown suspended CNTs to detect various gas molecules [213].

**Figure 1.9:** Concept of local CNT synthesis on CMOS-MEMS microheater at high temperatures with ICs at low ambient temperature.

#### 1.4.6 Towards CNT-based commercial sensors

Extensive amount of work has been done on CNTs by M. S. Dresselhaus (earning her the title "Queen of Carbon") and R. Saito [93,216–218] since its discovery. Due to its newly founded potentials, a group of H. Dai at Stanford University synthesized CNTs on micro catalytic islands by CVD method in 1998 with the vision of integrating them in conventional microstructures [219]. After a few years, another group of H. Dai also synthesized suspended CNTs on microstructures aligned by electric fields in MEMS [211] and a N-type MOS (NMOS) technology [220]. Although the process involved CMOS-incompatible substrate heating in a CVD furnace at near 900 °C, these works were the first to demonstrate monolithic integration of CNT with MEMS and MOS technology. In

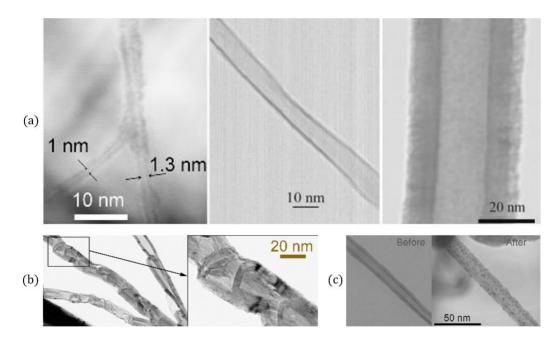

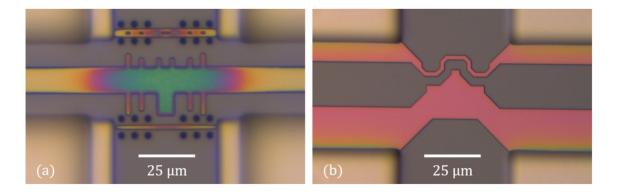

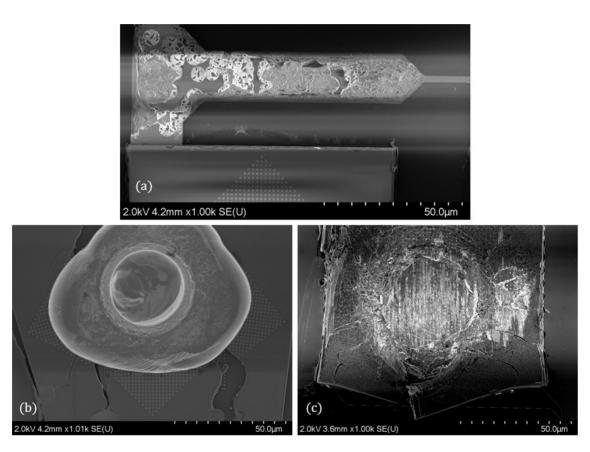

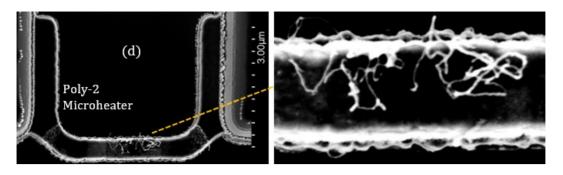

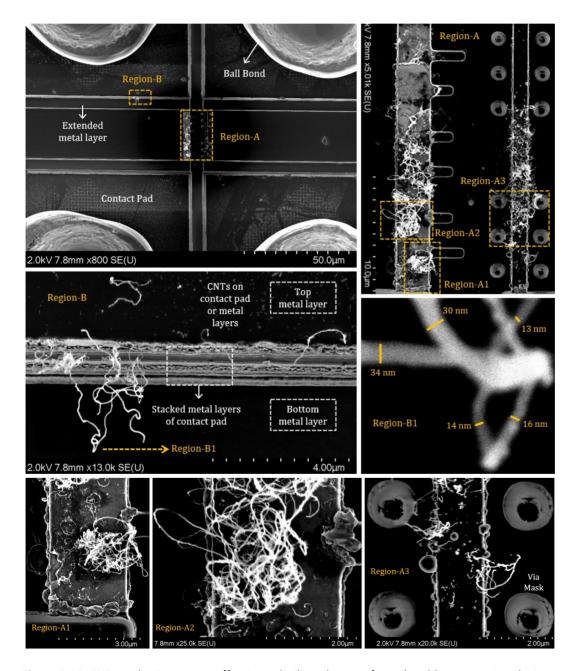

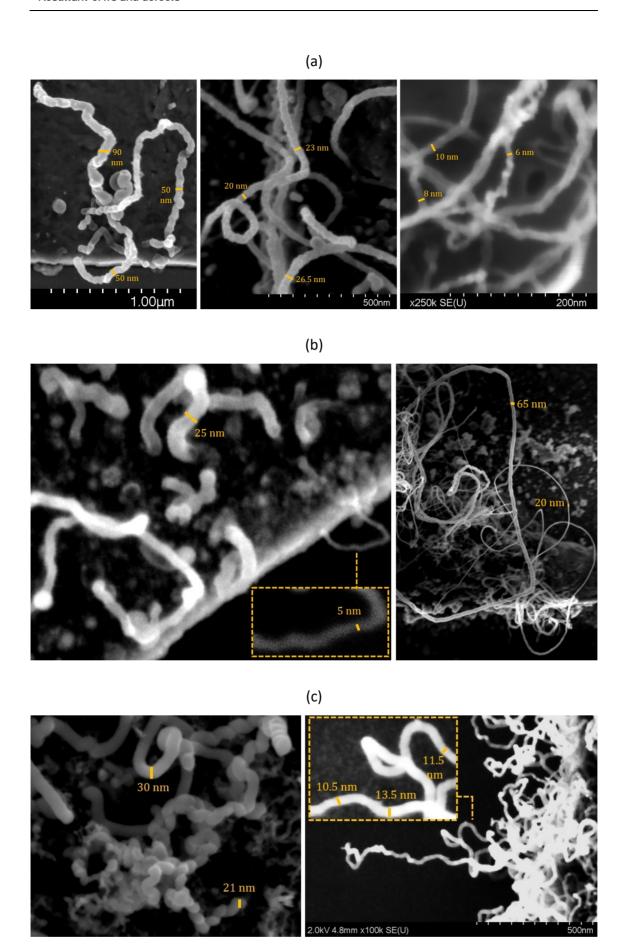

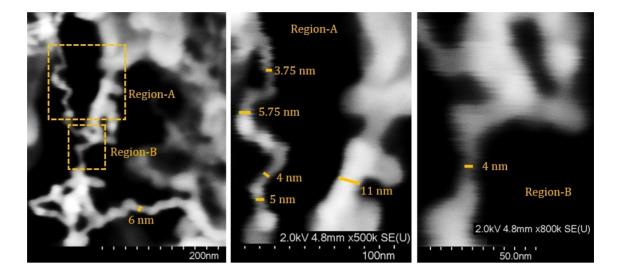

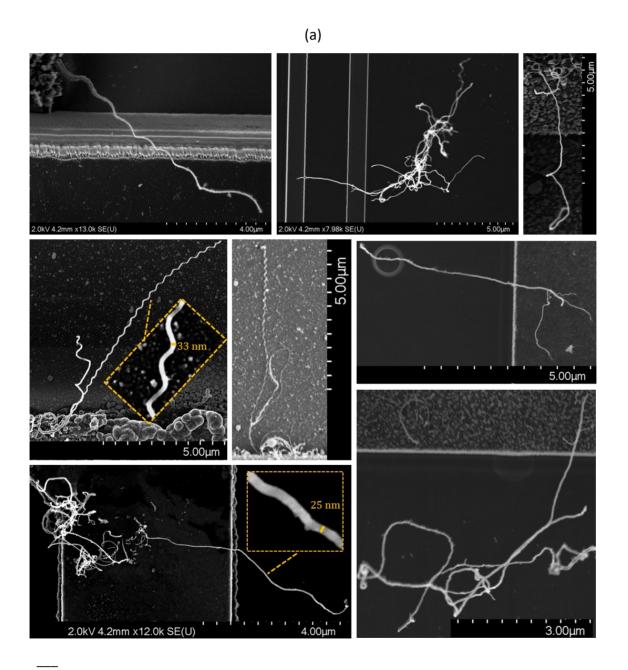

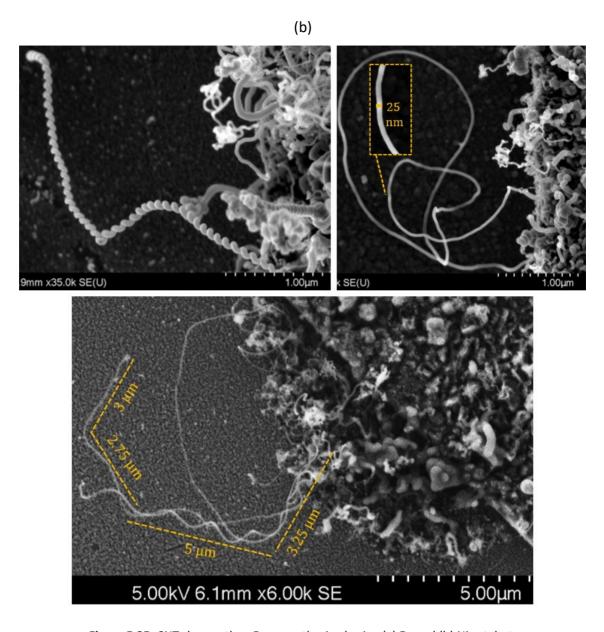

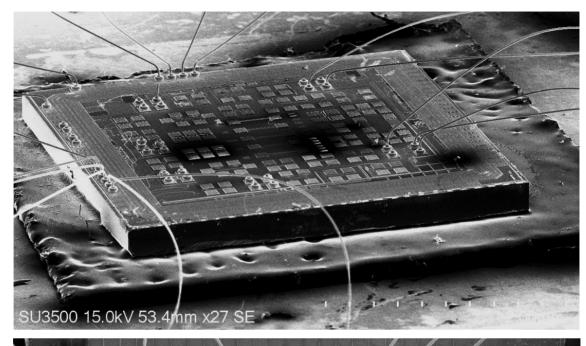

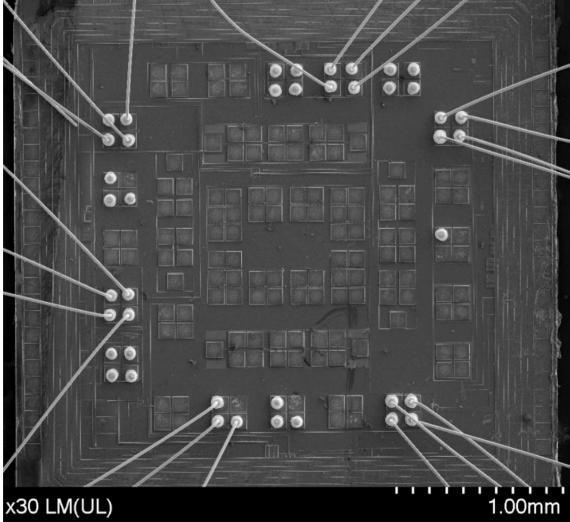

2003, O. Englander, D. Christensen and L. Lin first demonstrated local CNT growth on MEMS structures by resistive heating [176]. E. Campbell's group have been contributing in CNT-related studies since 1999 [221], which involved local CNT growth on MEMS from 2006 by S. Dittmer et al. [222–224], indicating CMOS-compatibility. Another group from ETH Zurich, led by C. Hierold, has significant work related to suspended CNTs on MEMS [225–227]. At the University of South-Eastern Norway (USN), group of K. Aasmundtveit have numerous works on CNT integration in microsystems as summarized in a review, presented in *Article 4*, where B. Ta has contributed in the development of CNT synthesis in MEMS [89,212,228]. Some of these MEMS heaters were fabricated in SOI process, which allowed the design of a hole in the chip for S(T)EM (scanning electron microscopy, in transmission mode) imaging of CNTs as shown in *Figure 1.10*, revealing far more details than more common Secondary Electron SEM imaging.

**Figure 1.10:** High-magnification CNT micrographs with S(T)EM in transmission mode: (a) individual CNTs [89,229], (b) bamboo-like CNTs [89], and (c) a pristine CNT (before) & a decorated CNT with Pd nanoparticles (after) [215].

To the best of the author's knowledge, only two groups have previously shown CMOS-compatible local CNT synthesis on CMOS structures. A group from the University of Cambridge are the first one to grow CNTs in a silicon-on-insulator (SOI) CMOS technology with tungsten microheaters as presented by F. Udrea et al. [230], which was

also the only resistive gas sensing demonstration of a CMOS-based sensor with locally grown CNTs. They also showed spectroscopic gas sensing in CMOS with locally grown CNTs as IR absorption layer [231]. This approach is a very good demonstration of local CNT synthesis for monolithic integration with CMOS, however, it is limited to more expensive SOI CMOS process [232] with tungsten metallization and involves complex bulk micromachining. The use of a refractory metal like tungsten is beneficial for high temperature CNT growth, but its utilization as interconnects (horizontal) is not common in foundry CMOS processes (especially in mixed-signal ICs) [49,190,233], where aluminium and copper are preferred, mostly due to their low resistivities. Moreover, the process involves selective backside bulk etching through a separate MEMS foundry [234,235], which reduces integration density and restricts the process to SOI CMOS substrates [49,190] beside adding cost and complexity. SOI CMOS process limits the scope for manufacturing low-cost CNT-based sensors, which is more desirable in an affordable bulk CMOS process.

H. Xie's group at University of Florida were the only one to locally grow CNTs on polysilicon microheaters, fabricated in a bulk CMOS process [236]. However, it involves various protracted post-CMOS processing steps before growing CNTs. In this approach, top metal layers made of Al were used as etching mask to protect CMOS circuits and the microheaters, which was then required to be etched by RIE. The process also includes two step frontside bulk silicon substrate etching involving both DRIE and RIE technique for anisotropic and isotropic etching to form cavities around microheaters. In addition, wet SiO<sub>2</sub> etching using buffered oxide etchant was performed, which can also etch any newly exposed aluminium layer during this dielectric etching step. Such extensive postprocessing is difficult to accommodate in an already developed CMOS foundry process. Moreover, ICs need contact pads for establishing electrical connections by wire bonding, and these contact pads are made of the exposed metal layers (typically top metal); as the post-processing involves a step of etching the exposed metal layers, the contact pads will also be etched. The process does not use any external mask to pattern and protect the metal exposed layers. In the paper, it is unclear how the transistors were wire bonded (as illustrated in a schematic) for testing after the post-processing steps.

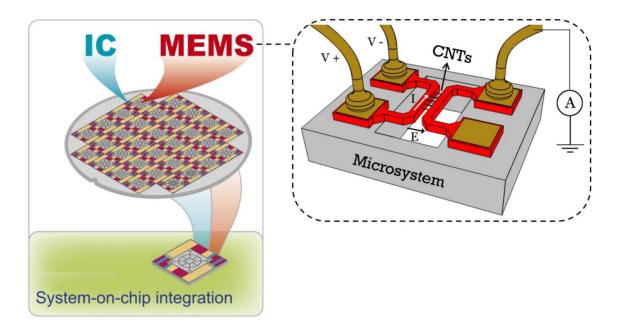

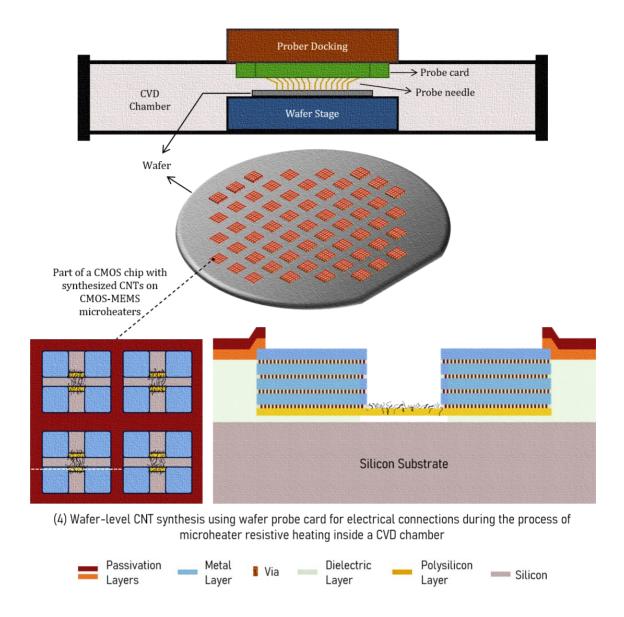

The scope for commercializing CNT-based sensors is high if a standard process can be developed to integrate CNTs with an existing low-cost IC manufacturing process [44,47,48,52,117]. We envision to incorporate the local CNT synthesis process in a low-cost industrial CMOS technology at the wafer-level. The direct CNT integration process would not be viable for mass production if extensive modifications are needed in an already developed foundry CMOS process. Therefore, our goal was to develop a simple post-processing method for fabricating CMOS-MEMS microheaters, where CNTs can be locally synthesized while maintaining low ambient temperature for CMOS-compatibility. The process steps should be compatible for transferring to the wafer-level, where CMOS, MEMS and CNTs are monolithically integrated, as illustrated in *Figure 1.11*.

**Figure 1.11:** A concept for monolithic integration of CMOS, MEMS and CNTs at the wafer-level. Adapted from [192,237].

## 1.5 Research objectives and dissertation outline

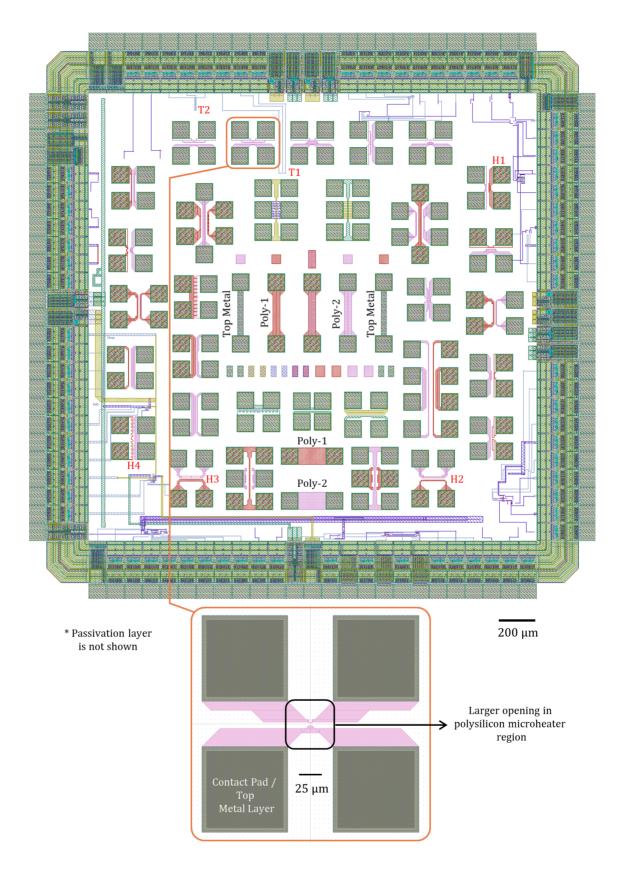

The main goal of this project is to develop a process for locally growing CNTs on a low-cost industrial CMOS technology with the vision of enabling the pathway for commercial production of CNT-based sensors. Based on the objectives, the project can be divided into four significant stages. The first stage of the project involved feasibility analysis for realizing microheaters with CMOS materials that can locally generate up to 900 °C for

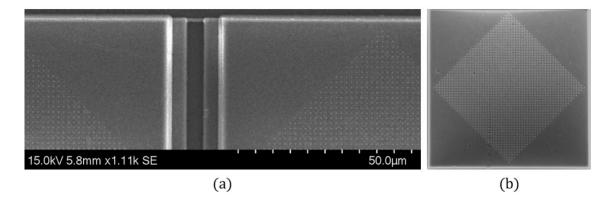

CNT synthesis, while the surrounding chip area remains at temperatures below 300 °C for CMOS-compatibility. It was done by analytical modelling and thermo-mechanical simulations, where suitable microheater dimensions were also analysed. This stage has been discussed in chapter 2. In the second stage, a CMOS chip was designed that contains several metal and polysilicon microheaters with various features to facilitate post-processing and CNT synthesis. The chip was designed in Cadence Virtuoso IC design tool and fabricated in a standard AMS 350 nm CMOS technology; details are presented in chapter 3. Focus of the stage three was realizing the CMOS-MEMS microheaters by necessary post-processing. Developing a suitable method of micromachining CMOS-MEMS heaters for high temperature applications was a crucial part of the project and a key step towards CNT synthesis in CMOS. The post-processing stage was challenging and most time-demanding part of the project, which is typical for SoC integration approaches [192]. An improved second chip was also designed and fabricated to facilitate the post-processing. Details of this stage is summarized in chapter 4, while some selective heaters from the new chip are presented in section 3.3. Fourth stage of the project was to locally grow CNTs on different CMOS-MEMS microheaters by thermal CVD process. The growth process itself was adapted from the earlier work of our group on MEMS-CNT integration (as introduced in section 1.4.6), while preliminary process developments were made for the CMOS-MEMS heaters to grow CNTs at lower temperatures, as discussed in *chapter 5*. As the objective was to directly transfer the developed growth settings for the MEMS heaters to the CMOS heaters without extensive development in growth process, in-depth characterization of the synthesized CNTs were not performed.

Beside the main objectives, CNT-based sensors were realized with the synthesized CNTs to demonstrate sensing applications, primarily for the purpose of gas sensing. To the best of the author's knowledge, this is the first reported demonstration of sensing applications (gas and pressure) with locally grown CNTs on the polysilicon layers of a bulk CMOS technology; results are shown in *chapter 6*. Synthesizing CNTs on CMOS layers is challenging and further developments are needed. The challenges and potential paths of resolving them to move towards wafer-level manufacturing are discussed in

chapter 7. Finally, on-chip temperature sensors are realized with the CMOS layers to estimate surrounding temperature of an active microheater when it is resistively heated to the maximum. Transistors are also characterized before and after operating some non-suspended polysilicon microheaters to CNT synthesis temperature for ensuring CMOS-compatibility. These results are presented in *chapter 8*.

Research contributions are made by publishing several articles on the obtained results. Some articles are in preparation phase, while some others are planned to be written. Significant results from these unpublished articles are also presented in this thesis. A list of the articles is provided in the thesis and the correlation of the articles with the thesis sections are shown in *Table 1.1*.

**Table 1.1:** Correlation between the thesis sections and relevant articles.

| Su | mmary of Thesis Sections                                     | Relevant Articles |

|----|--------------------------------------------------------------|-------------------|

| 2. | Feasibility Analysis for CNT Growth on CMOS                  |                   |

|    | 2.2 CMOS materials for microheater design                    | Article 1 & 2     |

|    | 2.3 Microheater design considerations                        | Article 1 & 5     |

|    | 2.4 Thermo-mechanical analysis of microheaters               | Article 1, 2 & 5  |

| 3. | CMOS Chip Design                                             |                   |

|    | 3.2 Layout and micrographs                                   | Article 2 & 6     |

|    | 3.3 Various microheater features                             | Planned Article   |

|    | 3.4 Microheater characterizations                            | Planned Article   |

|    | 3.5 IR microscopy                                            | Article 2         |

| 4. | Post-processing of CMOS-MEMS Microheaters                    |                   |

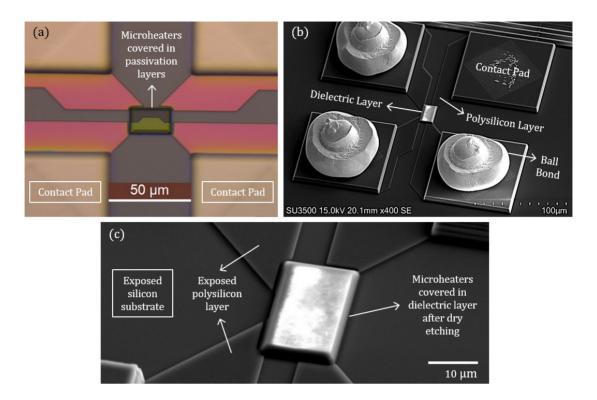

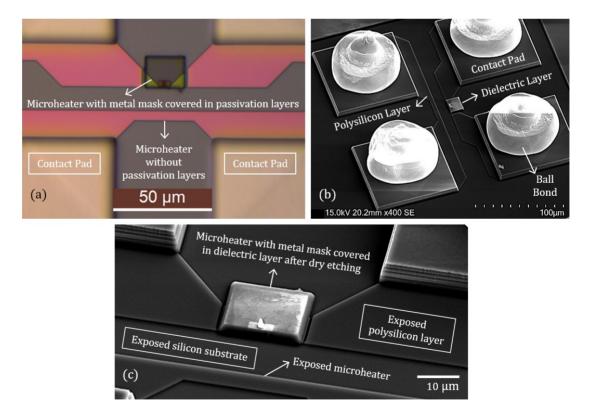

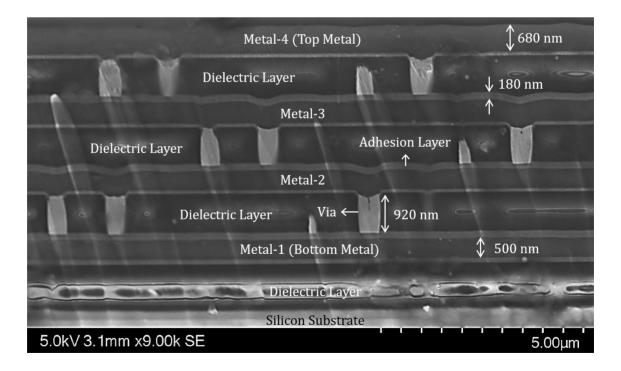

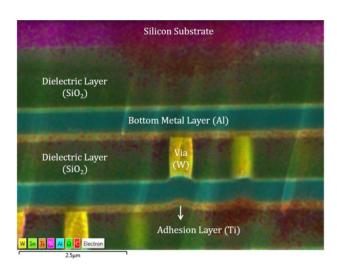

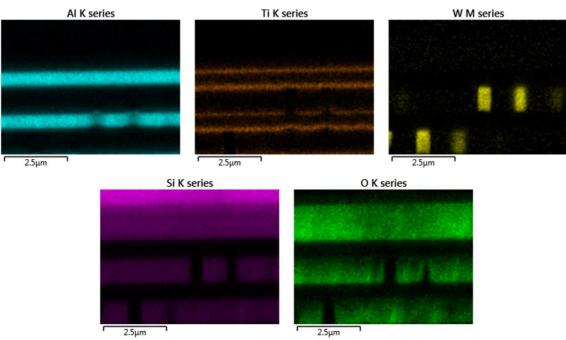

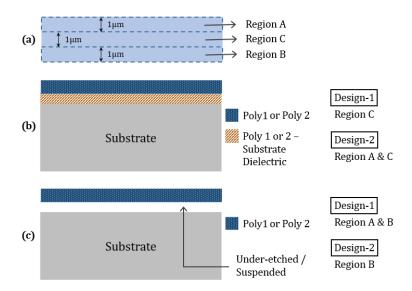

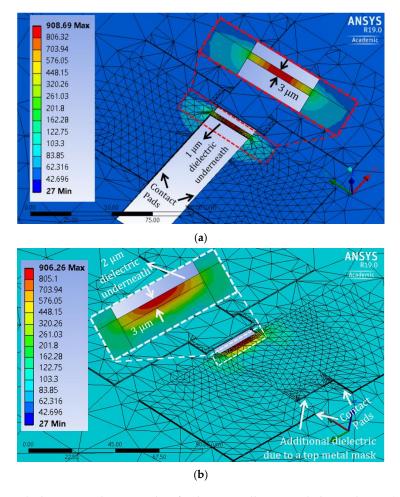

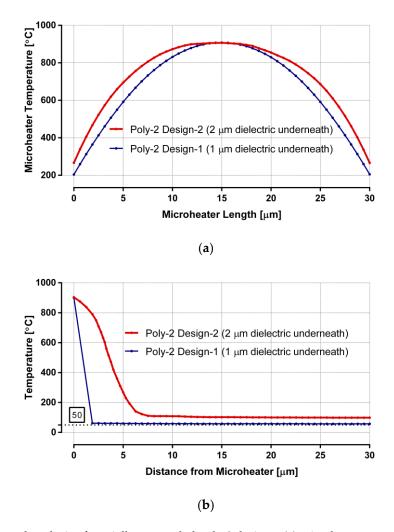

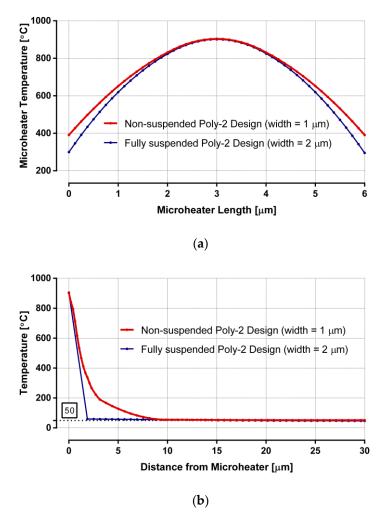

|    | 4.2 Polysilicon microheater design layers                    | Article 3         |

|    | 4.3 Fabrication process of CMOS-MEMS heaters                 | Article 3         |

|    | 4.4 Post-processing challenges and heater design limitations | Article 3         |

|    | 4.5 Improved designs and post-processing                     | Article 3         |

|    | 4.6 RIE recipe development                                    | Article 3 & Planned Articles |

|----|---------------------------------------------------------------|------------------------------|

|    | 4.7 Microheater suspension                                    | Article 3 & Planned Articles |

|    | 4.8 Nickel electroplating on metal heaters                    |                              |

| 5. | CNT Synthesis on CMOS                                         |                              |

|    | 5.2 CNT growth process                                        | Article 3 & 9                |

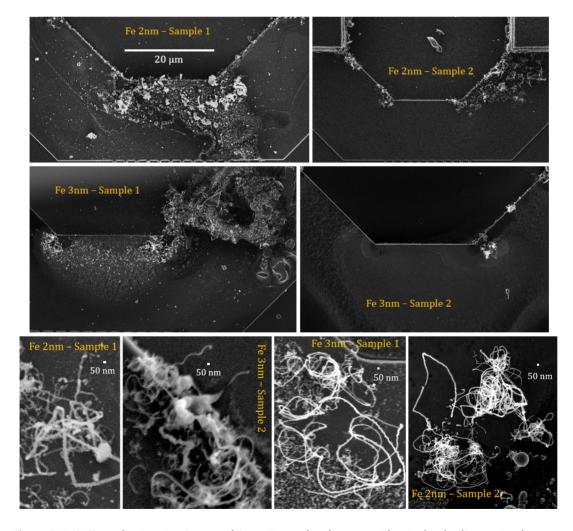

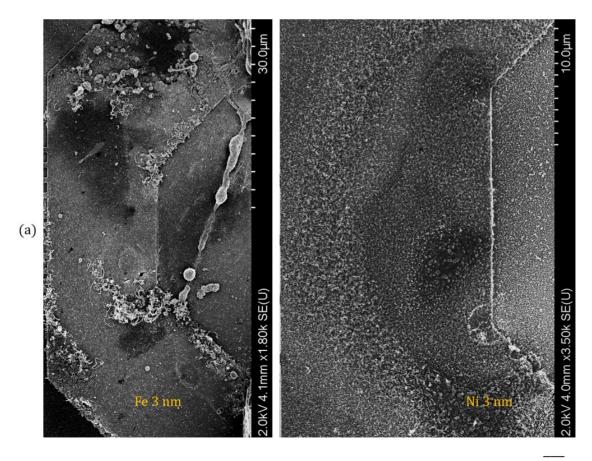

|    | 5.3 Effect of catalysts                                       | Planned Article              |

|    | 5.4 Growth on different polysilicon microheaters              | Planned Article              |

|    | 5.5 Growth on suspended microheaters                          | Planned Article              |

|    | 5.6 Effect of H2 in CNT synthesis                             | Planned Article              |

|    | 5.7 Resultant CNTs and defects                                | Planned Article              |

| 6. | Sensing Applications                                          |                              |

|    | 6.2 CNT growth towards adjacent heater                        | Article 9                    |

|    | 6.3 CNT connections and I-V curves                            | Article 9                    |

|    | 6.4 Gas sensing                                               | Article 9                    |

|    | 6.5 Pressure response                                         | Planned Article              |

| 7. | CMOS Microheater Challenges and Wafer-level Scaling           |                              |

|    | 7.2 Electrical control and temperature limitations            | Planned Article              |

|    | 7.3 Heater damages                                            | Planned Articles             |

|    | 7.4 CNT growth development                                    | Planned Articles             |

|    | 7.5 Towards wafer-level process for mass production           | Planned Article              |

| 8. | On-chip Temperature Sensing & Transistor Characterization     |                              |

|    | 8.2 Characterization of reference microstructures             | Article 7                    |

|    | 8.3 Sensor testing with on-chip microheaters                  | Article 7                    |

|    | 8.4 Effect of convection                                      | Planned Article              |

|    | 8.5 Effect of partially broken microheaters                   | Planned Article              |

|    | 8.6 Effect of CMOS microheaters on transistor characteristics | Article 9                    |

# Chapter 2

# **Feasibility Analysis for CNT Growth on CMOS**

#### 2.1 Introduction

Direct CNT synthesis on CMOS chips are much more challenging than on MEMS. Local CNT growth on a microsystem using CVD technique requires a microheater to generate a hotspot with temperature up to 900 °C. In a dedicated MEMS process, a material with desired properties can be deposited to fabricate the microheater. Furthermore, the microheater can be fully suspended to thermally isolate the heating region. However, this is not the case for CMOS since standard IC fabrication processes are not intended for implementing mechanical structures. In CMOS, the material options are limited, while the typical IC foundry processes do not offer suspension of microstructures. One key requirement in CMOS is the temperature compatibility that indicates the transistor regions should be below 300 °C during any post-CMOS processing. As a result, any microheater that generates high temperatures in CMOS need to ensure high thermal gradient around it for CMOS-compatible ambient temperature. Therefore, it is important to check the feasibility of using CMOS layers as microheaters for high temperature applications like CNT synthesis. Thus, suitable material options in CMOS were investigated, analytical models were made to specify the desired material properties and dimensions of the microheaters, and thermo-mechanical simulations were performed. Results from this chapter are published in Article 1, 2 and 5.

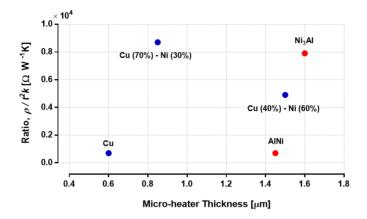

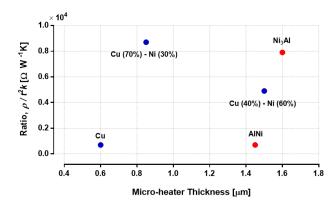

## 2.2 CMOS materials for microheater design

A standard CMOS process offers polysilicon and metal interconnecting layers that can be used to realize microheaters. Aluminium and copper are commonly used for metallization in typical CMOS technologies. These metals, however, are not suitable to serve as microheaters (for CNT growth) in their original form due to low electrical resistivity and high thermal conductivity. Moreover, Al melts at ~660 °C, which is far less

than the required 900 °C CNT synthesis temperature. Therefore, beside the polysilicon option, different binary alloys containing Al or Cu with suitable material properties were investigated.

An analytical model was established to obtain a better perspective of the material properties required for an efficient microheater. According to Fourier's law of thermal conduction, one-dimensional conductive heat transfer  $(Q_x)$  is defined as:

$$Q_x = -kA(\frac{dT}{dx})\tag{1}$$

where k is the thermal conductivity of the material, A is the cross-sectional area (normal to the heat flow direction), and dT/dx is the temperature gradient in the direction of heat flow (along the microheater length in this case). The negative sign indicates that the heat flow is in the opposite direction of the thermal gradient.

The local CNT synthesis temperature was generated by joule heating, where an electrical current is passed through a conductor to produce the heat. Electrical power (P) dissipation for heating a considered length ( $I_x$ ) of the microheater can be expressed as:

$$P = \frac{\rho I^2 l_x}{A} \tag{2}$$

where I is the applied current to the microheater,  $\rho$  is the microheater electrical resistivity, and A is the microheater cross-sectional area.

In this study, only conductive heat transfer was considered, neglecting convection and radiation due their minimal effect in micro scale compared to conduction. The nature of convection can be realized by Rayleigh number (Ra), where higher value of Ra indicates more influence of convective heat transfer, and it was shown that Ra decreases significantly for microscopic structures compared to macroscopic structures; thereby, the effect of convection becomes negligible at the micro level [238]. It was also derived that the heat loss on microstructures due to thermal radiation is less than 1%, even for temperature as high as 1000 °C [238]. Therefore, the dissipated electrical power in

resistive heating can be converted to heat by Fourier's law of heat conduction, and the following expression can be deduced from equation (1) and (2):

$$dT = \frac{\rho I^2 l_x}{kA^2} dx \tag{3}$$

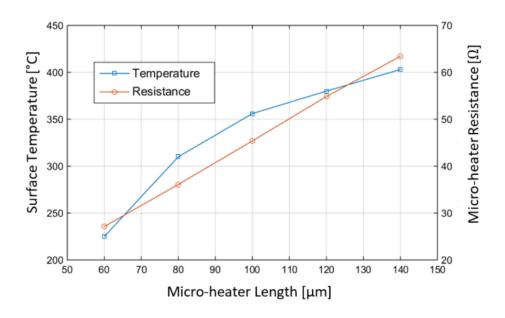

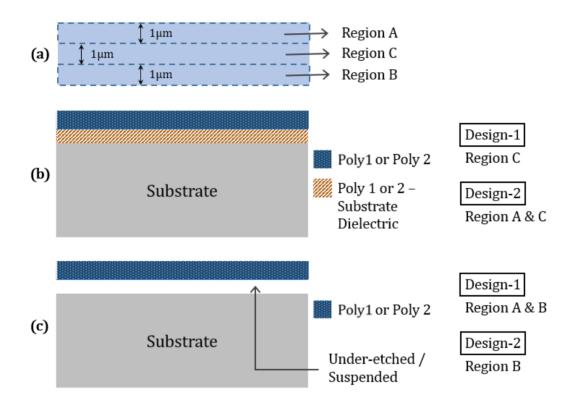

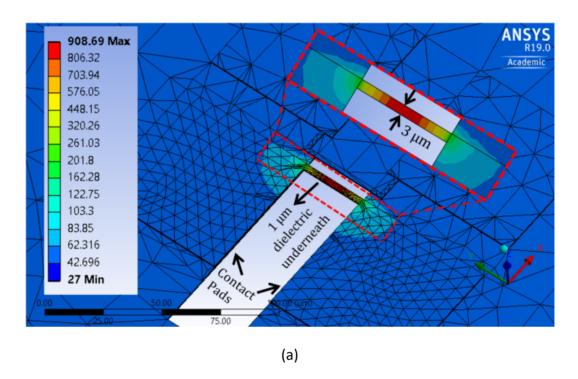

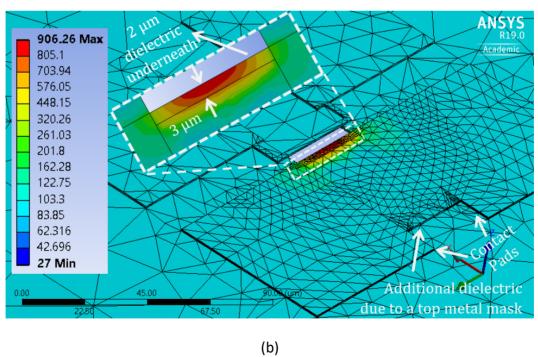

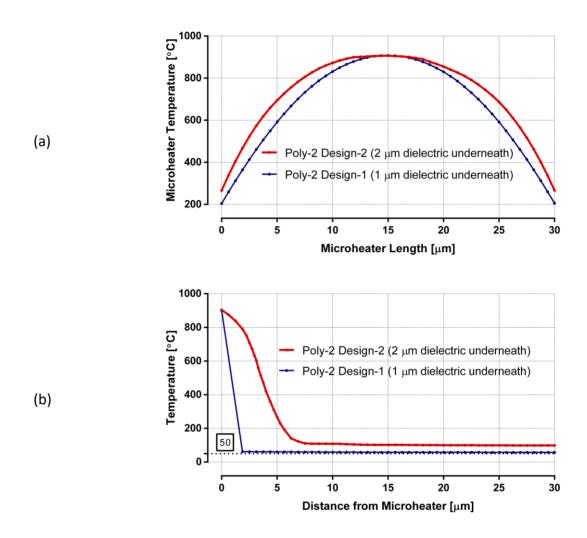

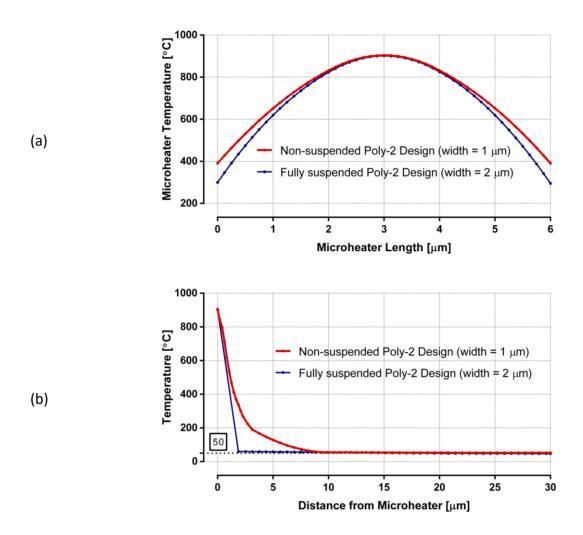

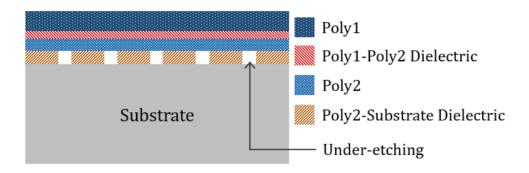

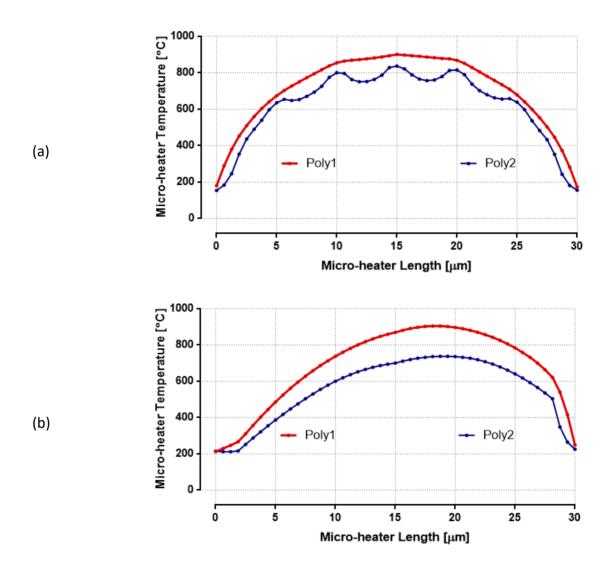

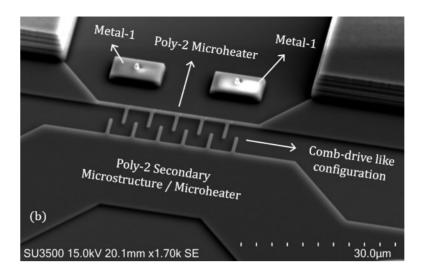

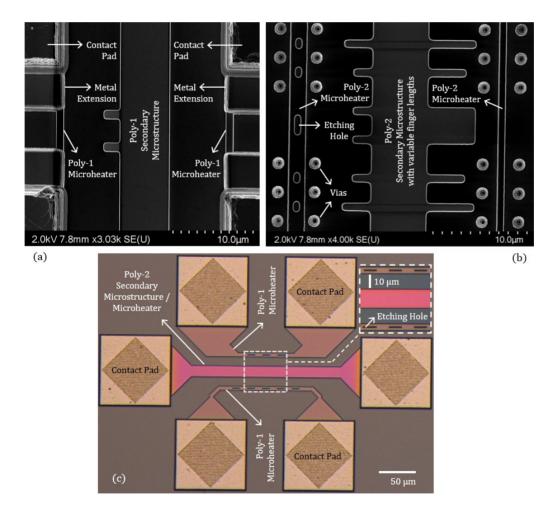

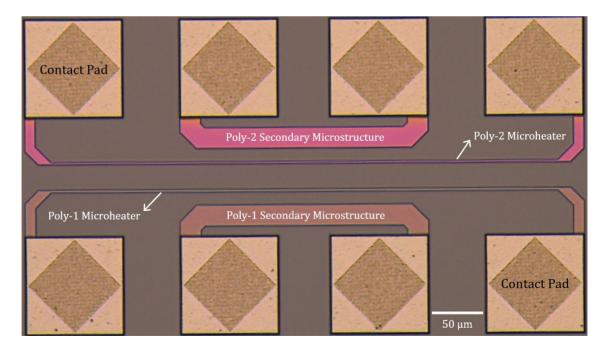

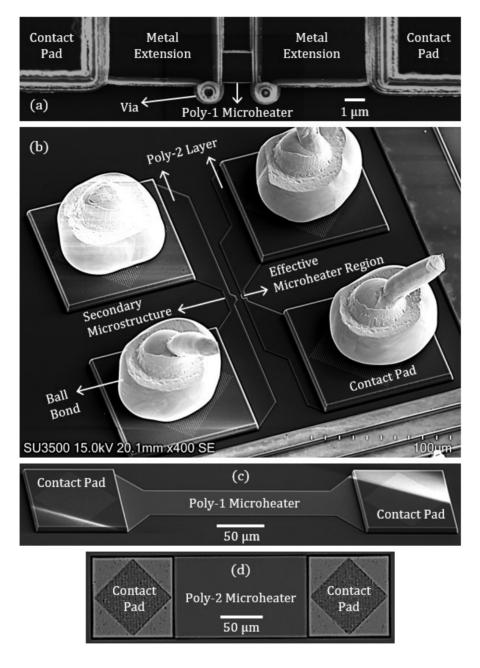

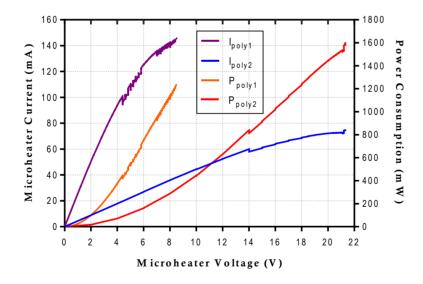

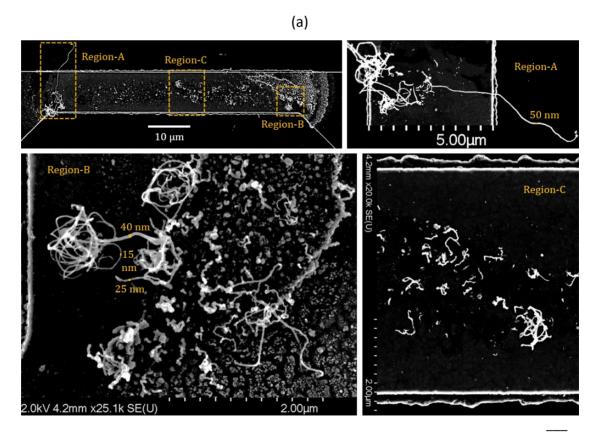

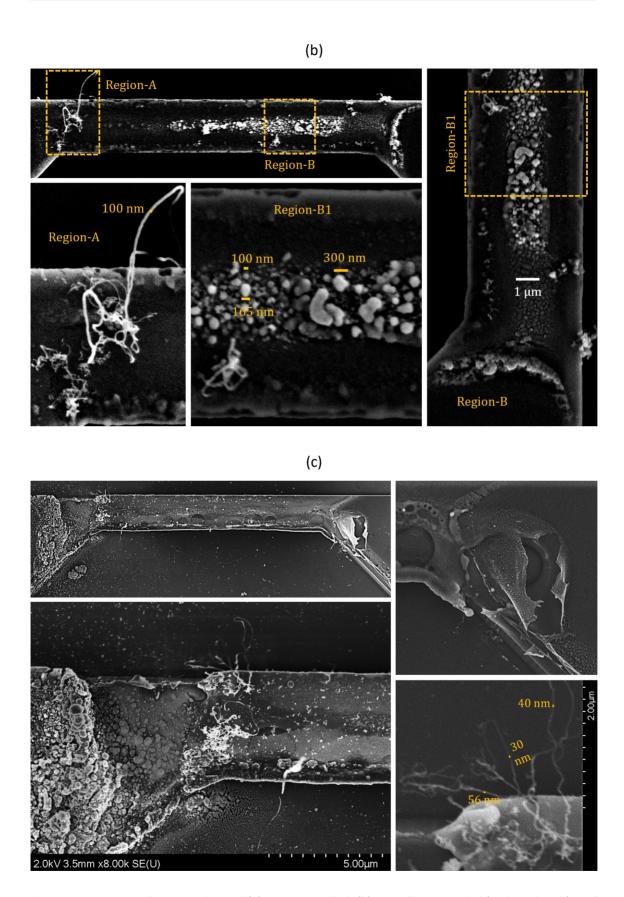

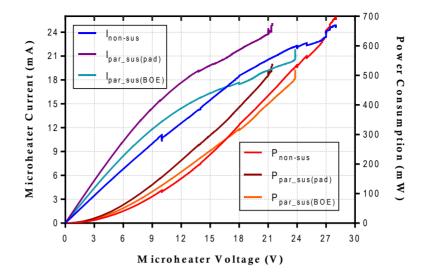

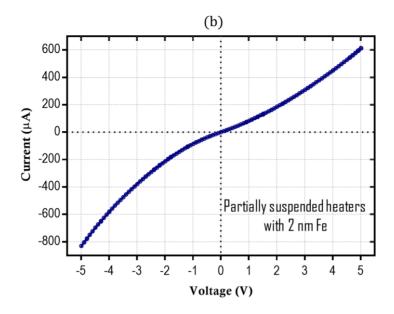

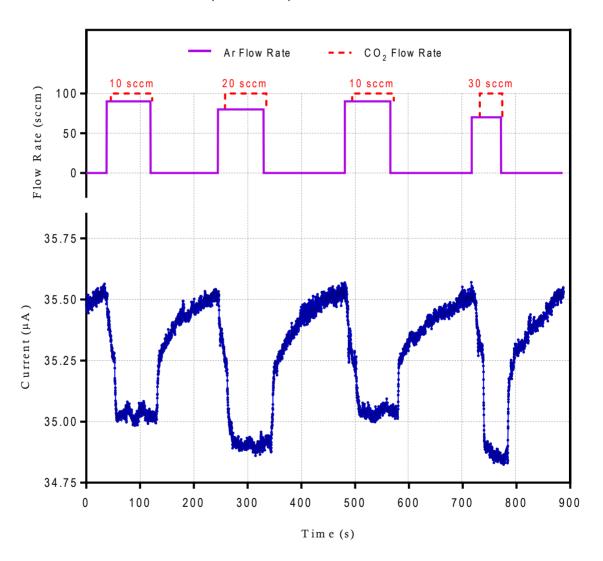

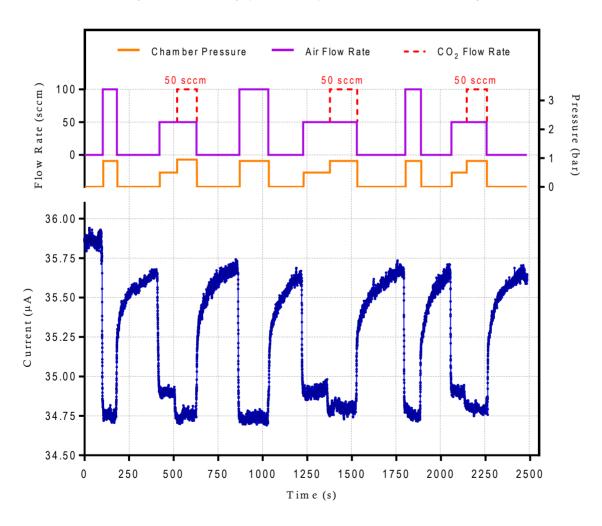

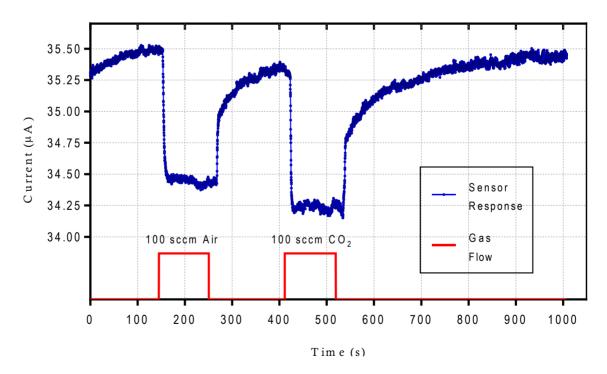

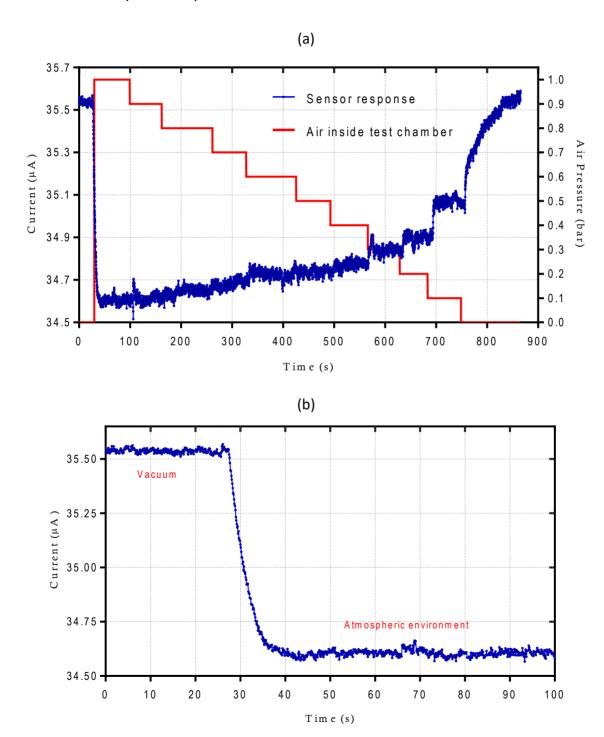

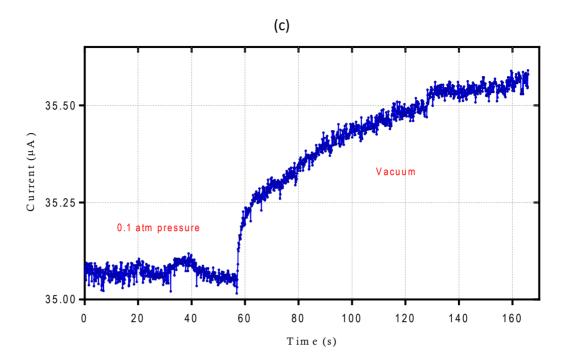

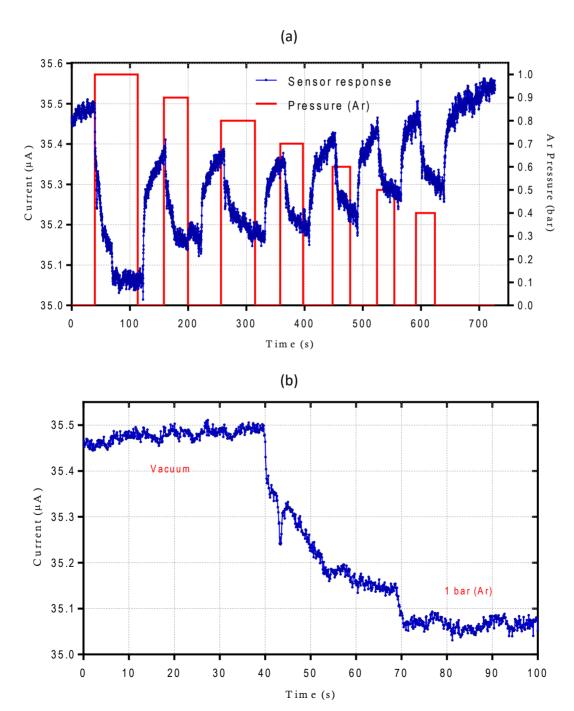

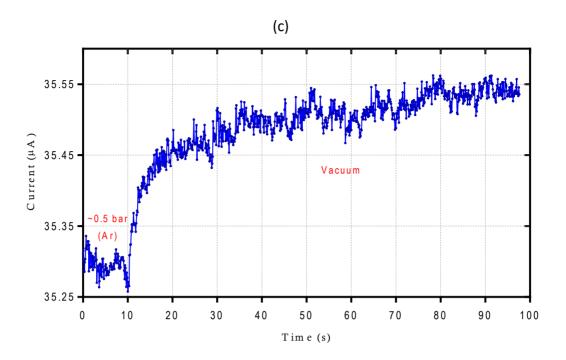

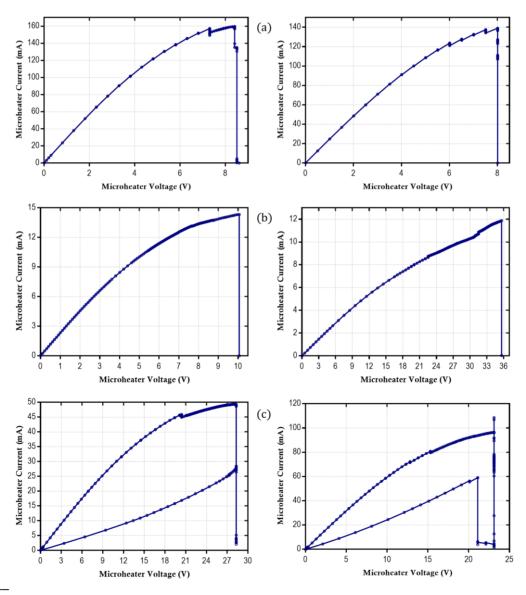

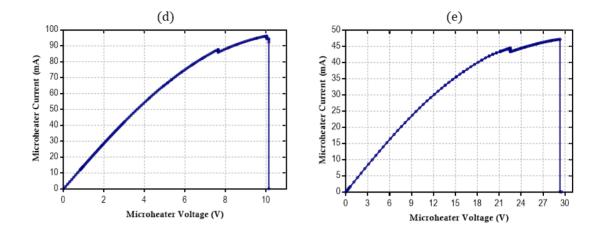

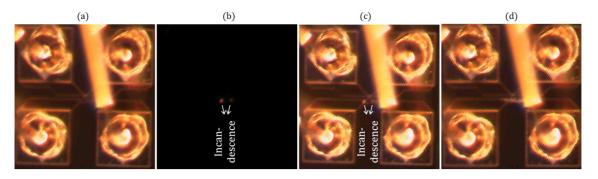

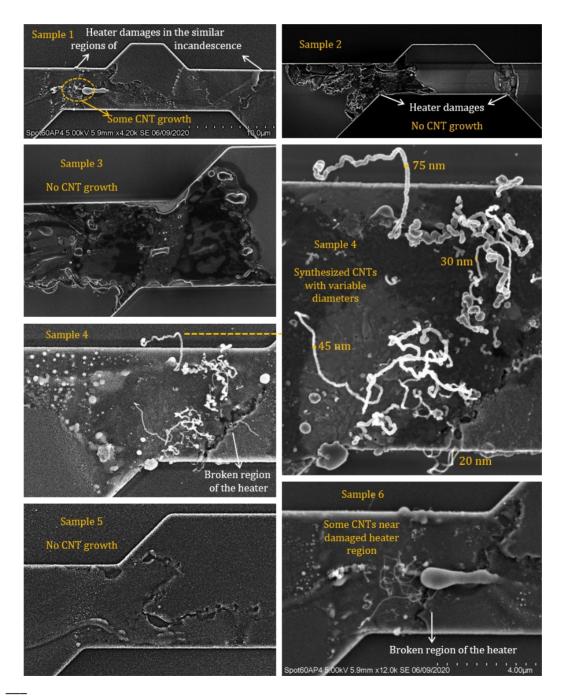

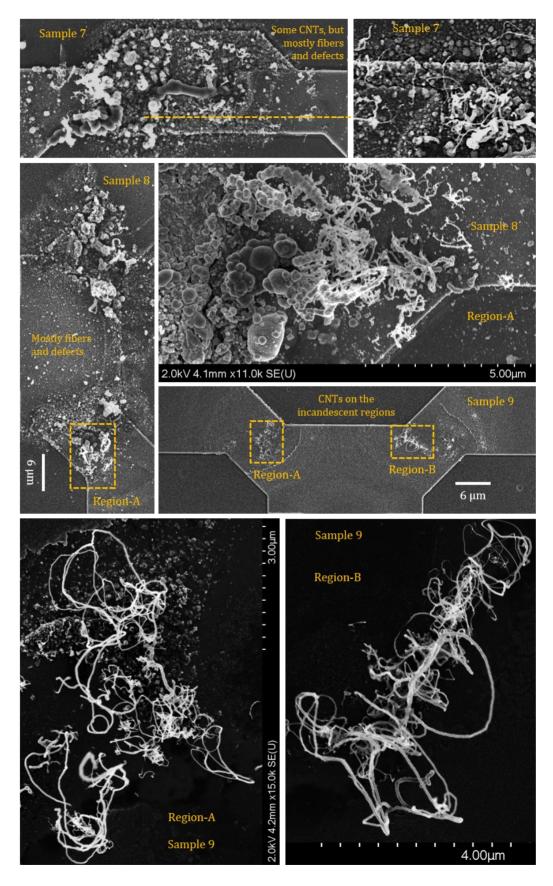

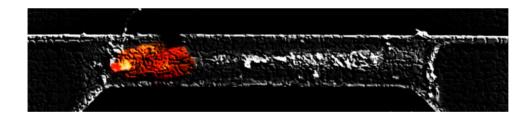

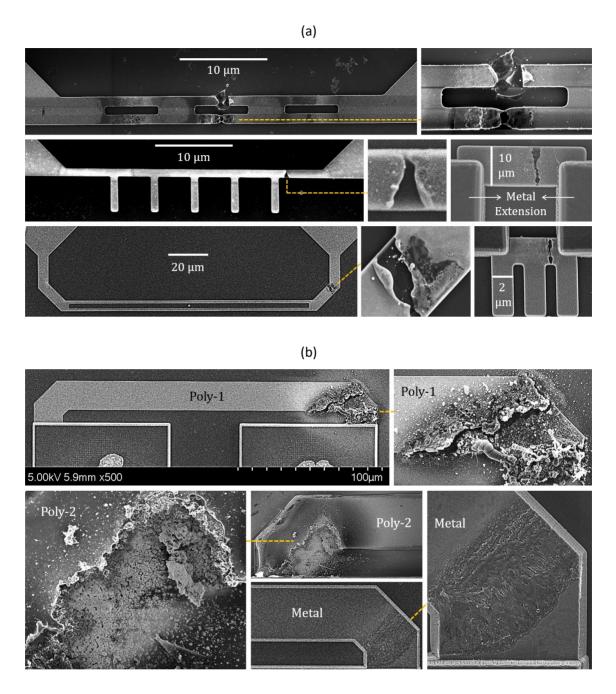

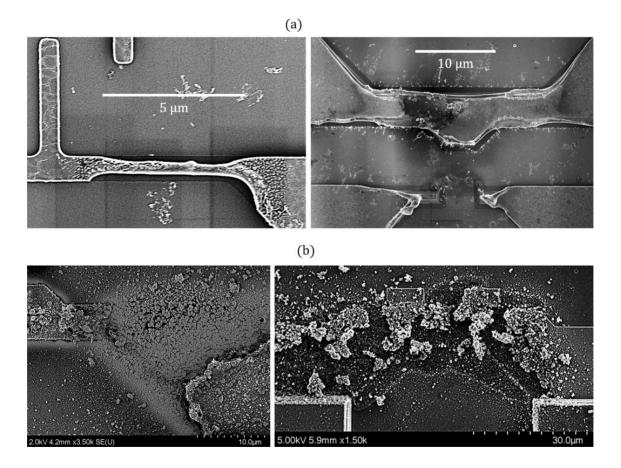

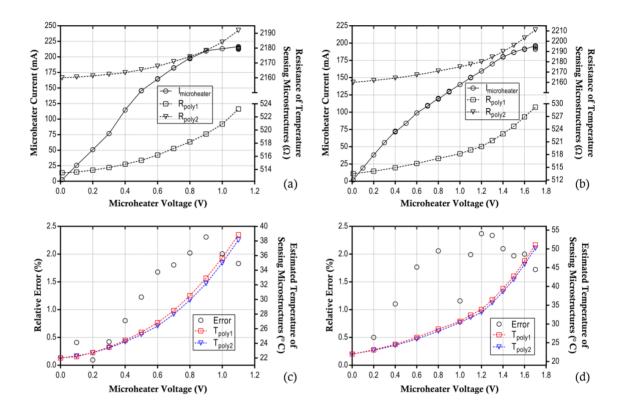

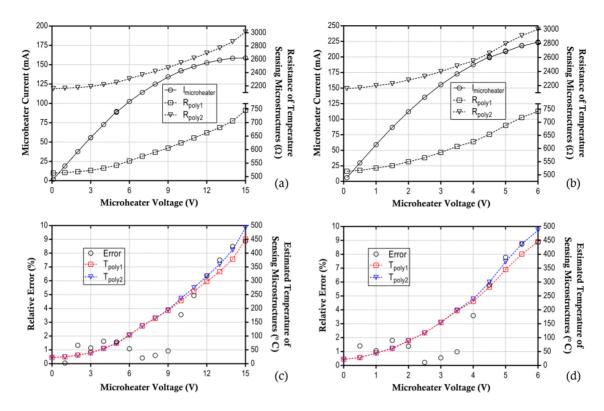

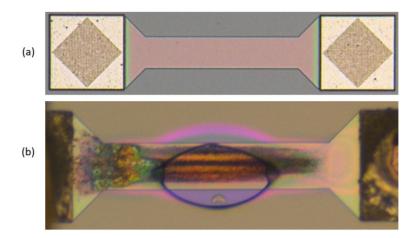

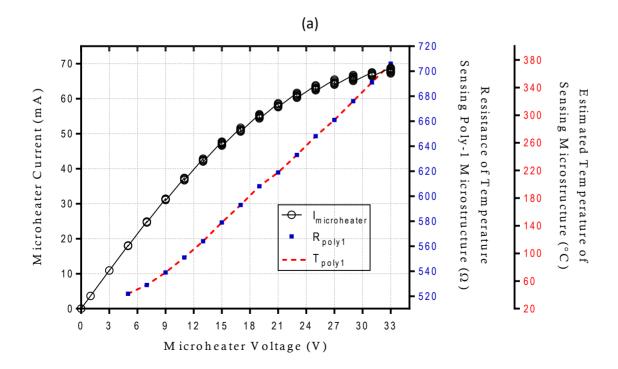

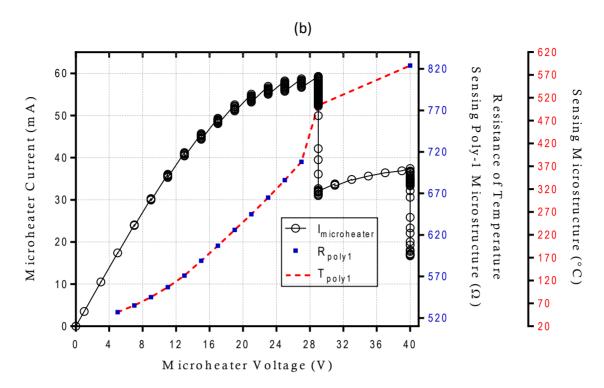

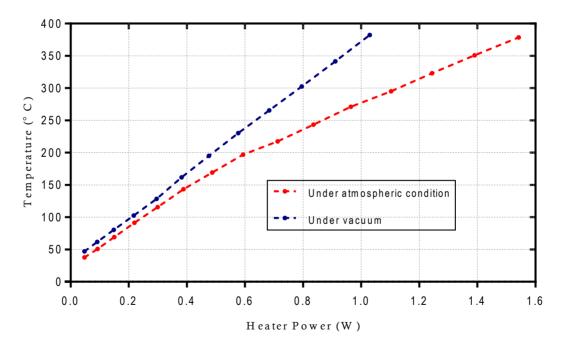

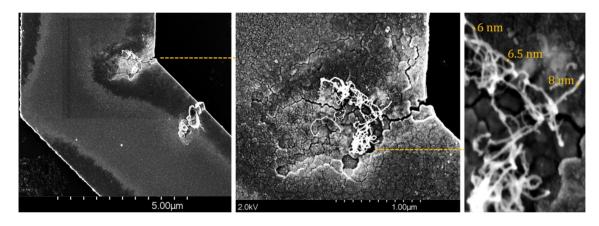

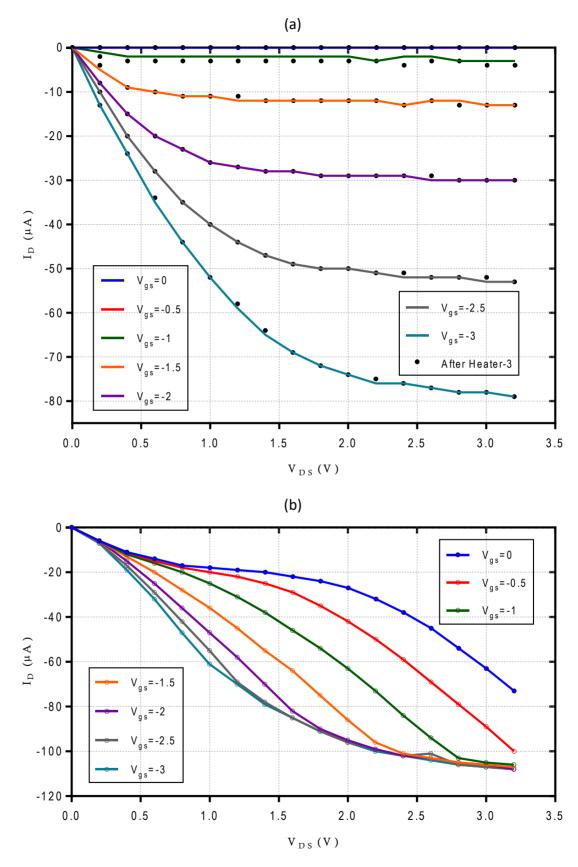

For a rectangular microheater, maximum temperature is generated at the centre of the heater and gradually reduces along its length. An expression for the maximum microheater temperature (T) can be derived by considering  $I_x = I/2 - x$ , where I is the total microheater length. For this condition, following expressions can be written: